Department of Electronics and Bio Medical Engineering

advertisement

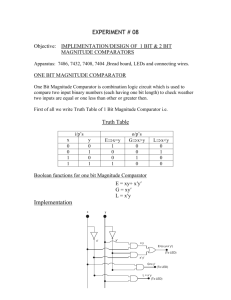

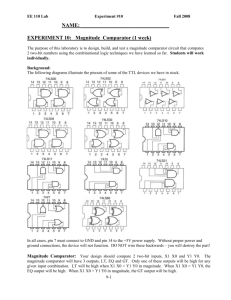

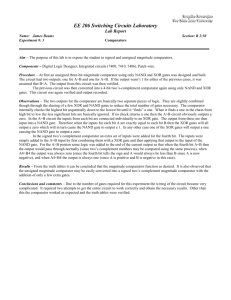

ISRA UNIVERSITY FACULTY OF ENGINEERING, SCIENCE & TECHNOLOGY Lab – 06 -1 Lab Experiment No.06 Name: _____________________________________________________ Roll No: ______________ Score:_________________ Signature:__________________________________ Date:___________ Designing of 1-Bit Magnitude Comparator PERFORMANCE OBJECTIVE: After the successful completion of this lab, students will be able to: Design & Synthesize of Magnitude Comparator using Xilinx ISE Software Simulation of Magnitude Comparator using ISIM Simulator. Implementation of Magnitude Comparator with NEXYS2 Spartan 3E Kit using Xilinx ISE & Adept Software. LAB REQUIREMENTS: PC with Windows XP/2007 Operating System. Xilinx ISE Design Suite 12.3 Software installed. Digilent Adept Software. NEXYS2 Spartan 3E Kit DISCUSSION: A comparator is a Combinational logic circuit that compares the two input binary numbers and signals if the two numbers are equal or if one is higher than other. The basic function of comparator is to compare the magnitude of two quantities to determine the relationship of those quantities. A binary comparator is usually has three outputs (A>B, A=B and A<B). A 1-Bit comparator compares the two one bit (A and B) and determine whether they are “Greater than”, “Less than” or “Equal to” each other by the high level on the appropriate output. The truth table and logic diagram of 1-bit magnitude comparator as shown in figure 5.1. A 0 B 0 A>B 0 A=B 1 A<B 0 0 1 0 0 1 1 0 1 0 0 1 1 0 1 0 A B 1-Bit Magnitude Comparator A>B A=B A<B Figure 5.1: Full Adder Truth Table, and Signal Block Designed By: Engr. Irshad Rahim Memon Department: Electrical Engineering . ISRA UNIVERSITY FACULTY OF ENGINEERING, SCIENCE & TECHNOLOGY Lab – 06 -2 DESIGNING PROCEDURE: STEP1: DESIGN ENTRY 1. Invoke Xilinx ISE Design Suite 12.3 Software. “Select File > New Project” 2. Enter the Project name mag_comp in the Name field. Verify that HDL is selected as the Top-Level Source Type, and click on NEXT again click on NEXT and Click on Finish. 3. Now Create a New Source file; Go to Project > New Source. Select VHDL Module and Enter the source file name mag_comp. Click on Next. Enter the Input and output Ports name and click NEXT and click Finish. VHDL Code for the Magnitude Comparator is library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity mag_comp is Port ( A : in STD_LOGIC; B : in STD_LOGIC; AGB : out STD_LOGIC; AEB : out STD_LOGIC; ALB : out STD_LOGIC); end mag_comp; architecture Behavioral of mag_comp is begin AGB <= A AND (NOT B); AEB <= A XOR B; ALB <= (NOT A) AND B; end Behavioral; Step 2: Simulation After Creating project and new Source File now it is ready to simulate the Design. To simulate the Magnitude Comparator follow the following steps. 1. In the Design Panel, select the Simulation radio button. 2. Select mag_comp Behavioral file and double click on Simulator Behavioral Model in the Process window. 3. Select the Simulation from the menu bar and click on Restart. 4. Force the input signal (A and B). 5. Select the Simulation from the menu bar and click on Run. It shows the following Simulation result of Magnitude Comparator. Figure: 5.3. Simulation Result for Magnitude Comparator Designed By: Engr. Irshad Rahim Memon Department: Electrical Engineering . ISRA UNIVERSITY FACULTY OF ENGINEERING, SCIENCE & TECHNOLOGY Lab – 06 -3 Step 3: Synthesis 1. To synthesize the design, double click on the Synthesize Design option in the Processes window. 2. Now the schematic diagram of the Magnitude comparator can be viewed by double clicking View RTL Schematic under Synthesize-XST menu in the Process Window, (Figure5.4). 3. Similarly you can view the Technology Schematic Symbol by double clicking View Technology Schematic under Synthesize-XST menu in the Process Window, (Figure 5.5). Fig: 5.5. Technology Schematic Symbol for Magnitude comparator Fig: 5.4. Schematic diagram for magnitude comparator Step 4: Implementation 1. Before implement the design you must create the User Constraint File UCF. 2. After creating the UCF file Single Click on mag_comp.ucf file from within Project Navigator, and then Select “Edit Constraints (Text)” from the Process window. 3. Assigning the pins to inputs and outputs of Magnitude comparator as following and save Ucf file. NET "A" LOC = G18; NET "B" LOC = H18; NET "AGB" LOC = J14; NET "AEB" LOC = J15; NET "ALB" LOC = K15; 4. After assigning the Pins double click on “Implement Design” option in the Processes window. It will go through steps like Translate, Map and Place & Route. Designed By: Engr. Irshad Rahim Memon Department: Electrical Engineering . ISRA UNIVERSITY FACULTY OF ENGINEERING, SCIENCE & TECHNOLOGY Lab – 06 5. -4 Now create a programming file (bit stream file) of the design. This is done by clicking once on your top-level design in the Sources Pane, followed by a double click on “Generate Programming File” in the process window. 6. Once the programming file (bit stream file) is generated, the file has to be downloaded to the NEXYS2 Spartan3E device, using Digilent Adept Software. Review Question Select NEXYS2 Spartan3E FPGA design the 4-Bit Magnitude Comparator. Final Assignment : 1. What is Comparator? 2. Simulate “4-Bit and 8-Bit Magnitude Comparator” and Attach simulation Result. 3. Designed the 4-Bit and 8-Bit Magnitude Comparator , perform Synthesis Process and attach the Schematic diagram and Technology Schematic Symbol. Designed By: Engr. Irshad Rahim Memon Department: Electrical Engineering .