Comparator Circuits Lab Report - Ohio State University

advertisement

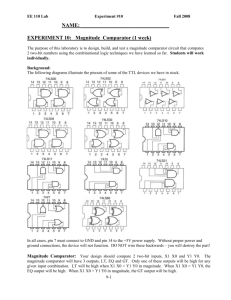

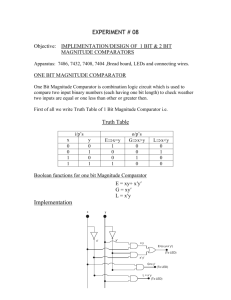

D Deeeeppiikkaa D Deevvaarraajjaann TThhee O Ohhiioo SSttaattee U Unniivveerrssiittyy EE 206 Switching Circuits Laboratory Lab Report Name: James Beams Experiment #: 3 Section: R 2:30 Comparators Aim – The purpose of this lab is to expose the student to signed and unsigned magnitude comparators. Components – Digital Logic Designer, Integrated circuits (7400, 7410, 7486), Patch wire. Procedure – At first an unsigned three-bit magnitude comparator using only NAND and XOR gates was designed and built. The circuit had two outputs: one for A>B and one for A+B. If the output wasn’t 1 for either of the previous cases, it was assumed that B<A. The output from this circuit was then verified. The previous circuit was then converted into a 4-bit two’s-complement comparator again using only NAND and XOR gates. This circuit was again verified and output recorded. Observations – The two outputs for the comparator are basically two separate pieces of logic. They are slightly combined though through the sharing of a few XOR and NAND gates to reduce the total number of gates necessary. The comparator internally checks the highest bit sequentially down to the lowest bit until it “finds” a one. When it finds a one in the chain from high bit to low the less significant bits are basically ignored. If no check returns a one then the A>B circuit obviously outputs a zero. In the A=B circuit the inputs from each bit are connected individually to an XOR gate. The output from these are then input into a NAND gate. Therefore when the inputs for each bit A are exactly equal to each bit B then the XOR gates will all output a zero which will in turn cause the NAND gate to output a 1. In any other case one of the XOR gates will output a one causing the NAND gate to output a zero. In the signed two’s complement comparator an extra set of inputs were added for the fourth bit. The inputs were simply added to the A=B input by first combining them with a XOR gate and then applying that output to the input of the NAND gate. For the A>B portion some logic was added to the end of the current output so that when the fourth bit A=B then the output would pass through normally (since two’s complement numbers may be compared using the same process), when A4>B4 the output was always zero (since the fourth bit tells the sign and A would always be less than B since A is now negative), and when A4<B4 the output is always one (since A is positive and B is negative in this case). Results – From the truth tables it can be concluded that the magnitude comparators function as desired. It is also observed that the unsigned magnitude comparator may be easily converted into a signed two’s-complement magnitude comparator with the addition of only a few extra gates. Conclusions and comments – Due to the number of gates required for this experiment the wiring of the circuit became very complicated. It required two attempts to get the entire circuit to work correctly and obtain the necessary results. Other than this the comparator worked as expected and the truth tables were verified. D Deeeeppiikkaa D Deevvaarraajjaann TThhee O Ohhiioo SSttaattee U Unniivveerrssiittyy Fig. 1: 3-bit Magnitude Comparator A2 1 3 B2 2 A2 1 B2 A1 B1 A1 B1 A0 B0 13 3 2 11 12 4 2 4 6 5 10 4 8 9 B0 9 A>B 3 5 A0 6 1 6 10 3 4 5 1 2 13 12 11 10 9 8 6 5 8 10 9 8 A=B D Deeeeppiikkaa D Deevvaarraajjaann TThhee O Ohhiioo SSttaattee U Unniivveerrssiittyy Fig 2: 4-bit signed 2’s complement comparator A3 1 B3 2 A2 3 1 B2 2 A2 1 B2 A1 B1 A1 B1 A0 B0 13 2 11 12 4 A>B 6 4 6 5 3 5 2 4 6 5 10 4 8 9 1 2 13 12 11 10 9 8 6 5 8 9 12 3 4 5 1 6 A3 13 B3 8 9 3 A0 10 B0 10 3 11 10 9 8 13 13 11 12 11 12 A=B D Deeeeppiikkaa D Deevvaarraajjaann TThhee O Ohhiioo SSttaattee U Unniivveerrssiittyy Three 2-bit number comparator with seven outputs A0 B0 A1 B1 A0 A=B=C C0 A1 C1 A1 B1 A>B A>B,C A0 B>A,C B0 A1 C1 A>C A0 C>B,A A<B,C C0 B1 C1 B<A,C B>C C<A,B B0 C0 Numbers in signed magnitude representation cannot be used with the magnitude comparators built in the experiment since only the sign bit is being changed to indicated the sign of the number (1111 in signed magnitude is the same as 1000 in two’s compliment =-7). For the magnitude comparators built in the experiment to work correctly the output must be complimented when the signed bit is one. Otherwise the comparator would treat the other bits as it would a positive number and always display the incorrect output (except when the numbers are equal).