EXPERIMENT # 08

advertisement

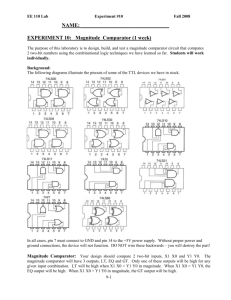

EXPERIMENT # 08 Objective: IMPLEMENTATION/DESIGN OF 1 BIT & 2 BIT MAGNITUDE COMPARATORS Apparatus: 7486, 7432, 7408, 7404 ,Bread board, LEDs and connecting wires. ONE BIT MAGNITUDE COMPARATOR One Bit Magnitude Comparator is combination logic circuit which is used to compare two input binary numbers (each having one bit length) to check weather two inputs are equal or one less than other or greater then. First of all we write Truth Table of 1 Bit Magnitude Comparator i.e. Truth Table i/p’s x 0 0 1 1 y 0 1 0 1 Ex=y 1 0 0 1 o/p’s Gx>y 0 0 1 0 Lx<y 0 1 0 0 Boolean functions for one bit Magnitude Comparator E = xy+ x′y′ G = xy′ L = x′y Implementation x y x' y' xy E=(x y+x' y') (To LED) x' y' G=x y' (To LED) L = x' y (To LED) To check this logic circuit, we shall use the above Truth Table 2 BIT MAGNITUDE COMPARATOR Two Bit Magnitude Comparator which is used to compare two input binary numbers (each having bit length of two ) to check weather two inputs are equal or one less than other or greater then. USING XOR GATES AND BASIC LOGIC GATES First of all we write Truth Table of 2 Bit magnitude Comparator. Truth Table i/p’s A A1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 o/p’s B A0 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 B1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 B0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 EA=B 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1 GA>B 0 0 0 0 1 0 0 0 1 1 0 0 1 1 1 0 LA<B 0 1 1 1 0 0 1 1 0 0 0 1 0 0 0 0 Now we simplify outputs of 2 Bit Magnitude Comparator by k-map technique. k-map’s for outputs of 2 Bit Magnitude Comparator. k-map of “E”. E B1B0 A1 A0 00 01 11 10 00 1 01 11 10 1 1 1 k-map of “G” G B1B0 A1A0 00 01 11 10 00 01 1 1 1 1 1 11 10 1 k-map of “L”. L B1B0 A1 A0 00 00 01 11 10 01 1 11 1 1 10 1 1 1 Boolean Functions Now writing Boolean functions from above k-maps for outputs of two Bit Magnitude Comparator, we get. E = A1 A0 B1 B0+ A1 A0 B1 B0+ A1 A0 B1 B0+ A1 A0 B1 B0 E= A1 B1(A0 B0+ A0 B0) + A1 B1(A0 B0+ A0 B0) E = (A0 B0+ A0 B0) (A1 B1+ A1 B1) E = (A0 + B0)'(A1 + B1)' G = A1B1+ A1 A0 B1 B0+ A1 A0 B1 B0 G = A1B1 + A0 B0 (A1B1+ A1 B1) G = A1B'1 + A0B'0 (A1 + B1)' L = A1B1 + A0 B0 (A1B1+ A1 B1) L = A'1B1 + A'0B0 (A1 + B1)' Implementation A1 A0 B1 B0 E = (A0 + B0) (A1 + B1) (To LED) G = A1B'1 + A0B'0 (A1 + B1)' (To LED) L = A'1B1 + A'0B0 (A1 + B1)' (To LED) We check this circuit by Truth Table of 2 Bit Magnitude Comparator as written before.