Lab - 02 - 4th Semester Notes

advertisement

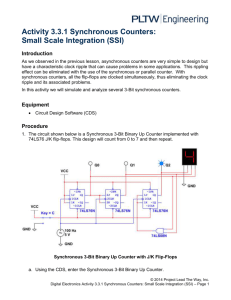

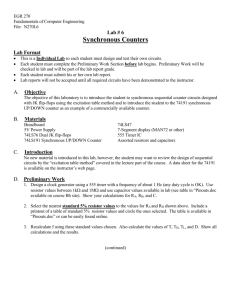

LAB NO.02 Objective: Design 2-bit mod 4 synchronous counter, 2-bit mod 3 synchronous counter and 3-bit mod 8 synchronous counter using IC-7476 with master slave JK flip-flop and AND gate. Equipment: 1 Logic probe 1 Proto board 1 Set of wires 2 -7476 ICs with dual JK flip-flop 1 7408 AND Gate Theory: A synchronous counter, in contrast to an asynchronous counter, is one whose output bits change state simultaneously, with no ripple. The only way we can build such a counter circuit from J-K flip-flops is to connect all the clock inputs together, so that each and every flip-flop receives the exact same clock pulse at the exact same time. A simple way of implementing the logic for each bit of an ascending counter (which is what is depicted in the image to the right) is for each bit to toggle when all of the less significant bits are at a logic high state. Circuit Layout: 4 Pin Layout: 7476 IC Pin Configuration Observations: Truth Table for 2-Bit Mod 4 synchronous Counter 5 Clock pulse Q2 Q1 0 1 2 3 4(recycles) 0 0 Truth Table for 2-Bit Mod 3 synchronous Counter Clock pulse Q2 Q1 0 1 2 3(recycles) 0 0 Truth Table for 3-Bit Mod 8 synchronous Counter Clock pulse 0 1 2 3 4 5 6 7 8(recycles) Q3 Q2 Q1 0 0 0 Conclusion: This synchronous circuit may show the result according to its pin configuration and its truth table is verified as proceed. 6