Review-problems

advertisement

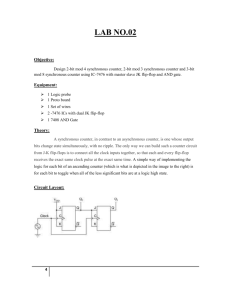

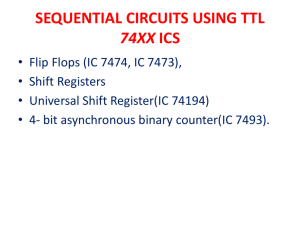

CS207-Spring 01 Computer Science & Engineering December, 2001 Digital Logic Design K. YETONGNON UTEB 352 Selected Review questions This problem set includes several exercises to help you study materials not covered by the first two exams. If you have any questions, send me an email (kokou@engr.uconn.edu). Good luck on your review. Solutions Important : Review all problems and questions from Exam1, Exam2 and the first set of review questions ( the one you use to review for exam2). The Final exam is cumulative (it covers materials from homeworks, project and previous exams). 50% of the exam will be devoted simple class note questions (these question can easily be answered if you review all class material (homeworks, project, previous exams). A.State diagrams Exercise 1 Draw a state diagram for a mealy type state machine specified as follows: - Denote "a" the initial state of the machine - set the initial output to the initial input (the input is presented to the machine bit by bit) - The output changes value only when three successive inputs have the same value and that value is opposite to the current output. For example, if the current output is 1 and the machine detects three consecutive 0 it changes the output to 0. Repeat the above for a Moore type machine. Answer: Starting from an initial 0 input the sequence detector works as follows. S0 is the initial state. If the current output is 0, we will change the output to 1 if we detect 3 consecutive 1's. This is handled by states S1, S2 and S3. In S1 we wait for a 1 to move to state S2, where we are looking for a second 1. If we get 0, we go back to S1 and start all over and if we get a 1, we go to S3. In S3 we wait for the final third 1. If we get 0 instead, we go to S1 to start all over and if get 1, we go to a state where we are reading to detect an output change from 1 to 0. Detecting 3 consecutive 0 to change the output from 1 to 0 is symmetrical to what we have just done. This is handled by states S1', S2' and S3'. S0 0/0 1/1 1/1 0/1 0/0 S1 S1’ 1/0 0/0 1/1 0/1 0/0 S2 1/1 S2’ 0/1 1/0 S3 1/1 0/0 S3’ Now you can adapt this solution to derive a state diagram for a Moore state machine. Exercise 2 Draw a state diagram for a 3 bit UP/Down counter specified as. The counter has a an input U that determines the direction of the generated count sequence. When the control input U=1, the counter counts up in the sequence 0,1,2,3,4,5,6,7. When U=0, the counter counts down in the sequence 0,7,6,5,4,3,2,1 Anwer: This exercise is quite easy, but you should note that there is no specific output. The transitions are labelled with the input values (0 to count down and 1 to count up). The state diagram is given by: 1 1 1 1 0 0 1 1 2 0 4 3 0 1 0 1 5 0 1 6 0 7 0 0 A.Analysis of clocked synchronous state machine Exercises Problem 7.17 on page 648 of text. Problem 7.18 on page 648 of text. Problem 7.19 on page 649 of text. Answer: These problems are similar to the discussion in the text book. Review the analysis sections in your book. These problems are similar to the discussion in the text. B.Design of clocked synchronous machine Answer: Exercise 1 and 2 are straightforward. Go over the design steps given in text and your class notes. The solutions are very similar. Exercise 1 Problem 7.32 Problem 7.34 page 651 of text Problem 7.35 page 651 of text Exercise 2 Study the design examples (there are two examples, study both) given in 7.4.6 on page 580 of text. Solve the same examples using J-K flip flops. Exercise 3 a) Design a Mealy sequence detector for the sequence 1010 (overlapping is allowed) First, note that overlapping means that part of a "1010" sequence can be including in the next "1010" sequence, thus if the input is "101010" then the sequence is detected twice. 0/0 1/0 0/0 b a 1/0 c 1/0 0/0 d 0/1 1/0 State descriptions are as follows: state a is the initial state, in state b we have received a 1 and we are waiting for "010", in state c we are waiting for "10" and finally we go to state d to wait for a 0 to output 1. Note that when we output 1 we go to state c to wait for an overlapping sequence. Determine the state/output table Answer: Current state q a b c d Next State Q Input 0 1 a b c a a d c a Output Input 0 0 0 0 1 1 0 0 0 0 There are 4 states, so we need 2 bits (q1q0) to encode them. The state assignment is as follows: a=00, b=01, c=10, d=11. Current state q1q0 a b c d 00 01 10 11 Next State Q1Q0 Input 0 1 00 01 10 00 00 11 10 00 Output Input 0 1 0 0 0 1 0 0 0 0 For D flip flop the excitation input to obtain a next state Q=d (0 or 1) is d. So the flip flop excitation table is the same as the next state table above. So the excitation inputs , D1+, D0+ are given by: Current state q1q0 a b c d 00 01 10 11 Next State D1+ D0+ Input 0 1 00 01 10 00 00 11 10 00 From the above excitation map and using a K-Map, we can derive the excitation equations of the flip flop: D1+ = q0I' + q1q0'I D2+ = q1q0'I Draw the corresponding sequential circuit. Now starting from the excitation, you can repeat the derivation of the excitation equations for JK flip flops. b) Design a Mealy sequence detector for the sequence 110 (no overlapping) The state diagram is composed of the following states. State a is the initial state. In state b a 1 is detected and we are expecting a "10". In state c, the sequence "11" has been detected. From c, if the input is 1 we are done (so output a 1 and go to state 0), if the input is "1" stay in c to wait for a 0. 1/0 0/0 1/0 1/0 b a c 0/0 0/1 C.Counters and Registers Exercise 1 a) Design a synchronous 3-bit binary counter with JK flip-flops. b) Design a synchronous 4-bit counter with D flip-flops c) Design a 3-bit counter that generates the sequence (in decimal) 0,4,6,7,3,1,5 The above problem are classical sequential circuit design. Review your class notes and apply them to the problems. Exercise 2 a) Design a 4-bit parallel in / parallel out register using D flip-flops Answer: this problem is given in the practice exam. The design is as follows: I3 D Enable Clock I2 D3 Q C Q’ Q3 D I1 D2 Q C Q’ Q2 D I0 D1 Q Q C ’ D D0 Q Q C ’ Q1 Q0 b) Repeat a) using JK flip-flops c) Design a parallel in / serial out right-shift register using And and Or gates and edgetriggered D flip-flops Exercise 3 Design a device that generates the sequence 1,2,4 and 8 over and over again. a) use a shift register to design the device This problem was discussed in class. Load 4 bits (0001) in the register. To generate the sequence, shift the register left and load a 0 in the least significant bit of the register. At each clock pulse, shift the register left to generate the sequence. I3 D Enable Clock D3 Q C Q’ Q3 I1 I2 D D2 Q C Q’ Q2 D D1 Q C Q’ Q1 D D0 Q 0 C Q’ Q0 b) design the device as a counter using D flip-flops. Yet another classical sequential design. So apply the design steps discussed in class.