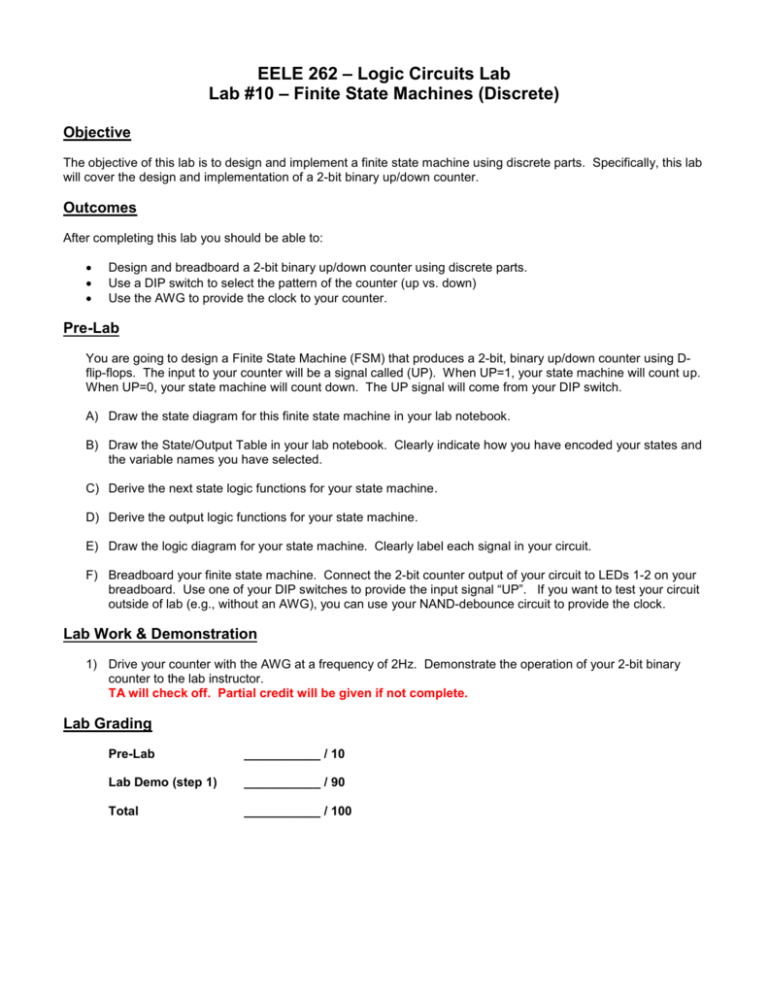

Lab #10 – Finite State Machines (Discrete)

advertisement

EELE 262 – Logic Circuits Lab Lab #10 – Finite State Machines (Discrete) Objective The objective of this lab is to design and implement a finite state machine using discrete parts. Specifically, this lab will cover the design and implementation of a 2-bit binary up/down counter. Outcomes After completing this lab you should be able to: Design and breadboard a 2-bit binary up/down counter using discrete parts. Use a DIP switch to select the pattern of the counter (up vs. down) Use the AWG to provide the clock to your counter. Pre-Lab You are going to design a Finite State Machine (FSM) that produces a 2-bit, binary up/down counter using Dflip-flops. The input to your counter will be a signal called (UP). When UP=1, your state machine will count up. When UP=0, your state machine will count down. The UP signal will come from your DIP switch. A) Draw the state diagram for this finite state machine in your lab notebook. B) Draw the State/Output Table in your lab notebook. Clearly indicate how you have encoded your states and the variable names you have selected. C) Derive the next state logic functions for your state machine. D) Derive the output logic functions for your state machine. E) Draw the logic diagram for your state machine. Clearly label each signal in your circuit. F) Breadboard your finite state machine. Connect the 2-bit counter output of your circuit to LEDs 1-2 on your breadboard. Use one of your DIP switches to provide the input signal “UP”. If you want to test your circuit outside of lab (e.g., without an AWG), you can use your NAND-debounce circuit to provide the clock. Lab Work & Demonstration 1) Drive your counter with the AWG at a frequency of 2Hz. Demonstrate the operation of your 2-bit binary counter to the lab instructor. TA will check off. Partial credit will be given if not complete. Lab Grading Pre-Lab ___________ / 10 Lab Demo (step 1) ___________ / 90 Total ___________ / 100