Investigation of High-Speed Optoelectronic Receivers in SiGe

advertisement

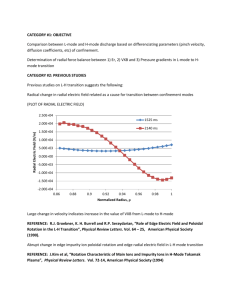

Research on Investigation of High-Speed Optoelectronic Receivers in SiGe Principle Investigators: Funding: Steven P. Levitan and Donald M. Chiraulli Pittsburgh Digital Greenhouse The goal of this research is to investigate SiGe technology for the implementation of high speed photoreceivers. One of the tasks in this project was to use NeoCircuit and NeoCell tools from Neolinear Inc. (now part of Cadence Design Systems Inc.) to optimize circuits based on SiGe Bi-CMOS for optical receivers. The project flow, which used tools from both Cadence and Neolinear is illustrated below. Circuit architectures for multi-stage high-speed photo receivers were designed. For each sub-circuit, circuit design and optimization was performed by utilizing state of the art tools from Neolinear and Cadence. Final layout for the cell was also performed by utilizing tools from Neolinear and Cadence Design Systems. Figure 1: Overall Project Flow Figure 2: Tool Flow Design Flow: Tools Project Flow Identify SiGe photodiode/phototransistor topologies in IBM SiGe process Choose key sub-circuits for receiver design Neo Constraint editor Cadence Framework NeoCircuit Virtuoso XL Schematic Composer Import Investigation of SiGe based high speed receiver circuits NeoCircuit Editor Export NeoCell Layout Editor Neolinear Neo Configuration Spectre RF NeoCell Analysis, simulation and optimization of circuits at University of Pittsburgh Fabricate through MOSIS NeoCell Auto Place and Route Test receiver configuration Fabrication Figure 3: Example Sub-Circuit Layout Two Stage Differential Amplifier Figure 4: TIA Simulation and Testing Transimpedance Amplifier Simulation and Test Results TIA Circuit Topology Simulation 2.00E+00 4.00E-01 1.80E+00 2.00E-01 1.60E+00 -2.00E-08 0.00E+00 0.00E+00 2.00E-08 4.00E-08 6.00E-08 8.00E-08 1.00E-07 1.20E-07 1.40E+00 -2.00E-01 1.20E+00 -4.00E-01 1.00E+00 -6.00E-01 8.00E-01 -8.00E-01 6.00E-01 4.00E-01 Cascaded Differential Amplifier Layout - Auto Place & Route -1.00E+00 2.00E-01 -2.00E-08 0.00E+00 0.00E+00 -1.20E+00 2.00E-08 4.00E-08 6.00E-08 Input 8.00E-08 1.00E-07 1.20E-07 -1.40E+00 1000Ms/S Output 1. “Design and Fabrication of SiGe Photo-Detectors in the IBM 5HP Process,” Leo Selavo, Amit Gupta, Donald M. Chiarulli, Steven P. Levitan (poster) Optics in Computing (OC 2004), Engelberg, Switzerland, April 21-23, 2004. 2. “High-Speed Optoelectronics Receivers in SiGe,” Amit Gupta, Steven P. Levitan, Leo Selavo, Donald M. Chiarulli, (Design Contest, 2nd Place) 17th International Conference on VLSI Design 2004 (VLSI 2004), pp. 957-960, Mumbai, India, January 5-9, 2004. 3. 3rd Place 2004 DAC/ISSCC Student Design Contest – SiGe Prototype Chip Design Implementing CMOS Fixed Bit-Load Drivers and Receivers for Next Generation High-Speed Board-Level Interconnect Jason D. Bakos, Amit Gupta, Leo Salavo, Donald Chiarulli – University of Pittsburgh, Pittsburgh, PA