sampleECO - UCSB Computer Science

advertisement

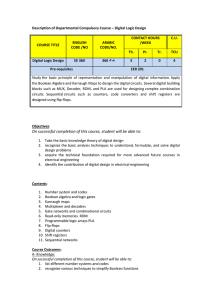

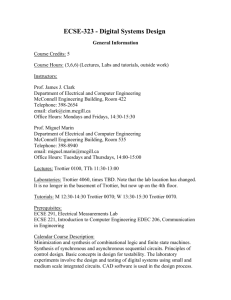

CPE/CSC/EE/SE Programs Course Syllabus EE/CPE 129: Logic and Switching Circuits (3 credits) Prepared by: Sandige, Richard S. DePiero, Fred W. (Updated by Dan Stearns for discussion purposes, Sept 13, 2007) Course Description: (2007-2009 Catalog) Modulo-N arithmetic and digital coding techniques. Fundamentals of Boolean algebra and minimization techniques. Two-level logic realizations of SOP and POS functions, and an introduction to multi-level logic. Multiple function synthesis using PLDs and gate arrays. Combinational circuit design as it applies to computers. Sequential circuit elements, flip-flops, counters and shift-registers. 3 lectures. Required/Elective: Required CPE CS EE x x x SE Elective Prerequisite Courses: Prerequisites by Topic: Textbook: (and/or other required material) References: Course Coordinator: URL (if any) Prerequisite: CPE 101 or CSC 234. Concurrent: CPE 169. Material covered in CSC 101: Ability to follow a software algorithm, and basic experience in a programming language. Digital Design Essentials, Richard S. Sandige, Prentice-Hall, 2002. 1. Data book information such as the TI (Texas Instruments) data book available on the following web site: http://www.ti.com. 2. Xilinx Foundation Series Software, available on CD ROM with specified textbook. Sandige, Richard Course Goals/Learning Outcomes/Performance Criteria (For EAC programs, performance Criteria for all courses are listed in <<a separate document.>>.) This course will give the student a background in, and help them understand the concepts of combinational and basic sequential logic circuit design. Computer architecture and subsystems will be used as the context to present the concepts to be learned in the course. It will give the student experience in the art of design and logical thinking. After completing the course, the student will be able to: 1. Convert numbers to different number systems (decimal, binary, octal, and hexadecimal), add and subtract signed and unsigned numbers in the binary number system, and work with different binary codes. 2. Minimize Boolean algebraic functions via Boolean algebra, and K-maps. 3. Analyze and design combinational logic circuits that use: (a) gate level logic; (b) Decoders; (c) Multiplexers; and (d) programmable logic devices (PLDs). 4. Analyze and design adder circuits and arithmetic logic units 5. Analyze and design basic feedback circuits such as latches and flip-flops. 6. Analyze and design basic synchronous sequential logic circuits (counters and controllers). Course Assessment Methods Graded homework, midterm exam and final exam Relationship of Course to EAC Program Outcomes (H=high, M=medium, L=low, N=none; n/a=not applicable) CPE EE SE a b c d e f g h i j k M M n/a L L n/a M M n/a N N n/a M M n/a L L n/a M M n/a L L n/a M M n/a M M n/a M M n/a Major Topics Covered: (number of hours each) 1. Computer/digital building blocks. (0.5) 2. Decimal, binary, octal, and hex number systems, conversions; signed number representations (sign magnitude, diminished radix complement, and radix complement representations); addition and subtraction of binary numbers; and bit patterns and codes. (2.5) 3. Boolean algebra; minimization of Boolean expressions; and basic logic gates. (2) 4. SOP and POS forms of functions and their realizations; different logic representations; and additional graphic symbols. (2) 5. Analyzing and designing combinational relay and IC logic circuits. (1) 6. Karnaugh maps; compressed truth tables; compressed K-maps using map-entered variables. (2) 7. Hazards, glitches, and glitch removal. (0.5) 8. Introduction to Decoders and Multiplexers; designing with Decoders and Multiplexers. (2) 9. PLD architectures (PROM, PLA, and PAL); designing with PROMs, PLAs, and PLDs. (2) 10. Positive logic convention vs. direct polarity indication with polarized signals. (0.5) 11. Types of digital output circuits (totem pole, open collector, and 3-state); applications of XOR and XNOR circuits; designing simple arithmetic and ALU circuits. (2) 12. Introduction to latches; clocks; descriptions of sequential circuits including state diagrams, edgetriggered flip-flops, asynchronous and synchronous inputs to flip-flops; simple synchronous counter analysis; and shortened length counters. (4) 13. Synchronous sequential state machine circuit analysis and design with supporting CAD packages, i.e. hardware description languages (HDLs). (5) Laboratory Projects and Schedule (specify number of weeks on each) See corresponding lab course, EE 169. Contribution of Course to meeting EAC Category 5 Requirements College-level mathematics and basic sciences: Engineering Topics (Science and/or Design): General education component: 0 credits 3 credits 0 credits Curriculum Category Content (specify hours per quarter) Area Algorithms Software Design Comp. Arch. Core 0 0 4 Advanced 0 0 0 Area Data Structures Prog. Languages Core 0 0 Advanced 0 0 Oral and Written Communications None; but students write formal lab reports in the laboratory course (CPE/EE 169) Social and Ethical Issues None Theoretical Content Students study several theoretical topics: Boolean algebra,; circuit minimization; digital design methods Problem Analysis Students learn to translate written problems into working digital circuits Solution Design None