Topics Summary For CPS211 in W'04

advertisement

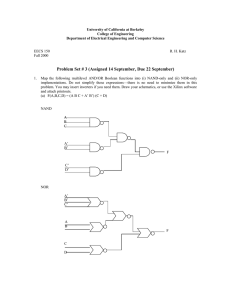

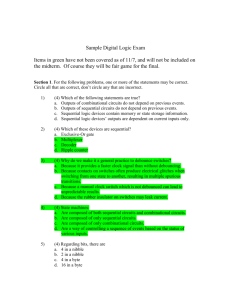

CPS211 – W’04, Dr. A. SadeghianAbhari Page 1 Topics Summary For CPS211 in W'04 "Digital Design" erd. Ed., M. Mano 2002, Prentice Hall CPS211 in W'04 0. Introduction Computing Machines Computer Architecture The Computer Brain; The CPU The Von Neumann Model 1. Number Systems A Formal Definition Focus on Number Bases Conversions Between Systems Complementary Systems Standard Coding Schemes 2. Computer Arithmetic with Binary Numbers using a Complementary System using Coded Numbers (BCD) END OF WEEK 1 & 2 3. Basic Logic Elements Fundamental Set; AND , OR, NOT Expanded Set; NAND, NOR, XOR, XNOR Logic Gates; Electronic Logic Elements Electronic Number Representation; Voltage Levels Logic Equations Logic Circuits Diagrams Positive and Negative Logic Implementations 4. Boolean Algebra Laws of Boolean Algebra DeMorgan’s Theorem Mapping Boolean Functions Formalism of Karnaugh Mapping K-Maps up to 5 variables Minimization Function Forms : SOP and POS Circuits from Minimized Fn using NAND (NOR) only END OF WEEK 3 & 4 5. Combinational Circuits Filters Even/odd numbers 2-bit magnitude comparator Complementors (2's) 8-bit n-bit MUX 4-chan 1-bit 2-chan 2-bit DEMUX Encoders - 4-bit in/ 2-bit out Decoders 1 of 8 1 of n (extended) Binary Adders Half-Adder (HA) Last Updated: Jan. 04, 04 CPS211 – W’04, Dr. A. SadeghianAbhari Page 2 Full-Adder (FA) Adder/Subtracter (8-bit) Circuit ALU 4-bit Design supporting : 4-bit comparator Logic Functions : AND,OR,NOT,XOR Arithmetic Functions : ADD, SUB, 2's Comp. END OF WEEK 5 & 6 & 7 6. Basic Sequential Devices R-S NOR and NAND Latch ( S-R vs R-S ) Gated Latches (level triggered) Clocked Flip-Flops (edge-triggered both + and -) 7. Fundamental Sequential Circuits Master-Slave Pulse Generator Data Flip-Flop Toggle Flip-Flop J-K Flip-Flop All Function J-K Arrangements Timing Diagrams; reading and creating END OF WEEK 8 & 9 8. How to Design Sequential Circuits Excitation Table State Table State Diagram Design Procedure 8. Registers & Counters Counters; synchronous and asynchronous, both up- and downRegisters; Parallel and Serial; read and write Register Files; leading to MEMORY Memory from Memory Cells Bus Structures Serving Memory Access 9. Memory Address Decoding fully decoded linear decoding partial linear addressing 10. CPU (Central Processing Unit) Level 0 overview architecture Operation Principle; Fetch/Execute Cycle Level 1; detail on: ALU section Address Section Data Section Control Unit Section Internal Bus Connections External Bus Linkages END OF WEEK 10 & 11 & 12 & 13 Last Updated: Jan. 04, 04