tilecal-pub-2007-003

advertisement

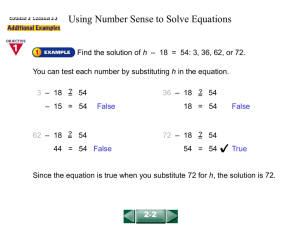

ATLAS Internal Note March, 2007 Temperature studies of the TileCal ROD G-Links chips for the validation of the air-cooling system A. Ruiz-Martíneza, A. Valeroa, J. Abdallaha, V. Castilloa, C. Cuencaa, A. Ferrera, E. Fullanaa, V. Gonzálezb, E. Higona, A. Munara, J.Povedaa, B. Salvachuaa, E. Sanchísb, C. Solansa, J. Torresb, J. A. Vallsa a Dpto. de Física Atómica, Molecular y Nuclear and IFIC (CSIC-UV), b Departamento de Electrónica, Universidad de Valencia Aptdo. 22085, Valencia, Spain Abstract In this paper we show the results of the temperature studies performed on the TileCal ROD G-Links receiver chips in order to validate the air-cooling system. In the first part of the note we present results on the characterization tests of the temperature monitor system for the G-Link chips of the TileCal ROD motherboard, performed at IFIC-Valencia. We report on the performance of the temperature monitoring system and some cooling studies of a single ROD motherboard. We conclude that the present system can be successfully used to online monitor the temperature of the ROD G-Links chips. In the second part we show the results of the studies performed with multiple RODs in a standard 9U VME crate in the laboratory at IFIC, and in their final location in the ATLAS cavern. We conclude that the air-cooling provided by the standard VME crate fans is enough to keep the temperature of the G-Links chips well within specifications. 1 Index 1 Introduction ..........................................................................................................................................3 2 Temperature operation range for the HDMP-1024 chip ..................................................................3 3 The G-Link receiver chips temperature monitor system of the TileCal ROD motherboard ........5 4 Setup and system noise measurements ...............................................................................................6 5 G-Link chips temperature measurements .........................................................................................9 5.1 Thermistor response to external cooling sources .........................................................................9 5.2 Long term temperature measurements .......................................................................................10 5.3 Air flux cooling measurements ...................................................................................................11 6 G-Link receiver chip temperature studies in TileCal ROD production test-bench .....................13 7 G-Link chip temperature studies in USA15 ....................................................................................15 8 Conclusions .........................................................................................................................................18 Acknowledgments ........................................................................................................................................19 References ....................................................................................................................................................20 2 1 Introduction The ATLAS calorimeter Read Out Driver system (ROD) [1] receives the front-end data through a high frequency link handled at 40 MHz. To reduce the number of links between the front-end and the ROD, the incoming 16-bit data are serialized before being sent to the ROD through a HDMP-1022 G-Link chip [2]. At the ROD motherboard, the data are deserialized through the HDMP-1024 G-Link chip receiver [2]. Both chips are commonly used to build high-speed data links and are manufactured in monolithic bipolar technology. The ATLAS TileCal ROD motherboard [3] is a modification of the originally designed ATLAS calorimeters common ROD, with the same G-Link system. However, due to the much higher channel density of the Liquid Argon (LAr) calorimeter detector with respect to TileCal, the G-Link chips have to be clocked at 80 MHz in the LAr design in order to achieve the required bandwidth [1]. This is beyond of the HDMP1024 chip nominal specifications. The LAr group has demonstrated that the chips can be reliably overclocked if the temperature of the chips is kept below 35 °C [4]. For that purpose, a water cooling system has been developed by the LAr group to refrigerate the G-Link receiver chips. For TileCal the chips will be clocked at 40 MHz, well within the manufacturer specifications. In this note, we report on the characterization of the temperature monitoring system of the TileCal ROD motherboard. We also present temperature measurements of the ROD G-Link chips in an air-cooled VME crate with single and multiple ROD boards. Section 2 presents a study of the temperature operation range of the HDMP-1024 chip and how the temperature and other factors affect the Bit Error Rate (BER) of this component. Section 3 describes in detail the ROD motherboard temperature monitoring system. Section 4 describes the setup and shows some electronic noise issues which could be eventually avoided in a future revision of the ROD motherboard. Section 5 reports on the measurements performed with a single ROD in an air-cooled VME crate: cross calibration with a temperature probe, response of the system when the G-Links chips are cooled with dry ice, long term temperature measurements and G-Link chips temperature dependence on the cooling air flux. Finally, Sections 6 and 7 describe the studies done in the laboratory and in USA15 (ATLAS electronics cavern) with 8 and 16 RODs inserted in the same crate. 2 Temperature operation range for the HDMP-1024 chip The HDMP-1024 receiver is used to build a high-speed data link for point-to-point communication, so-called G-Link. This chip is connected by a differential signal with the Optical Receivers (ORx), and parallelizes data coming from the front-end. The serial data rate of the G-Link chip is selectable in four ranges and extends from 120 Mbit/s up to 1.25 Gbit/s. In TileCal ROD, the clock frequency used as reference by the G-Link receiver chips is 40 MHz, and it determines an input data rate of 640 Mbit/s (16 bits @ 40 MHz). The use of the 40 MHz clock represents one of the modifications needed to adapt the ATLAS calorimeters common ROD to TileCal requirements. On the other hand LAr G-Link receiver chips are clocked at 80 MHz which means a serial data rate of 1.28 3 Gbit/s. Rigorously it is beyond the manufacturer specifications. Nevertheless, after some studies [5], the LAr collaboration proved that the G-Link receiver chips could work at this rate if the temperature of the chips is kept below 35 ºC. For that reason and due to the fact that the air-cooling of the crate was not enough to meet this requirement, a water cooling circuit was designed and mounted on the ROD motherboard over the G-Link chips, in order to guarantee not to reach 35 ºC (Figure 1). Figure 1. Water cooling circuit for the G-Link receiver chips in the ATLAS calorimeters common ROD. However, the input rate for the TileCal RODs is in agreement with the manufacturer specifications. At this rate, the manufacturer guarantees a correct operation below 85 ºC. Nevertheless, some studies related to the operation of the G-Link receiver chips as a function of the temperature and the input data rate showed a lower temperature upper limit for the correct behavior of the chip [5]. As shown in Figure 2, the BER increases if the G-Link chip is clocked at higher frequencies and the BER at a given frequency increases also with temperature. Thus for a fixed input rate we should keep the temperature as low as possible, in order to guarantee a low BER. For the TileCal ROD we choose the air-cooling in order to maintain the temperature of the G-Link chips within the manufacturer specifications and as low as possible. Bit Error Rate vs. Temperature, at 45 MHz Bit Error Rate Bit Error Rate Bit Error Rate vs. Data rate, at 21 ºC Parallel Data Rate (MHz) Temperature (ºC) Figure 2. G-Link receiver chips Bit Error Rates as a function of the input data rate at 21 ºC (left) and the temperature at 45 MHz (right) [5]. 4 3 The G-Link receiver chips temperature monitor system of the TileCal ROD motherboard The temperature of each of the 8 ROD HDMP-1024 chips (Figure 3) is measured with a Negative Temperature Coefficient (NTC) resistor model Siemens B57702-M103G [6]. The NTC is connected to the board ground and, in series with a 10 k resistor, to the 3.3 V power of the ROD board, which is directly supplied from the VME power crate (Figure 4). The thermistor resistance depends on the temperature and therefore the voltage drop across it. At ~40 °C a change of 5 °C will induce a voltage drop across the thermistor of approximately 100 mV. A change of 100 mV on the thermistor voltage drop can also be induced by noise in the reference voltage, which in this case corresponds to the 3.3 V power of the crate. As we will show in Section 4, such noise and the induced oscillations on the temperature reading have been observed. Figure 3. The 8 G-Link chips of the TileCal ROD motherboard. The 8 temperature sensors (metallic washers with blue cable) are also shown on top of each G-Link chip. Figure 4. Schematic connection of the thermistor of each G-Link chip. For the TileCal ROD RREF is 10 kΩ, Vcc is 3.3 V and the thermistor resistance at 25 ºC is 9.78 kΩ. Figure 5. Schematic connection of the 8 G-Link chip thermistors and the MAXIM1110 ADC on the TileCal ROD motherboard. 5 The voltage from all the 8 thermistors are read out by a multichannel ADC from MAXIM IC [7] which has eight analog inputs and a serial 8-bit digital output (Figure 5). The reference voltage for the ADC is set to approximately 1.2 V through a voltage divider connected to the 3.3 V power, and is set in such a way that a 0 ADC counts reading corresponds to a thermistor temperature of approximately 40 °C (Figures 6 and 7). The ADC output is connected to the ROD Staging FPGA number 3, which gets the values continuously and stores them in internal registers readable through the VME bus. This register also stores the maximum and minimum temperature achieved by each GLink chip since the last reset. It has the capability of comparing the temperature to a predetermined value, and to issue an interrupt in case any of the G-Link chips temperature exceeds this value. Besides, a LED in the front panel of the ROD is switched on if the threshold is exceeded. One of the objectives of these temperature studies is to determine the most appropriate threshold for the TileCal ROD system, taking into account the air-cooling used and the work frequency of the TileCal G-Link chips. Figure 6. Thermistor temperature (in K) as a function of the voltage drop across the thermistor on the ROD motherboard. Figure 7. ADC counts versus input voltage for the MAX1110 ADC with voltage reference set to 1.2 V. 4 Setup and system noise measurements For the measurement of the G-Link chips temperature, a single ROD board is placed in a standard ATLAS VME air-cooled crate [8]. The air flux can be regulated varying the revolutions per minute of the fan, from 1200 rpm to 3600 rpm. For the DAQ, the program XTestROD [9] is used. Figure 8 shows the temperature readings of the 8 ROD G-Link receiver chips as a function of time. Each 10 seconds the temperature register is read once, and the result is plotted. Some channels show temperature jumps of ~20 ºC. These jumps are believed to be caused by electronic noise in the 3.3 V voltage reference of the thermistors and the ADC. 6 Figure 9 shows a scope screen shot when the 3.3 V power line is probed near the voltage reference of the thermistors. A 200 mV amplitude noise of 500 kHz is clearly seen. This noise is believed to be caused by a defective Wiener power crate supply [8], where the power supply commutation frequency of 100 kHz together with an unknown ground loop would result in such noise oscillations. Figure 8. Temperature reading (in ºC) of the 8 ROD G-Link chips as a function of time. Each 10 seconds the temperature registers are read once and the result is plotted. Figure 9. Scope screen shot of the 3.3 V power line near the G-Link chip thermistors voltage reference point. The observed 50 mV noise lays within the specifications of the Wiener power supply. The 500 kHz, 200 mV noise is believed to be caused by the Wiener power supply. 7 This noise can be filtered offline by simply computing the mean of several temperature readings acquired consecutively1. Figure 10 shows the temperature reading of 4 ROD G-Link receiver chips. For each point 100 events are acquired and the mean is plotted as a function of time. The temperature jumps have disappeared although in some cases big spreads are found in the sets of 100 readings. Figure 11 shows the temperature reading spectrum in ADC counts for 4 out of the 8 ROD G-Link chips. Most of the readings fall in a narrow peak of 1-2 ADC counts, with asymmetrical long tails due to the mentioned noise. These tails can be suppressed if instead of computing the mean, we take as the temperature value the mode of the distribution. Figure 10. Temperature reading of 4 ROD G-Link chips as a function of time. For each point, 100 events are acquired and the mean is computed. Error bars represent the temperature standard deviation over 100 readings. 1 The time interval between such two readings is undetermined and given by the speed of the VME crate controller [8]. 8 Figure 11: ROD G-Link chip temperature distribution in ADC counts. Only the temperature distributions of 4 out of the 8 G-Link chips are plotted. 5 G-Link chips temperature measurements 5.1 Thermistor response to external cooling sources To check the inertia of the G-Link chips temperature sensors, a piece of dry ice is applied directly on top of the G-Link chips while the temperature is continuously monitored. Figure 12 shows the temperature readings for 4 out of the 8 ROD G-Link chips. For G-Link chip 1 (located in the uppermost corner, further away from the crate fans), dry ice is placed on top of the temperature sensor one minute after the run has started, and is taken away two minutes later. The temperature drops in matter of seconds (approximately 20), and once the ice is taken away, it heats again very rapidly at the beginning (few seconds) and at a slower rate after that until the previous temperature is reach. The plateau at 15 °C is due to the fact that the voltage drop on the thermistor goes beyond the ADC range. The temperature increase, observed in the G-Link chips when the dry ice is applied to the other G-Link chips, is caused by the partial diversion of the air flux when the ice has to be applied on the other G-Link chips. 9 Figure 12. G-Link chip temperature reading taken as the mean of 100 consecutive reading and the errors as the standard deviation as a function of time when dry ice is placed on top of the G-Link chip temperature sensor: 1 to 3 minutes after the start of the test for the G-Link chip 1, 3 to 5 minutes for the G-Link chip 2, 5 to 6 minutes for the G-Link chip 3 and 6 to 7 minutes for the G-Link chip 4. G-Link chip 1 is located at the upper front corner of the ROD motherboard, with the G-Link chip 2, 3 and 4 located immediately beneath. 5.2 Long term temperature measurements In order to verify the stability in the temperature of the G-Link chips some runs were performed during more than 12 hours. The DAQ system was left processing emulated data and the temperature of the G-Link chips was read periodically. Figure 13 shows the temperature variation during the first 20 minutes after powering on the crate. The G-Link chips temperatures steadily increase during the first seven minutes. After this time the temperature is practically constant. 10 Figure 13. Temperature variation in all the G-Link chips in a ROD after powering on the crate. Figure 10 shows the temperature variation in some G-Link chips in a ROD during 15 hours processing data. The temperature is kept constant along the run. In Sections 6 and 7 we will show other results regarding long term runs with multiple RODs per crate. 5.3 Air flux cooling measurements The VME crate used for the measurements is air-cooled by means of fans located at the bottom of the crate [8]. The air flux can be regulated varying the revolution speed of the fans, from 1200 rpm to 3600 rpm. To somehow approach the much more efficient aircooling system that will be available at the USA15 room of the ATLAS cavern, the front side of the VME crate has been covered to enhance the chimney effect (Figure 14). However, it must be noticed that in the final setup, the VME crate will be populated with at least 8 RODs and 8 Optical Multiplexer Boards (OMB), so the heat conditions may be radically different. We will study these setups with multiple RODs in Sections 6 and 7, but we will see now the effects of the air-cooling flux in the temperature of G-Link chips with single ROD. 11 Figure 14. The VME crate used at Valencia for the ROD G-Link chip temperature measurements. The blue cables are the optical fibers for the ROD input data. Figure 15. G-Link chip temperature as a function of time when changing the speed of the crate fans. The fans revolutions start at 3600 rpm and then they are decreased to 1200 rpm during 15 minutes. Figure 15 shows the temperature of 4 G-Link chips when the fan revolutions are decreased from 3600 rpm to 1200 rpm during 15 minutes. Finally, the revolutions are setup again at their maximum speed of 3600 rpm. The G-Link chip temperature steadily increases from approximately 50 ºC to 68 ºC, in both cases well within the HDMP-1024 G-Link chip [1][2] specifications. 12 6 G-Link receiver chip temperature studies in TileCal ROD production test-bench Figure 16 shows the test-bench used for the TileCal ROD validation at IFICValencia laboratory. The RODs to be validated were inserted in a 9U Wiener remote power supply crate [8]. This crate is air-cooled by 6 fans placed in two rows on the bottom part of the crate. The remote power supply is located in the top part of the crate. Besides the test-bench was composed by other hardware components to inject and verify the data processed by the RODs as well as software to configure the tests [11]. ROD crate OPTICAL BUFFER OMB 6U PC_2 PC_3 PC_1 DUAL TIMER Figure 16. Picture of the ROD production test-bench. Two types of temperature studies were done with this setup. In the first one 8 RODs were plugged the crate. In the second one 16 RODs were inserted together, emulating the final composition in the ATLAS experiment with 8 RODs and 8 OMBs. In the ATLAS experiment a TileCal partition will be composed by 64 modules connected by optical links with 8 RODs in a crate. The temperature was studied in this situation with 8 RODs in the same crate. During TileCal operation the crate slots from 6 to 21 are reserved for 8 RODs and 8 OMBs. RODs will be placed in slots 6, 8, 10, 12, 14, 16, 18 and 20. In consequence odd slots are reserved for OMBs. Table 1 shows the GLink chips temperature measurements for 8 RODs in a crate after at least 10 hours processing data. As shown in Section 5.2, some minutes after the crate power on the temperature remains practically constant (Figure 13). Thus 10 hours is enough time to consider that the temperature will remain unchanged. The warmest G-Link chips are number 2 and 3 in all the RODs. This is because those chips in the bottom part of the ROD receive a higher air flux from fans and G-Link chip1 in the top part is cooled also by external air. 13 In addition, there is also a variation in the G-Link chip temperature regarding the slot where the RODs are plugged, believed to be caused by the fan position respect each slot. Table 1.G-Link chip temperature (±1 ºC) in a crate with 8 RODs in the laboratory. G-Link / Slot 1 2 3 4 5 6 7 8 6 42 44 44 42 40 40 36 30 8 45 45 44 45 45 44 40 32 10 45 44 44 45 44 42 36 32 12 42 44 42 40 40 36 36 32 14 45 45 44 45 45 42 40 30 16 50 55 55 55 49 45 45 40 18 44 44 45 45 44 44 42 36 20 44 44 45 45 44 42 40 36 However a final partition in TileCal experiment will consist of 8 RODs and 8 OMBs per crate as shown in the previous section. As the OMBs are not yet available, in order to emulate this situation 16 RODs were inserted in the same crate. The OMBs will be also 9U VME boards and the conditions in air flux terms will be very similar with RODs and with OMBs. Table 2 presents the G-Link chips temperature measurements for all the RODs in a crate after more than 10 hours processing data. Table 2. G-Link chip temperature (±1 ºC) in a crate with 16 RODs in the laboratory. G-Link / Slot 1 2 3 4 5 6 7 8 6 45 45 45 45 42 40 36 32 7 45 45 45 45 44 43 40 36 8 49 55 55 49 47 45 45 36 9 49 55 55 49 49 45 45 40 10 55 55 55 49 47 45 43 36 11 55 55 55 55 49 46 45 36 12 49 47 45 45 45 43 40 32 13 45 45 45 44 43 40 36 32 14 45 45 45 45 45 43 40 36 15 46 49 49 49 46 45 45 40 16 49 49 47 47 45 45 43 36 17 62 66 62 62 55 55 45 43 18 55 62 62 55 55 49 45 40 19 55 55 55 49 47 45 45 36 20 45 45 45 45 44 43 40 36 21 45 45 45 45 45 43 40 36 Again, the warmest G-Link chips in all the RODs are those in the top part. Besides, as observed in the case of 8 RODs per crate, some slots have a worst cooling behavior, also believed to be caused by the position of the fans with respect to the crate slots. Figure 17 shows the relationship between slots and its position with respect of the fans and the temperature reached in G-Link chip 2 (worst case) in each slot. 14 Figure 17. Temperature in G-Link chip 2 as a function of the slot in the crate of the laboratory after 10 hours of processing data superimposed to an actual picture of the crate. 7 G-Link chip temperature studies in USA15 Once the TileCal ROD production was almost finished the commissioning tasks started in the ATLAS cavern at CERN. For the commissioning some RODs were installed on their final placement in USA15. Moreover, final crates installed in the USA15 racks are not exactly the same model as those used for TileCal ROD production. In the test-bench, the remote power supply was placed in the top part of the crate [11]. In the pit, the remote power supply is placed behind the crate providing a better air flux. Besides, the air coming from the fans is cooled before going through the RODs with heat exchangers. For these reasons, a better cooling was expected on the pit crates. The same temperature tests performed in the laboratory were repeated in the pit to corroborate the results obtained. Figure 18 shows a whole rack used in USA15. There are two racks for the TileCal readout electronics. Each of these racks consists of two 9U VME crates and two 6U VME crates. The 9U VME crates will hold the RODs and OMBs and the 6U VME crates are for trigger modules. There is a fan system below each crate and the whole rack acts as a chimney. In fact each crate takes the air coming from the crate below and expels the air to the crate above. The crate in the bottom part was chosen for the temperature studies and, in order to improve the chimney effect, the crates in the top part of the rack were covered with front panels and kept switched on during the studies. 15 Figure 18. Rack with a crate with 16 RODs in USA15. Table 3 presents the G-Link chips temperature measured after more than 10 hours processing data in a crate populated with 8 RODs (placed in the even slots). Table 3. G-Link chip temperature (±1 ºC) in a crate with 8 RODs in USA15. G-Link / Slot 1 2 3 4 5 6 7 8 6 40 45 45 45 43 40 36 28 8 36 40 40 40 36 32 32 28 10 36 40 36 36 32 30 28 28 12 36 40 40 40 36 36 32 28 14 36 40 36 36 36 36 30 28 16 40 42 42 40 36 36 32 28 18 42 45 45 45 45 45 40 32 20 40 43 42 40 36 36 36 36 Comparing Table 1 (laboratory results) and Table 3 (pit results), we can conclude that the situation in the pit is considerably better. In both cases, slots 16 and 18 are the warmest and G-Link chips 2 and 3 receive worse cooling. Finally, the study with 16 RODs per crate emulating the final composition in the ATLAS experiment was repeated in USA15. Table 4 shows the G-Link chips temperatures measured after more than 10 hours processing data. 16 Table 4. G-Link chip temperature (±1 ºC) in a crate with 16 RODs in USA15. G-Link / Slot 1 2 3 4 5 6 7 8 6 40 43 43 40 36 36 32 28 7 36 37 36 36 36 35 32 28 8 36 44 44 43 40 36 36 28 9 36 36 36 36 36 36 32 28 10 36 40 36 36 36 32 29 28 11 36 40 40 40 36 36 32 28 12 40 43 43 40 40 36 32 28 13 36 40 40 36 36 32 29 28 14 36 40 36 36 36 32 29 28 15 45 45 45 45 43 40 36 29 16 44 45 45 44 43 40 36 29 17 44 45 45 43 40 36 35 28 18 47 49 49 46 45 45 40 32 19 45 45 45 45 45 45 42 36 20 45 45 45 45 44 40 36 30 21 40 45 43 40 36 36 32 29 Once again the results obtained in USA15 are considerably better than those obtained in the laboratory. The G-Link chip with highest temperature in the pit is G-Link chip 2 in slot 18 (49 ºC), whereas in the laboratory is G-Link chip 2 in slot 17 (66 ºC). Regarding the temperature as a function of the slot in this case the worst slots are from 15 on, especially slot 18. Figure 19 shows the temperature in G-Link chip 2 (worst case) as a function of the slot in the crate. 70 65 Temperature (ºC) 60 55 Laboratory USA15 50 45 40 35 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 Slot Figure 19. Temperature (±1 ºC) in G-Link chip 2 as a function of the crate slot in the laboratory and in USA15 after more than 10 hours processing data. To conclude some long runs were performed in USA15. The temperature in the G-Link chips was measured every 30 seconds and during 100 hours in order to verify the temperature stability in the pit. Figure 20 shows the temperature as a function of time in G-Link chip 2 on each ROD with 8 RODs per crate. The temperature is stable and in all the cases below 55 ºC. 17 Figure 20. Temperature in G-Link chip 2 as a function of time in a crate with 8 RODs in USA15. 8 Conclusions The TileCal ROD G-Link chip temperature monitoring system has been characterized at the IFIC-Valencia TileCal laboratory. The system shows an adequate performance of the online G-Link chip temperature monitoring, although some potential undesired sensitivity to electronic noise has been observed. Preliminary temperature measurements of one single ROD board in a standard ATLAS VME crate showed that the crate air-cooling system was able to keep the temperature of the 8 G-Link chips in the range of 50 to 60 °C, well within the G-Link chip specifications. The laboratory temperature tests with multiple RODs showed the worsening of the cooling performance when the number of RODs inserted in the crate was increased. It was studied the behavior of the cooling as a function of the crate slot. Nevertheless, even with 16 RODs inserted in the crate the temperature remained within the manufacturer specifications. Finally, the study was repeated in the RODs final location in the ATLAS cavern at CERN. The cooling system in USA15 was proved to work better than in the laboratory and the temperature results showed lower values in all cases. With these results the Staging FPGA firmware was modified in order to set the temperature threshold for the LED in the front panel of the ROD at 65 ºC. The ROD will send an interruption through the VME bus if this temperature is reached. At this temperature the ROD should work correctly, but such a temperature in any G-Link chip implies a wrong operation in the cooling system. 18 Acknowledgments We would like to thank the entire Liquid Argon Calorimeter ROD group for their useful comments, suggestions and unvaluable help, especially Imma Riu for her explanations about the ROD G-Link chip temperature monitoring system. 19 References [1] The ROD Mother Board for the ATLAS Liquid Argon Calorimeter. A. Blondel, D. La Marra, A. Léger, I. Riu, A. Straessner. June 2004. ATLAS EDMS document ATL-ALEN-0055. [2] Agilent Technologies, HDMP-1022/24 · Low Cost Gigabit Rate Transmitt/Receive Chip Set with TTL I/Os. [3] TileCal ROD Hardware and Software Requirements. J. Castelo et al., ATLTILECAL-2005-003. CERN, Feb 2005. [4] The ATLAS LARG ROD G-Links Cooling System. F.Hubaut, B. Laforge, Ph. Repain, F. Rossel, D. Vincent. ATL-ELEC-2004-002; CERN, Mar 2004. [5] Integration Studies of the Optical Data Link for ATLAS Liquid Argon Calorimeter Readout System. T. Liu, J.Ye. SMU-HEP-04-02. Southern Methodist University, Physics Department, Dallas TX 75275, USA. [6] Temperature measurement probe assembly. (http://dpnc.unige.ch/LArgROD/CapteurdetemperatureB57703.pdf) [7] MAX1110, +2.7V, Low Power, Multichannel Serial 8-Bit ADC. [8] Wiener, Series 6000 LHC, VME -64x. User’s Manual. http://ess.web.cern.ch/ESS/ePoolDoc/239_1261.pdf. [9] Standalone Software for TileCal ROD Characterization and System Tests, J. Poveda et al., ATL-TILECAL-2004-012. CERN, Dec 2004. [10] Concurrent Technologies, VP 110/01X Low Power Embedded VME Controller. [11] Setup, tests and results for the ATLAS TileCal Read Out Driver production, A.Valero. et al., 12th Workshop on Electronics for LHC and Future Experiments. Valencia (Spain) September 2006. 20