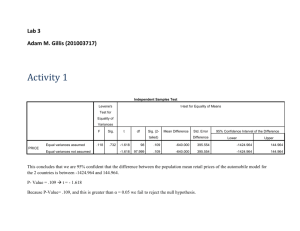

Lab9與Lab 10 需交實習報告,每組交一份,報告內容需包括以下五部分

advertisement

科技工程與管理系

課程名稱: 數位系統設計

HOMEWORK # 2

班級: XXX

姓名: XXX

學號: XXXXXXX

繳交期: XXXXXXX

需交的作業:

1.根據各題要求寫出 VHDL 碼。

2.將你所寫的 VHDL 碼使用 quartus II 進行 functional 模擬,印出

並說明你的模擬結果。

HW#2

1. The top-level diagram of a 4-by-2 encoder is shown in Fig.1. One and only one input bit is expected to be

high at a time, whose address must be encoded at the output.

Fig.1

(a)

(b)

Design the encoder using WHEN…ELSE concurrent statement.

Design the encoder using WITH..SELECT… WHEN concurrent statement.

Sol: 4-by-2 encoder

x(3:0)

y(1:0)

0001

00

0010

01

0100

10

1000

11

(a)

-- Homework #2 (1.a)

-- Design a 4-by-2 encoder using WHEN…ELSE concurrent statement.

library ieee;

use ieee.std_logic_1164.all;

entity p1_a is

port (

x : in std_logic_vector(3 downto 0);

y : out std_logic_vector(1 downto 0)

);

end p1_a;

architecture a of p1_a is

begin

y<= "00" WHEN (x="0001") ELSE

"01" WHEN (x="0010") ELSE

"10" WHEN (x="0100") ELSE

"11";

end a;

(b)

-- Homework #2 (1.b)

-- Design a 4-by-2 encoder using WITH..SELECT… WHEN concurrent statement

library ieee;

use ieee.std_logic_1164.all;

entity p1_b is

port (

x : in std_logic_vector(3 downto 0);

y : out std_logic_vector(1 downto 0)

);

end p1_b;

architecture a of p1_b is

begin

with x select

y <="00" when "0001",

"01" when "0010",

"10" when "0100",

"11" when others;

end a;

2. Using only concurrent statements, design the 8-bit unsigned adder in Fig.2

.

Fig.2

Sol:

-- Homework #2 (2)

-- Using only concurrent statements, design the 8-bit unsigned adder

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity p2 is

port (

a,b: in std_logic_vector(7 downto 0);

cin: in std_logic;

sum : out std_logic_vector(7 downto 0);

cout: out std_logic

);

end p2;

architecture a of p2 is

signal tempsum: std_logic_vector(8 downto 0);

begin

tempsum <= ('0' & a) + ('0' & b)+ cin; -- pad with ‘0’ before addition

sum <= tempsum(7 downto 0);

cout <= tempsum(8);

end a;

3. Design a circuit capable of converting Binary code to Gray code in Table 1.

Table .1

Sol:

- Homework #2 (3)

-- Design a circuit capable of converting Binary code to Gray code

library ieee;

use ieee.std_logic_1164.all;

entity p3 is

port (

binary_in : in std_logic_vector(3 downto 0);

gray_out : out std_logic_vector(3 downto 0)

);

end p3;

architecture a of p3 is

begin

WITH binary_in SELECT

gray_out <=

"0000" WHEN "0000",

"0001" WHEN "0001",

"0011" WHEN "0010",

"0010" WHEN "0011",

"0110" WHEN "0100",

"0111" WHEN "0101",

"0101" WHEN "0110",

"0100" WHEN "0111",

"1100" WHEN "1000",

"1101" WHEN "1001",

"1111" WHEN "1010",

"1110" WHEN "1011",

"1010" WHEN "1100",

"1011" WHEN "1101",

"1001" WHEN "1110",

"1000" WHEN OTHERS;

end a;

4. Fig.3 shows the diagram of a very simple barrel shifter. In this case, the circuit must shift the input vector

( inp(7 downto 0) ) either 0 or 1 position to the left. When actually shifted (shift = 1), the LSB bit (inp(0))

must be filled with ‘0’ (shown in the bottom left corner of the diagram). If shift =0, then outp = inp; else, if

shift = 1, then outp(0) = ‘0’ and outp(i) = inp(i - 1), for 1≦i≦7. Write a concurrent code for this circuit.

Fig.3

Sol:(Method I)

--component MUX 2-to-1

library ieee;

use ieee.std_logic_1164.all;

entity mux2to1 is

port (

in_a, in_b, sel : in std_logic;

mux_out: out std_logic

);

end mux2to1;

architecture a of mux2to1 is

begin

mux_out<= in_a WHEN (sel='0') ELSE

in_b;

end a;

-- barrel shifter

library ieee;

use ieee.std_logic_1164.all;

entity p4 is

port (

inp : in std_logic_vector(7 downto 0);

shift: in std_logic;

outp : out std_logic_vector(7 downto 0)

);

end p4;

architecture a of p4 is

signal zero: std_logic;

component mux2to1

port ( in_a, in_b, sel : in std_logic;

mux_out: out std_logic);

end component;

begin

zero<='0';

U7: mux2to1 PORT MAP (

in_a => inp(7),

in_b => inp(6),

sel => shift,

mux_out => outp(7));

U0: mux2to1 PORT MAP (

in_a => inp(0),

in_b => zero,

sel => shift,

mux_out => outp(0));

G1:FOR i IN 1 TO 6 GENERATE

Ui: mux2to1 PORT MAP ( in_a => inp(i),

in_b => inp(i-1),

sel => shift,

mux_out

=> outp(i));

END GENERATE;

end a;

mux2to1:U7

inp[7..0]

in_a

in_b

shift

mux_out

sel

mux2to1:\G1:6:Ui

in_a

in_b

mux_out

sel

mux2to1:\G1:5:Ui

in_a

in_b

mux_out

sel

mux2to1:\G1:4:Ui

in_a

in_b

mux_out

sel

mux2to1:\G1:3:Ui

in_a

in_b

mux_out

sel

mux2to1:\G1:2:Ui

in_a

in_b

mux_out

sel

mux2to1:\G1:1:Ui

in_a

in_b

mux_out

sel

mux2to1:U0

in_a

0

in_b

mux_out

sel

RTL VIEWER

outp[7..0]

Sol:(Method II)

library ieee;

use ieee.std_logic_1164.all;

entity p4 is

port (

inp : in std_logic_vector(7 downto 0);

shift: in std_logic;

outp : out std_logic_vector(7 downto 0)

);

end p4;

architecture a of p4 is

begin

outp<= inp(6 downto 0)&'0' WHEN (shift='1') ELSE inp ;

end a;

shift

outp~[7..0]

SEL

inp[7..0]

DATAA

1' h0 --

OUT0

DATAB

MUX21

RTL VIEWER

outp[7..0]

5. Construct a circuit shown in Fig. 4 capable of comparing two 8-bit vectors, a and b.

A selection pin (sel)

should determine whether the comparison is signed (sel =’1’) or unsigned (sel = ‘0’). The circuit must have

three outputs, x1, x2, and x3, corresponding to a > b, a = b, and a < b, respectively

Fig. 4

Sol:

-- Homework #2 (5)

-- comparing two 8-bit vectors as signed or unsigned number

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

entity p5 is

port (

a,b : in std_logic_vector(7 downto 0); sel: in std_logic;

x1,x2,x3 : out std_logic

);

end p5;

architecture a of p5 is

signal x1_unsigned, x1_signed,

x2_unsigned, x2_signed,

x3_unsigned, x3_signed: std_logic;

begin

x1_signed<= '1' WHEN ((signed(a)>signed(b))) ELSE '0' ;

x2_signed<= '1' WHEN ((signed(a)=signed(b))) ELSE '0' ;

x3_signed<= '1' WHEN ((signed(a)<signed(b))) ELSE '0' ;

x1_unsigned<=

'1' WHEN ((unsigned(a)>unsigned(b))) ELSE '0' ;

x2_unsigned<=

'1' WHEN ((unsigned(a)=unsigned(b))) ELSE '0' ;

x3_unsigned<=

'1' WHEN ((unsigned(a)<unsigned(b))) ELSE '0' ;

x1 <= x1_signed WHEN (sel = '1') ELSE x1_unsigned;

x2 <= x2_signed WHEN (sel = '1') ELSE x2_unsigned;

x3 <= x3_signed WHEN (sel = '1') ELSE x3_unsigned;

end a;

LessThan3

a[7..0]

b[7..0]

A[7..0]

OUT

0

x3

B[7..0]

1

LESS_THAN

x3~0

Equal0

LessThan1

A[7..0]

OUT

B[7..0]

x2

A[7..0]

OUT

B[7..0]

EQUAL

LESS_THAN

LessThan2

A[7..0]

OUT

0

B[7..0]

1

x1~0

LESS_THAN

LessThan0

A[7..0]

OUT

B[7..0]

LESS_THAN

sel

RTL VIEWER

x1