Expected date of graduation: May, 2001

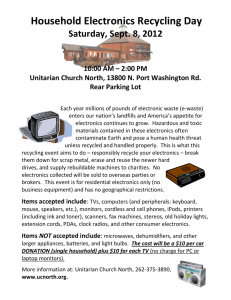

advertisement

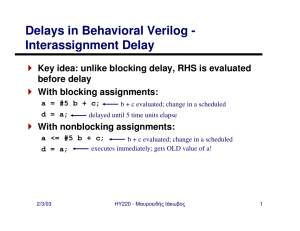

MD. REZWANUL ISLAM 12117, Diogenes Ct, Orlando , FL 32826 Phone: (407) 275-0432 (home) (407) 882-1014 (Office) Email: mri52842@cs.com OBJECTIVE: To obtain a challenging and dynamic position as an Electrical Engineer in VLSI Circuit design, Digital Logic design, Hardware or Product Engineer with long term career goal. PROFILE: Have knowledge of IC design, CAD tools and programming languages like Verilog, C and C++. Have experience in digital VLSI circuit design, simulation, synthesis, and layout. Expert in logic design, assembly language, device physics, computer architecture,. A team player and an exceptionally quick learner. EDUCATION: At present - M.S. Student, Physics University of Central Florida, Orlando, Florida Expected date of graduation: May, 2001 GPA: 3.75/4.0 1993 - M.Sc, Applied Physics & Electronics , Rajshahi University, Bangladesh. GPA: 76.7/100 (Stood First class first in the Science faculty) Thesis title: Recognition of Bengali Numerals using Artificial Neural Networks”, 1992 - B.Sc.(Hons.), Applied Physics & Electronics, Rajshahi University, Bangladesh. GPA: 78.1/100 (Stood First class first in the Science faculty) RELEVANT COURSE WORK: CMOS Digital & Analog IC Design, Structured VLSI Design, Architecture of VLSI design, Semiconductor Device Modeling & Simulation, Fabrication of Solid State Devices & VLSI Processing, Electronics Part-I, Electronics Part-II, Advanced Electronics, Basic Solid Sate Physics & Material Science, Digital Electronics, Geophysics and Computer Programming, Computer Technology, Computer Programming & Numerical Methods, Communication Engineering, Electrodynamics I, Electrodynamics II, Laser Engineering. . PROJECTS: 1. Design and Simulation of an ASIC for 8 bit Digital Sine/Cosine wave generator. Verilog code was written and simulated using Verilog –XL, Synthesized and Optimized using Ambit . 2. Design and Simulation for Digital Traffic Light Control System for a four way intersection with pedestrian circuit. Verilog code was written and simulation using Verilog XL, Synthesized and optimized using Ambit and Lay-ed out using Silicon Ensemble in Cadence environment. 3. Design of a 15-bit SRAM memory using the 0.18m CMOS process. The data bus is 3-bit wide , both read and write time <=50ns. Cadence Virtuoso has been used to perform the basic SRAM cell layout. 4. Design of a low voltage, low power CMOS operational amplifier with the following features (a) Gain > 2500, (b) Phase margin > 600 ,(c) Common mode range 1.2 v to 1.8, (d) Slew Rate > 5 V/s, (e) Load capacitance 10pF, (f) Power dissipation as small as possible. WORK EXPERIENCE May, 2000 to present : August, 1999 to May, 2000 Graduate Research Assistant : Dept. of Physics, University of Central Florida, Orlando, FL. Conducting Research on Growth of oriented, single carbon nanotube microscopy tips. Graduate teaching Assistant : Dept. of Physics, University of Central Florida, Orlando, FL. February,1998 to July, 1999 Lecturer, Dept. of Applied Physics & Electronics, Rajshahi University, Rajshahi, Bangladesh (Teaching and Research) PUBLICATIONS: Conf. Proc. International Conference of Computer & Information Technology -ICCIT98, BUET, Dhaka, December, 98 , “A technique for Fast minimization of Boolean function” Conf. Proc . National Conference of Computer & Information System, NCCIS97, BUET, Dhaka, November, 1997- “Recognition of Bengali Numerals using Kohonen Neural Network” Journal of Geophysics, India, Oct-1998, Vol XIX, No. 4, pp 211-217“Spectral Analysis of Gravity Anomalies of the North western part of Bangladesh” TECHNICAL SKILLS: Hardware Platform: SUN, PC. Languages: Verilog, C, C++, FORTRAN, BASIC, 8086 Assembly, Operating System: MS-DOS, UNIX Simulation & Synthesis Tools: Cadence, Verilog-XL, Ambit, Pspice. Layout Tools: Virtuoso, L-Edit, Silicon Ensemble. Packages: Mathcad, MATLAB, Excel. PERSONAL: Available to work from April, 2001. Willing to relocate. References are available upon request