414m1f02

advertisement

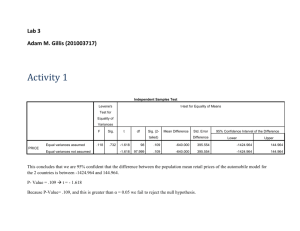

EE 414/514 VHDL DESIGN Dr. J.A. Starzyk MIDTERM I Tuesday, October 15, 2002 THIS IS A CLOSED BOOK EXAM Name: Box #: Note: 1) 2) Problem All scratch and problem papers must be turned in. Estimated times required to complete problems are indicated. 1 Weight (points) 15 Estimated Time (minutes) 10 2 10 5 3 10 10 4 10 10 5 10 10 55 45 TOTAL Examiner' Use only . . GOOD LUCK!!! Problem 1 Check true or false next to each statement: Problem 2 A poor attempt at a VHDL architecture for a 2-to-1 multiplexer is shown below.: Architecture art of mux2to1 is Begin Y <= a when (s = '0') else '0'; Y <= b when (s= '1') else '1'; End art; This obviously does not synthesize a 2to1 multiplexer. synthesized. Show the logic that is actually Problem 3 Analyze the following code – sketch the waveforms a1, a2, c1 and c2. entity DELAY is end DELAY; architecture RTL of DELAY is signal a1,a2,c1,c2 : bit; begin p0 : process begin a1<= '0','1' after 23ns,'0' after 28ns,'1' after 43ns,'0' after 63ns; a2<='0','1' after 20ns,'0' after 25ns,'1' after 40ns,'0' after 60ns; wait for 65ns; end process; p1 : process(a1,a2) begin c1<=a1 and a2 after 10 ns; c2<=transport a1 and a2 after 10 ns; end process; end RTL; Answer: 5 10 15 20 25 30 35 40 45 50 55 60 65 70 75 80 ns Problem 4 Draw the waveform for signal a,a1,a2,b1,b2 and variable vtmp in P1 process. Hint: the integer waveform can be draw like the following waveform. library IEEE; use IEEE.std_logic_1164.all; entity prob2 is end; architecture sigvar of prob2 is signal a:bit; signal a1:Integer:=50; signal a2:Integer:=51; signal b1:Integer:=60; signal b2:Integer:=61; begin a<='0','1' after 1ns,'0' after 2ns,'1' after 3ns; P1:process(a) variable vtmp:integer:=0; begin vtmp:=vtmp+1; a1<= vtmp; a2<= a1; end process; P2:process(a) begin b1<=a1; b2<=a2; end process; end sigvar; Answer: vtmp waveform is same as sigal a1; Problem 5 Use the component port map to finish the incomplete VHDL code based on the given schematic. u0_s a Half_adde r b INV Half_adde r binv cin library IEEE; use IEEE.std_logic_1164.all; entity substractor is port( a,b,cin: std_logic; s,co:out std_logic ); end; architecture structure of substractor is component half_adder port( a,b:in std_logic; s,co:out std_logic ); end component ; component inv port( a:in std_logic; b:out std_logic ); end component ; component orgate port( a,b:in std_logic; c:out std_logic ); end component ; signal u0_co,u0_s,u1_co,binv:std_logic; begin u0_co s u1_co orgate co Answer: u0:inv port map(a=>b,b=>binv); u1:half_adder port map(a,binv,u0_s,u0_co); u2:half_adder port map(u0_s,cin,s,u1_co); u3:orgate port map(u0_co,u1_co,co); end structure;