Impact of few electron phenomena on floating-gate memory

advertisement

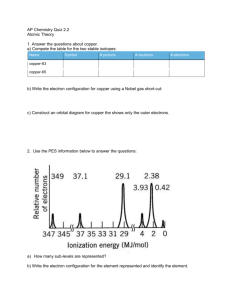

Degradation of floating-gate memory reliability by few electron phenomena Gabriel Molas, Damien Deleruyelle, Barbara De Salvo, Gérard Ghibaudo, Marc Gely, Luca Perniola, Dominique Lafond, Simon Deleonibus The authors are with the CEA-LETI Grenoble, Cedex 9, France (e-mail: gabriel.molas@cea.fr). D. Deleruyelle is with the L2MP-CNRS Marseille, Cedex 20 France. G. Ghibaudo is with the IMEP-CNRS/INPG Grenoble, Cedex 9 France. Keywords: Electron beam (e-beam) lithography, memories, quantum dots, silicon-on-insulator (SOI) technology. Abstract The purpose of this article is to give a quantitative evaluation of the intrinsic reliability limits of Floating Gate (FG) memories in the deca-nanometer range, due to the reduction of collective phenomena and to the dominance of single electron stochastic behaviors. To this aim, firstly, a model that quantitatively predicts the intrinsic dispersions of the memory retention time and programming window is proposed. Secondly, experimental results obtained on ultra-scaled memory devices (with an active area as small as 30nm x 30nm) with either a continuous poly-Si FG or Silicon nanocrystals (Si-ncs), will be shown and used to validate our model. Finally, extrapolations on the intrinsic reliability limits of future generations of Flash memories will be done. 1/23 I. INTRODUCTION Following the ITRS rules, NAND and NOR Flash memory devices are aggressively scaled down for high performance applications and high density integration. This is illustrated by the recent demonstrations presented in the literature: 70nm NAND Flash technology with 0.025µm² cell size [1], 8Gb NAND Flash Memory using 63nm Process Technology [2] and 70nm NOR Flash technology with 0.049µm² cell size [3] have been demonstrated. Currently, extensive studies are in progress in IC companies in order to scale further the memory cell and to solve the extrinsic reliability concerns (process related variations, ionic contamination) of future floating gate devices [4]. In this context, it becomes also urgent to address the intrinsic fundamental limits that FG memories will face once in the decananometer range, even before reaching the ultimate Single Electron Memory [5]. In particular, as the dimensions of flash memories are scaled down, the number of electrons representing one bit N dramatically reduces, enhancing the effects of single electron phenomena. As a consequence, few electron devices should not be considered as alternative devices, on the contrary, they allow to study the new physical phenomena such as single electron phenomena that will become predominant in future memory technologies. In this paper, we study the impact of these single electron phenomena on the performances of floating gate memory devices. We demonstrate that the charging and the discharging of scaled floating gate memories should no more be considered as a continuous phenomenon, but as a sum of discrete stochastic events. This leads to an intrinsic dispersion of both the retention time and of the memory programming window. In Section I, we present a theoretical study based on analytical models, allowing to calculate the intrinsic dispersion of the retention time and of the programming window. We treat the case of continuous floating gate memories, but also of Si-nc based floating gate memories, where the number of electrons per bit is further reduced. In Section II, we present experimental results obtained on an ultra-scaled memory, 2/23 processed on Silicon On Insulator (SOI) substrates, with either a continuous poly-Si FG or Sincs. We demonstrate that the charging and the discharging of these memory devices are controlled by single electron stochastic events, and we show the intrinsic dispersion of retention time and programming window on a single memory device. We exhibit that these experimental results are in good agreement with our analytical models. Finally, in Section III, we discuss these results and we make some predictions for the future memory nodes. II. MODEL In this Section, we propose analytical models allowing to calculate the number of electrons per bit in a floating gate memory, the dispersion of the retention time and the dispersion of the programming window of a memory device controlled by single electron phenomena. II 1. Number of electrons per bit The number of electrons per bit N is calculated as the number of electrons necessary to induce a threshold voltage shift Vth of 3V. The value of Vth is obtained with the classical formula of floating gate memory devices: Vth (1) N.q C IPD Where q is the elementary charge and CIPD the control gate to floating gate capacitance, expressed by: C IPD 0 .S IPD EOTIPD (2) where EOTIPD is the equivalent oxide thickness of the interpoly dielectric (IPD) and S IPD the floating gate area covered by the control gate. An approximation of SIPD is given by: SIPD W.L 2.H.L (3) 3/23 with W the channel width, L the gate length and H the floating gate thickness. Indeed, in current structures, the coupling ratio is increased by using an important floating gate thickness (H~W); covered by the control gate. In figure 1, we have represented the number of electrons per bit N as a function of the technological node, for NAND and NOR devices, but also for NAND Si-nc memory devices, from expectations of ITRS 2003. Concerning the devices presented in the literature, we used the technological characteristics given by the authors to extract W, L, H, and the top oxide EOT in order to calculate N. Concerning the theoretical curves that allow to make extrapolations for the future technological nodes, we made the assumption that H~W. In the case of NAND memories, we suppose that W=L=F, F being the technological node, while in the case of NOR memories, we consider that W=F. First-of-all, we can see that floating gate memory devices use less and less electrons and naturally become few electron devices. Moreover, it appears that the number of electrons per bit is more critical in the case of NAND memory devices than in the case of NOR memory cells, given the smaller cell active area: the number of electrons per bit reduces by a factor ~0.77 for each NAND Flash generation, each generation being defined as a 0.9 size reduction. So, in other words, the number of electrons which should be stored in the FG in order to set correctly the state of the memory cell dramatically decreases as the dimensions of Flash memory devices will be reduced. For example, the number of electrons per bit for the 35nm NAND technology node will be equal to 200. It should also be considered that these calculations have been done assuming only one bit per cell, while the use of multi-bit or multi-level cell memory technologies [6, 7] will result in an even more reduced number of electrons per bit. These theoretical calculations can be validated by advanced NOR and NAND devices in the literature, calculated from the described structures, for technology nodes going from 130nm to 65nm. Finally, this trend will further strengthen if new 4/23 technologies are introduced, using limited charge storage sites, such as in Si-ncs memories [8, 9]. The stochastic character of the charging process in a few electron memory has been addressed in [10], in the case of a nanometer size storage node. In this case, it has been demonstrated that there is an uncertainty on the number of charged electrons in the floating gate after writing due to the Poisson nature of the electron charging. Moreover, it is shown that Coulomb blockade modifies the charging kinetic. In our case, we will assume that in an ultra-scaled memory device, the charging (/discharging) of one electron to (/from) the FG can be described by a Poisson process with an exponential law in time and a lifetime d, depending on the charge stored in the floating gate and on the tunnel oxide transparency (/c, the electron capture time constant, depending on the oxide thickness and the writing voltage). However, no Coulomb blockade is taken into account. Indeed, in the case of continuous floating gate memories, the charging energy is negligible due to the large dimensions of the storage node. For the smallest devices we present in this work and also for the 35nm NAND technology node, the charging energy is estimated to ~10meV. In the case of silicon Si-nc based memories, the distribution of the diameters of the silicon Si-ncs is too important and coulomb blockade phenomenon is smoothed [11]. For instance, for a sheet density of 1012cm-2 Si-ncs with diameter of 4nm, a diameter standard deviation of 1nm completely hides the Coulomb blockade effect in the writing characteristics [12]. II. 2. Retention time dispersion As presented in [13], in a few electron memory, the Poisson nature of the electrons discharging phenomena induces a dispersion on the number of electrons lost from the FG in a fixed period, resulting in an uncertainty on the retention time TR (TR being defined as the time 5/23 when a fixed % of the stored charge is lost). In other words, we argue that the retention time TR is a stochastic variable. Based on these assumptions, the probability density of the retention time of Poly-Si FG memories and Si-nc memories will be analytically derived. We will show that the dispersion of the characteristics is more and more important as the dimensions are scaled. a. Retention time probability density Continuous floating gate devices We consider here a memory device containing N electrons in a continuous floating gate. Based on the previous discussion, we consider that the emission of one electron from the floating gate to the channel follows an exponential distribution law, with a time constant d. This assumption can be justified by making an analogy with the Random Telegraph Theory, where the charging and the discharging of a trap in a MOSFET is an exponential process [14]. The time constant d essentially depends on the tunnel oxide thickness and on the trapped charge in the floating gate (thus the internal electrical field). As a consequence this time is different for each emitted electron. In an exponential process, we can write that the discharging probability density is 1/d.exp(-t/d). We now suppose that the retention time is defined as the time when k electrons are emitted from the floating gate. For example, if we consider that the retention criterion corresponds to a charge loss of 20% of the initial stored charge, we have k=0.2xN. We have now to calculate the time when the kth electron will be emitted from the FG, or in other words, we have to calculate the probability that the retention time takes a particular value TR. This gives us the retention time probability density p(TR) whose derivation is provided in the Appendix: 6/23 t TR t t 1 TR t k 1 1 1 dt k 1...dt1 exp 1 ... exp k 1 k 2 exp t1 0 t k 1 t k 2 d1 d k 1 d k 1 dk d1 dk p(TR ) TR (4) k being the number of electrons lost at TR, defining the retention criterion (e.g. k=0.2N), ti the discharging time of the ith electron, di the time constant of the ith electron. This result is closed to the Markov process described by Yano et al. [10] to describe the charging time probability density in presence of Coulomb blockade. In our case, Coulomb blockade has not been taken into account, as the dimensions of the floating gates are not in the nm range. Note that the discharging time constants d of the k electrons of the floating gate are not equal one to the other, indeed, the time constant of each electron depends on the tunnel oxide electric field, which varies when the number of electrons in the FG changes. When the time constants i are close, the latter expression can be simplified and we obtain the following formula: k 1 TR TR 1 d p(TR ) exp d k 1! d (5) This is the case in particular when the retention criterion is small (e.g. k=0.2N), so that the electric field in the tunnel oxide does not vary much during the discharging process. This leads to a Poisson process, with a mean temporal value µ which increases with k: k 1. d (6) In Fig.2 we represented the calculated retention time distribution for various numbers of electrons per bit N. This figure shows that decreasing N implies a strong evolution of the retention time probability density, evolving from a Gaussian-like distribution (when N~250) to a pure exponential/Poisson-like distribution (when N~5). We can also see that the dispersion around the mean value increases as N is reduced. 7/23 Note that if the memory working includes over-erase process, i.e. if the erased Vth is smaller than Vth0, the same single electron phenomena could occur during retention for the erased state. Indeed, charge gain could also take place, following stochastic behaviors. Si-nc based floating gate devices In the case of a Si-nc based floating gate memory device, the adopted model is quite similar. We consider a memory containing N charged Si-ncs. The retention time is reached when k Sincs are discharged. The hypotheses of the model are the following: firstly, we assume that all the discharging events follow an exponential distribution law, with a unique discharging time constant d. In a more realistic approach, we have to introduce a sum of discharging time constants, depending on the dimensions of the Si-ncs and of the number of electrons trapped in each Si-nc. This distribution of d has been experimentally put in evidence in [13]. However, a mean time constant d can be considered at the first order, in order to simplify the model. Secondly, we assume that each Si-nc charged by one electron has the same impact on the channel conduction, and is responsible for an elementary threshold voltage shift dVth. Finally we assume that emission events are not correlated, what is a key difference with a continuous FG. Indeed, the retention time probability density is calculated from the product of the probabilities of charging and of discharging of the Si-ncs. We can thus express the retention time TR probability density by: 1 N! 1 exp TR p(TR ) d k 1!N k ! d k 1 exp TR d N k 1 (7) N being the number of electrons per bit and k the number of electrons lost at TR. Note that in our approach, we consider that the memory window Vth is independent of the memory cell dimensions and does not change when the dimensions are scaled down. Indeed, 8/23 specific phenomena may appear in scaled memory devices [15] but strongly depend on the memory structure and could hardly be taken into account with a simple approach. b. Retention time dispersion and memory failure time The widening of the retention time distribution, by scaling the number of electrons per bit, yields to an increase of the relative dispersion of the retention time following a 1/√N law, which is consistent with the central limit theorem. It is also important to notice that the relative dispersion of the retention time does not depend on the mean retention time. For a retention criterion of 20% of charge loss, we reach a relative dispersion of 10% when the number of electrons involved in one bit is equal to 500, which corresponds to the 55nm NAND technology node according to ITRS 2003. We can thus understand the difficulties and theoretical limits of few electron memories, extremely sensitive to the stochastic discharging behavior of the storage node. The probability density also allows to calculate the theoretical reliability durability. This time is defined as the time when a certain number of memory cells of a memory array is discharged, e.g. one cell over one Megabit (1/106). This is expressed by the retention time cumulative probability, which is correlated to the probability that one memory cell is discharged at a time t. Thus, the cumulative probability gives the percentage of discharged memory cells, and is calculated for both types of devices by: C(T) pt dt (8) T 0 In the case of a continuous FG memory, and if we assume that the discharging time constants are of the same order of magnitude, the cumulative probability leads to the Euler gamma function: 9/23 k 1 t t 1 1 gamma (k) gamma (k, T) C(T) exp dt t 0 k 1! d k 1! d d T (9) In the case of a Si-nc based memory, the cumulative probability leads after calculations to: C(T) k 1 T d N! 1ki1 .N k i 1 1 . exp d .N k !k 1! i0 N k i 1 d (10) In figure 3 we have represented the cumulative probabilities for continuous floating gate memory devices for different values N of electrons per bit. On the one hand, for large values of N, the cumulative probability evolution is very abrupt. On the other hand, we can see that as N decreases, the distribution tails become less sharp, what means that the number of memory cells that will be discharged will become critical, even for short times. For a 1Mb memory array, with memory cells having a mean retention time of 10 years, and containing 5 electrons per bit, we can observe that one cell will be discharged after only a few hundreds of seconds. II 3. Programming window dispersion The laboratory of Hitachi [10] has already shown that the reduction of the number of electrons in an unique storage node could lead to an uncertainty of the number of stored charge after writing. Thus the threshold voltage shift after writing is also a stochastic variable. Here we propose a model for Si-nc based memory devices. We assume that the charging process follows an exponential distribution law, with the same time constants C for all of the Si-ncs. The aim of this model is to calculate the probability that a number n of electrons are charged after a writing time TW. Based on our assumptions, we can write that this probability P(n) is expressed by : TW N! 1 exp Pn n!N n ! C n TW exp C 10/23 N n (11) One should notice that this probability does not depend explicitly on T W, but only the ratio TW/C. The maximum threshold voltage shift Vth-max=Vth(N) is obtained when the cell is fully programmed. As all the charged Si-ncs are supposed to induce the same discrete threshold voltage shift, we can write that the threshold voltage shift due to the charging of n Si-ncs is: Vth n n.Vthmax N (12) From these latter two equations, it is possible to have an expression of the probability that the threshold voltage shift takes a particular value. In figure 4 we have represented the calculated probability distribution after writing for three memory devices. These three devices have the same Si-nc density, and the same Vth-max, but correspond to three different technology nodes. Consequently, they don’t have the same number of Si-ncs and electrons per bit. We can see that when the number of Si-ncs decreases, i.e. when the number of electrons per bit is small, the Vth distribution is larger, the devices having the same mean value of Vth. This can be explained by the fact that when N is reduced, a variation of only one electron in the floating gate leads to an important variation of Vth. III. EXPERIMENTS III. 1. Characterisation of single electron phenomena a. Device processing Poly-Si FG memories (Fig.5.a: type A) have been fabricated on a SOI substrate using electron-beam lithography and optimised etching [16]. In some devices, an active area (WxL) as small as 30x30nm² was reached. In order to further limit the number of electrons per bit, similar structures using Si-ncs instead of poly-Si FG were also fabricated (Fig.5.b: type B). Note that these devices were not optimised to reach high performances. Their tunnel oxides 11/23 were intentionally fabricated with small thicknesses (3nm for type A and 2.5nm for type B) in order to accelerate the single electron charging/discharging phenomena. We claim that using thin tunnel oxides only changes the time constants of the charging and discharging events, but not the physics (and the stochastic character) of single electron phenomena and is not penalizing for our study. Due to the very small active area, both Si-nc and poly-Si devices are sensitive to single electron discharging. Thus discrete threshold voltage shifts can be observed in the electrical characteristics [13, 17]. In previous wok we demonstrated that dVth is inversely proportional to the device active area for both poly-Si and Si-ncs FG memories [16]. These results showed that basic demonstrated electrostatic formulas (i.e. dVth α q/CIPD, being CIPD the FG to control gate capacitance directly proportional to the device area) also apply to few electrons devices at the first order. This also showed that the smaller the memory device, the more sensitive to single electron phenomena. In order to validate this result, 3D Poisson simulations were performed using SILVACO tools, showing that in a poly-Si FG device the simulated Vth is proportional to the number of stored electrons [16]. Concerning Si-nc memories, the simulated dVth (15.4mV) and the experimental one (18mV) are very close, confirming that the impact of one electron in a Si-nc is spread all over the device active area for the same arguments of the Random Telegraph Signal theory [13]. III. 2. Intrinsic reliability concerns Secondly, a quantitative evaluation of the intrinsic reliability concerns of few electron memories was done. Devices with different numbers of electrons per bit were studied, by varying dimensions (W, L) and programming windows. For each memory device, we performed ID(time) measurements after programming. The measurements were performed with a low value of VG in order to operate the device in the sub-threshold regime. Knowing 12/23 the sub-threshold slope, these ID(time) characteristics were transposed to Vth(time) measurements, from whom we extracted the retention times (assuming a given retention criterion). By repeating hundreds of times these measurements for each device, we obtained a statistical distribution of the retention time, dispersed around its mean value from one run to another due to the stochastic nature of the floating gate discharging. This distribution, as well as the relative dispersion (or relative standard deviation), were compared to the theoretical ones. The number N of electrons per bit was extracted from the ID(time) characteristics as the ratio of the threshold voltage shift after programming Vth and the mean value of the discontinuities dVth. It is thus equal to the number of drain current discontinuities measured on the ID(time) characteristics from the written state to the equilibrium state. In conclusion, the only fitting parameter of the model is the discharging time constant, or in other words the mean retention time. Note that the discharging time constant has no impact on the shape of the distribution and on the value of the relative dispersion. This time constant can also be theoretically calculated or extracted from the slope of the emission time histograms [13]. In figure 6 we present the retention characteristics (for three successive runs) of two devices with different dimensions. The discharging of the FG is made electron by electron, leading to a stepwise behavior. We obtained the retention time distribution from hundreds of measurements, for a criterion of 50% of charge loss. We can see that the relative dispersion of retention time is more important for the small device (R=38.7%) than for the device with the larger active area (R=9.3%). Our theoretical model allows to explain correctly the shape of the distributions and the relative dispersions. In order to generalize this result, we repeated these measurements for a large variety of devices (types A and B) for different dimensions W and L, and different writing conditions. This allowed us to plot the retention time relative dispersion as a function of the number of electrons per bit (Figure 7). As the number of electrons per bit N is reduced, we measured an 13/23 increase of the retention time relative dispersion, with a factor ~2 when we pass from 100 to 10 electrons. Once again, the analytical models show good agreement with the experimental data, which definitely proves the validity of our theory. It is important to highlight that the model underestimates the experimental dispersion, which can be partly explained by the fact that it does not take into account the dispersion of the threshold voltage after programming. This dispersion is even more pronounced in the case of Si-nc memories, due to the dispersion of the value of dVth from one Si-nc to the other [13, 17]. Finally, one should note that poly-Si and Si-nc based memories follow comparable dispersion laws, in an experimental and a theoretical way. In conclusions, at the first order, the retention time relative dispersion simply depends on the number of electrons per bit, and is lowly dependant on the nature of the floating gate. One should also note that while the increasing of the measurement temperature accelerates the mean retention time, the retention time relative dispersion shows no temperature dependence. Indeed, experiments were performed on the same memory sample at 30°C and at 200°C, and it was found that the retention time relative dispersion remained unchanged, being respectively equal to 52% and 49%. Similarly, the dispersion of the threshold voltage shift after programming was studied for Sinc memories. Fig.8 shows the evolution of the threshold voltage at constant drain current as a function of the programming gate voltage for three subsequent runs on a single device. It appears that the floating gate charging is made electron by electron as clearly evidenced by the threshold voltage discontinuities, and that for similar writing conditions, the written threshold voltage can be different from one run to the other, which illustrates the stochastic nature of the FG charging. On fig.9, we represented the evolution of the dispersion of the written threshold voltage as a function of the number of electrons per bit. Different devices with various W and L have been tested to that extent. For each device, the writing conditions have been set in order to have a 14/23 Vth of 600mV. Thus each memory device corresponds to a number of electrons per bit depending on the dimensions of the active area. We can observe on this figure that the dispersion increases as the number of electrons per bit is reduced. For the smallest tested device (W=L=30nm), the dispersion reaches 50mV, while it is smaller than 15mV for the largest device (W=80nm L=200nm), which corresponds to 2% of Vth. We also represented on this plot the theoretical curve corresponding to TW/C~2. We can see that this figure allows to explain correctly the experimental data. An example of Vth distribution after programming, extracted from repeated write/erase cycles is represented on the inset of fig.9 for a device with W=30nm L=60nm. We estimated the number of electrons per bit to ~40 for these dimensions. The theoretical distribution is also represented and matches correctly the experimental data. Finally, we can conclude that the Vth dispersion is not critical in our case and that it is much smaller than the mean value of 600mV, even for the smallest tested devices where it is inferior to 10%. IV. DISCUSSIONS AND EXTRAPOLATIONS We will now discuss the main consequences of these intrinsic dispersions on future memory generations. Concerning the uncertainty on the programming window Vth of few electron memories, we argue that dispersion could be reduced by maximizing the ratio T W/C (as it is the case in current technologies: C~10-100ps; the writing time TW~1µs). Moreover, in the case of polySi FG, the Vth dispersion can be limited by using a verify operation, where the completion of the write operation is checked by reading out the data [10]. Note also that a Vth selfsaturation is achieved in the case of Si-nc memories, due to the limited number of storage nodes (Si-ncs). In conclusions, the relative dispersion of Vth becomes negligible, even in few electron memories, when TW~10C. 15/23 It follows that, in few electron memories, the operation margins in terms of Vth will be less critical than in terms of retention time. Moreover, as shown in figure 3, the distribution tails of the corresponding retention time cumulative probability allow us to evaluate the memory failure time (defined as the retention time of one erratic bit in a 1 Megabit or a 1 Gigabit array). Figure 10 shows the evolution of this failure time, as a function of the number N of electrons per bit. In this case, the failure criterion is defined as the retention time of 1 bit over a one Gigabit array, and the retention criterion corresponds to 20% of charge loss. It appears that the failure time decrease can become relevant when the number of electrons per bit is reduced, and becomes really critical in few electron memories. We can now focus on NAND technology, which as already said is more critical in terms of number of electrons per bit than NOR memories. If we consider the 90nm Flash NAND technology node, a threshold voltage shift of 3V corresponds to about 1000 electrons per bit. Thus, in this case, the retention time of one erratic bit over 1Gigabit will be equal to 6.5 years. Now, for the 35nm Flash NAND technology node, which corresponds to about 200 electrons per bit, the retention time of one erratic bit in a Gigabit matrix decreases drastically to 3.3 years, which could be indeed very critical. Moreover, ITRS 2003 predicts as soon as year 2005 the introduction of multi-bits per cell memories [7]. Obviously, in these technologies, the retention time operation margins will be further reduced, the number of electrons per bit being decreased by 2bit/cell-1. Figure 11 shows the retention time of 1 bit/1Gigabit as a function of the NAND memory node, for 1 bit per cell and 2 bits per cell memory technologies. This plot illustrates that in future generations the use of multilevel memories (reducing the number of electrons per bit) will decrease even more critically the failure time of high density memory arrays. Thus for the 35nm memory node, the introduction of 2 bits per cell induces a reduction of the failure time from 3.3 years to one year. 16/23 Retention time dispersion issues in ultra-scaled devices could be compensated by increasing the operation window (i.e. the number of electrons/bit), with a trade-off in terms of writing and erasing voltages/times. In the case of Si-nc memories, where the number of electrons/bit is further reduced and self-limited, solutions to increase the mean retention time, as the engineering of the tunnel barrier [18], should be introduced. V. CONCLUSIONS The intrinsic reliability concerns of few electron memories have been quantified by means of original models and experiments. We have demonstrated that the working of ultra-scaled memories (down to W=L=30nm) is controlled by single electron events. The stochastic nature of electrons that becomes prominent in few electron structures leads to an intrinsic dispersion of both retention time and memory threshold voltage shift after programming. This constitutes a theoretical limit of floating gate memory devices. We also argue that the most limiting parameter is the retention time dispersion. Indeed, we estimate that the programming window dispersion due to single electron phenomena is not critical in current and future technologies, and can be limited by increasing the writing time or bias. On the other hand, the retention time dispersion has crucial reliability implications, and significantly reduces the reliability of high density memory arrays of incoming generations. APPENDIX In this section, we present the demonstration of Eq.(4), which calculates the retention time TR probability density of a memory device with a continuous FG. We consider that the FG contains N electrons. Based on our experimental results, we assume that the emission of one electron from the FG follows an exponential distribution law, with a time constant di. Thus 17/23 the probability density of the discharging of the ith electron is 1/di.exp(-t/di). We also consider that the retention time is reached when k electrons are emitted from the FG. We should now calculate the time when the kth electron is emitted from the FG. In order to understand the reasoning followed in this model, we will treat in a first step the case of a memory with 2 electrons in the FG (N=k=2). In this system, the discharging time constant of the first electron (/ the second electron) is d1 (/ d2). The probability that the 1st electron is emitted at a time t1 and the 2nd at a time t (namely the retention time) is given by: t dt t t1 dt 1 exp 1 exp d1 d1 d 2 d2 (13) Now we have to consider that t1, the discharging time of the 1st electron, can take any value between 0 and t. We integrate the previous term between 0 and t and we obtain the retention time probability density for N=k=2: t 1 t t1 1 dt 1 exp 1 exp t1 0 d1 d1 d 2 d2 pTR t, k 2 TR (14) We can now extend this result to the case of N electrons in the FG, with the electrons discharging time constants respectively equal to d1, ...dk. The probability that the k electrons are emitted at times t1, t2, ... tk is given by: t 1 t t k 2 1 exp 1 exp k 1 d d d1 d k 1 1 k 1 1 TR t k 1 dt k 1 ...dt 1 exp d dk k (15) We successively integrate this expression over tk-1 varying between tk-1 and TR; tk-2 varying between tk-3 and TR; ... and t1 varying between 0 and TR, what gives rise to Eq.(4). 18/23 REFERENCES [1] Y.-S. Yim, K.-S. Shim, S.-H. Hur, J.-D. Lee, I.-G. Baik, H.-S. Kim, S.-J. Chai, E.-Y. Choi, M.-C. Park, D.-S. Eun, S.-B. Lee, H.-J. Lim, S.-P. Youn, S.-H. Lee, T.-J. Kim, H.-S. Kim, K.-C. Park, K.-N. Kim, “70nm NAND Flash technology with 0.025µm2 Cell Size for 4Gb Flash Memory”, IEDM 2003 Tech. Dig, pp.819-822. [2] J.-H. Park, S.-H. Hur, J.-H. Lee, J.-T. Park, J.-S. Sel, J.-W. Kim, S.-B. Song, J.-Y. Lee, J.H. Lee, S.-J. Son, Y.-S. Kim, M.-C. Park, S.-J. Chai, J.-D. Choi, U-I. Chung, J.-T. Moon, K.T. Kim, K. Kim, B.-I. Ryu, “8Gb MLC (Multi-Level Cell) NAND Flash Memory using 63nm Process Technology”, IEDM 2004 Tech. Dig, pp.873-876. [3] C. Park, S. Sim, J. Han, C. Jeong, Y. Jang, J. Park, J. Kim, K. Park, K. Kim, “A 70nm NOR Flash Technology with 0.049µm2 Cell Size”, Proc. of VLSI 2004, pp.238-239. [4] S. Lai, “Non Volatile Memories: a look into the future”, MIT-Standford-UC Berkeley Nanotechnology Forum, 26/02/2004. [5] H. Silva, M. K. Kim, A. Kumar, U. Avci, S. Tiwari, “Few Electron Memories: Finding the Compromise between Performance, Variability and Manufacturability at the Nano-Scale”, IEDM 2003 Tech. Dig., pp.271-274. [6] G.Atwood et al., “StrataFlashTM”, Intel Techn. Journ., Q4-97. [7] B.Cambou, “MirrorbitTM”, http://www.spansion.com/overview. 19/23 [8] B. De Salvo, C. Gerardi, S. Lombardo, T. Baron, L. Perniola, D. Mariolle, P. Mur, A. Toffoli, M. Gely, M. N. Semeria, S. Deleonibus, G. Ammendola, V. Ancarani, M. Melanotte, R. Bez, L. Baldi, D. Corso, I. Crupi, R. A. Puglisi, G. Nicotra, E. Rimini, F. Mazen, G. Ghibaudo, G. Pananakakis, C. Monzio Compagnioni, D. Ielmini, A. Lacaita, A. Spinelli, Y. M. Wan, K. van der Jeugd, “How far will Silicon nanocrystals push the scaling limits of NVMs technologies?”, IEDM 2003 Tech. Dig., pp.597-600. [9] R. Muralidhar, R. F. Steimle, M. Sadd, R. Rao, C. T. Swift, E. J. Prinz, J. Yater, L. Grieve, K. Harber, B. Hradsky, S. Straub, B. Acred, W. Paulson, W. Chen, L. Parker, S. G. H. Anderson, M. Rossow, T. Merchant, M. Paransky, T. Huynh, D. Hadad, Ko-Min Chang, B. E. White Jr., “A 6V Embedded 90nm Silicon Nanocrystal Nonvolatile Memory”, IEDM 2003 Tech. Dig., pp.601-604. [10] K. Yano, T. Ishii, T. Sano, T. Mine, F. Murai, T. Hashimoto, T. Kobayashi, T. Kure, K. Seki, “Single-Electron Memory for Giga-to-Tera Bit Storage”, Proc. of the IEEE, 87, 4, pp.633-651, 1999. [11] K. K. Likharev, “Single-Electron Devices and their Aplications”, Proc. of the IEEE, 87, 4, pp.606-632, 1999. [12] P. Coli, G. Iannaccone, “Evaluation of performance and perspectives of nanocrystal flash memories based on 3D quantum modeling”, Proceedings of the 2001 1st IEEE Conference on Nanotechnology, pp.140-145, 2001. 20/23 [13] G. Molas, B. De Salvo, G. Ghibaudo, D. Mariolle, A. Toffoli, N. Buffet, R. Puglisi, S. Lombardo, S. Deleonibus, “Single Electron Effects and Structural Effects in Ultra-scaled Silicon Nano-crystal Floating-gate Memories”, IEEE Trans. on Nanotech., 3, 1, 2004. [14] M. Kirton, M. J. Uren, “Noise in solid-state microstructures: A new perspective on individual defects, interface states and low-frequency (1/f) noise”, Adv. Phys., 38, 4, pp.367468, 1989. [15] M. Saitoh, E. Nagata, T. Hiramoto, “Large memory window and long charge-retention time in ultranarrow-channel silicon floating-dot memory”, Appl., Phys. Lett., 82, 11, pp.17871789, 2003. [16] G. Molas, D. Deleruyelle, B. De Salvo, G. Ghibaudo, M. Gely, S. Jacob, D. Lafond, S. Deleonibus, “Impact of few electron phenomena on floating-gate memory reliability”, IEDM 2004 Tech. Dig.,pp.877-880. [17] M. Saitoh, E. Nagata, T. Hiramoto, “Effects of ultra-narrow channel on characteristics of MOSFET memory witht silicon nanocristal floating gates”, IEDM 2002 Tech. Dig., pp.181184. [18] S. J. Baik, S. Choi, U-I. Chung, J. T. Moon, “High Speed and Nonvolatile Si Nanocrystal Memory for Scaled Flash Technology using Highly Field-Sensitive Tunnel Barrier”, IEDM 2003 Tech. Dig., pp.545-548. 21/23 FIGURE CAPTIONS Figure 1: number of electrons representing one bit as a function of the Flash technology node according to the ITRS 2003 edition. Figure 2: probability density of the retention time TR for memories with reduced number of electrons per bit, N (eq. 5). The mean TR is fixed at 10 years. Figure 3: cumulative probability of retention time TR (from Fig.2) of memories with reduced number of electrons per bit, N. Figure 4: histogram of the programming window Vth at a writing time TW (= C, the electron capture time constant) for three Si-nc memories with decreasing numbers of Si-ncs, N, in the active area. Figure 5: schematic views and TEM cross sections of (a) a Poly-Si FG memory (device A) and (b) a Si-nc memory (device B). Figure 6: experimental retention characteristics of two devices of type A. The corresponding distributions of the retention time (extracted from ~100 measurements) are shown in the insets and compared to model. The number of electrons per bit N used in model has been extracted as Vth-max/dVth (i.e. N=21, dVth =6mV, and N=346, dVth=1.5mV, respectively). Figure 7: experimental and theoretical evolution of the relative dispersion of the retention time as a function of the number of electrons per bit. Data from devices of type A and B (with 22/23 different W, L and Vth-max) are extracted from measurements similar to the ones of Fig.6. Models, based on Eq.5 and Eq.7, are for retention time @ 50% of charge loss. Figure 8: writing characteristics for three successive runs on a single memory device (W=50nm; L=30nm) for a programming time of 1s. Figure 9: dispersion of the written threshold voltage as a function of the number of electrons per bit. Each point corresponds to a memory device with different W and L. Inset: distribution of the threshold voltage shift for successive write/erase measurements for a memory device with W=30nm; L=60nm. The writing conditions are11V/1s. Figure 10: calculated failure time (i.e. retention time of one bit over 1Gigabit array) due to single electron discharging of the FG, plotted as a function of the number of electrons per bit. The mean retention time is 10ys for each cell of the array. Figure 11: calculated failure time (i.e. retention time of one bit over 1Gigabit array) due to single electron discharging of the FG, plotted as a function of the technological node, for 1bit/cell and 2bits/cell memory devices. 23/23