LC101

advertisement

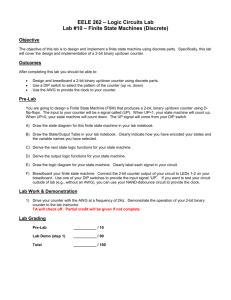

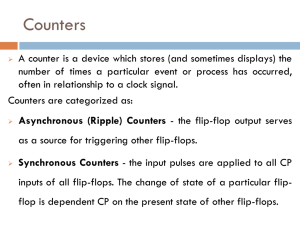

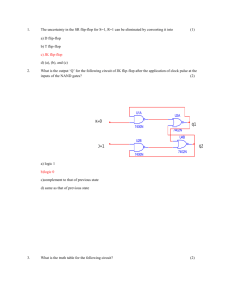

10. Simple Sequential Logic Circuits 10. SIMPLE SEQUENTIAL LOGIC CIRCUITS In this chapter we will form rather simple asynchronous and synchronous sequential logic circuits. The knowledge how various latches and flip-flops operate, and knowledge about combinational logic design is sufficient for this purpose. The next chapter will be devoted for asynchronous sequential logic design, and it demands the knowledge of some specific design rules and methods. 10.1. Registers The registers are devices for writing, short storage, processing, and reading of information. The registers are formed from memory storage devices, usually they are gated D latches or flip-flops, and from control circuit, usually it is a combinational logic circuit. A control circuit – inputs data to the register and outputs data from it; – shifts data along the register; – makes data processing. The registers are the simplest microprocessors. According the way of data input and the way of data output the registers are classified as – parallel or storage registers; – series or shift registers; – universal registers. According their structure the registers are classified as single-cycle and two-cycle. One memory cell of two-cycle register consists from two memory storage devices – two gated D latches. During the first cycle the data is written to the first D latch. During the second cycle the data is shifted from the first D latch to the second D latch – in this way the first D latch gets ready to data receiving during the next cycle. As a matter of fact a single-cycle register is the same as a two-cycle register, but in appearance it seems quite different. The memory cell of a single-cycle register consists from one master-slave or edge-triggered flip-flop, but we know that it is made from two connected in series gated latches. The inverter in the control signal circuit of such flip-flop creates the control signal that is equivalent to two control signals in two control lines of two-cycle register. 99 10. Simple Sequential Logic Circuits 10.1.1. Parallel Registers Parallel register of n bit's can be formed from n gated D latches. The D inputs of D latches are data inputs of register, Q outputs of latches are data outputs of register. The functional diagram (a) and the graphic symbol (b) of a 4 bit's parallel register is shown on the picture. When there is an enable pulse in a control line C the data in parallel (at the same time) are written to all D gated latches. D1 Q1 D2 Q2 D3 Q3 D4 Q4 D D D D D C C C C RG 1 2 3 4 Q 1 2 3 4 C C a b There are parallel registers with more complicated control circuit. Usually the control circuit is repeated in every memory cell of a register. One memory storage device with its control circuit and graphic symbol of Di Qi a 4 bit's parallel register with such D RG Q 1 memory cell is shown on the next 2 1 S picture. 3 1 4 2 The order Clear comes in line R C 3 CLR, the order Write – in line C, 4 RD C Read in direct form – in line RD, and RD CLR read complemented data – in line R RD RD. RD When an information is written to parallel register, it can be read many times until the new information is not written. 10.1.2. Shift Registers There are direct, reversible, and universal or bi-directional shift or serial registers. The data to the input of a direct shift register are written in a consecutive order, a cycle after a cycle; they are shifted along the register from its input to its output, and they occur in the output of the register in the same consecutive order as they came to its input. The most simple shift register is a two-cycle register with two gated D latches in every memory cell. 100 10. Simple Sequential Logic Circuits T1 Di+n T1 T2 T2 Tn Tn D D D D D D C C C C C C Di C1 C2 With first enable pulse in line C1 an information a1 is written to the latch T1. With the first enable pulse in line C2 an information a1 is shifted to the latch T1'. With the second enable pulse in line C1 an information a2 is written to the latch T1 C1 C2 D T1 T1 T2 T2 a1 a1 and an information a1 is written to the latch T2. With the 1 1 a1 second enable pulse in line C2 an information a2 is shifted to the latch T1' and information a2 – to the latch T2'. This 2 2 a2 a2 a2 a1 a1 consecutive shift of information along a direct two-cycle shift register is shown on the picture. One memory cell of one-cycle shift register with special control circuit illustrates the possibility to form a universal or bi-directional shift Q Qi Qi–1 Ti i+1 register. S The shift registers can fulfill many different func 1 D tions. Remember, that shift of binary digit for n bits to n right side means a division to 2 ; shift of binary digit for C n bits to left side means a multiplication with 2n. Shift register with outputs from each memory cell is a serial R R code converter to a parallel code. When information is S written to the memory cells of a shift register in parallel C way, and is red from the output of the shift register in series, we have a parallel code converter to serial code. Shift register with output connected to its input is a generator of a periodical sequence of pulses. Shift register of n bit's is a device for delay of pulses till n cycles. The imagination of the designer only can limit the fields of application of registers. 10.2. Counters The counter is a device that counts the pulses in its input and gives the result in a definite for this counter code: in a binary code, in a decimal code, or in a binary-decimal code. 10.2.1. Asynchronous Binary Counters Asynchronous or serial binary counters are formed as a cascade connection of the counting T flip-flops. The counting T flip-flop is a master-slave J-K flip-flop with inputs J = K = T = 1. It 101 10. Simple Sequential Logic Circuits means that counting T flip-flop has only one input C and it counts the pulses that are coming to this input. The counter from n counting T flip-flops can count till 2n. The simplest asynchronous binary counter is an adding or total counter. Every pulse in the input of this counter enlarges its reading by one. The counter formed from 3 T flip-flops is shown on the picture. It can count till 2n 8. The timing diagrams in the next a2 a0 a1 T1 T2 T3 picture explain the operation of the counter. PR Remember that T master-slave flip-flop togQ3 Q1 Q2 S S S gles with end of pulse in its control input C. IN The table of adding binary counter is C C C filled in according the timing diagrams: the values of bit's a0, a1, and a2 after every pulse in an input C. CLR 1 2 3 4 5 6 7 8 9 10 IN m 0 1 2 3 4 5 6 7 8 Q1= a0 Q2= a1 Q3= a2 Q3 = a0 0 0 0 0 1 1 1 1 0 Q2 = a1 0 0 1 1 0 0 1 1 0 Q1 = a2 0 1 0 1 0 1 0 1 0 t Every pulse in the input of subtracting or counting-down counter decreases its reading by one. The counter starts from the maximum reading that is set with preset signal for all flipflops. The counter gets subtracting when an a2 a1 a0 input of every next flip-flop is connected to T2 T2 T1 an inverted output of the previous flip-flop. Q2 Q3 IN Q1 Notice that the outputs of the subtracting C C C counter are direct outputs of every latch. R CLR R R Example 10.1 Draw the timing diagrams of the subtracting counter and fill in its table. The universal or bi-directional counter enlarges or decreases its reading depending on the line – C+1 or C–1 – in which the counted pulse acts. The pulses can not act in both lines at the same time. 102 10. Simple Sequential Logic Circuits 10.2.2. Synchronous Binary Counters The disadvantage of asynchronous counter – delay of signals in a serial circuit of flip-flops. In synchronous or parallel binary counter all flip-flops toggle at the same moment. One can see the idea of synchronous counter in the structure of each positional number system: the number in the higher position occurs when all less significant positions are fulfilled. We write 100 after 99 in decimal, 100000 after 011111 in binary. The conclusion is such that counted pulse must come to all flip-flops of the parallel counter at the same moment, but this pulse can toggle only the flip-flops, that have a permission to toggle – enable signal of logic 1 from all less significant bits. The functional diagram of a 4 bit synchronous binary counter, formed from master-slave counting T flip-flops with additional enable inputs, is shown on the picture. a0 a1 E C Q1 E T4 T3 T2 T1 a3 a2 Q2 C E C Q3 E Q4 C IN Example 10.2 Draw a logic diagram of master-slave counting T flip-flop with additional enable input. Example 10.3 Correct the functional diagram of a 4 bit synchronous binary counter so that the delay time in the counter would not increase with increasing the number of bits. 10.2.3. BCD and Decimal Asynchronous Counters The binary counters are indispensable, when the results of counting are processing by an electronic device. A person prefers the results in decimal number system. BCD counter is an intermediate version between binary and decimal counter. It counts in a binary code the repeated sequence of ten decimal symbols: 0, 1, 2, 3, ..., 8, 9, 0, 1, 2, ... We know that a binary counter from four flip-flops can count from 0 till 15. BCD counter from four flip-flops has a circuit, which recognizes the state "9" and generates the reset pulse for flip-flops of the counter. This pulse clears the counter to state "0" and from this state the counting is going on. At the same time the reset pulse occurs in the output of counter overflow (output "10"). The signal in this output is the input signal of other BCD counter in higher decimal position. The code converter "From BCD to Decimal" in the outputs a0, a1, a2 and a3 changes the BCD counter to decimal counter. 103 10. Simple Sequential Logic Circuits a1 a0 T2 T1 IN T3 Q2 Q1 a3 a2 T4 Q3 Q4 C C C C R R R R T5 10 C CLR 1 R Example 10.4 Draw a functional diagram of the asynchronous counter that counts till 99. CONTROL QUESTIONS AND PROBLEMS 10.1. Registers 10.1.1. Formulate a definition of a register. 10.1.2. Explain a classification of registers. 10.1.3. Draw a circuit of 4 bits parallel register with data inputs D1, D2, D3, and D4, with control input C, with input CLR, and with inputs WR and RD. 10.1.4. Draw a circuit of 4 bits shift register with data input D, with control input C, with input CLR, and with inputs WR and RD. 10.1.5. Draw a circuit of 3 bits universal register with data inputs D1, D2, D3, with control input C, with input CLR, and with inputs WR1, WR2, WR3, and outputs Q1, Q2, Q3. 10.2. Counters 10.2.1. Explain the properties of asynchronous and synchronous counters. 10.2.2. Draw a circuit of asynchronous 4 binary bits total counter with edge-triggered D flip-flops. 10.2.3. Draw a circuit of asynchronous 3 binary bits counting-down counter with universal JK MS type flipflops. 10.2.4. Draw a circuit of asynchronous 4 binary bits bi-directional counter. 10.2.5. Draw a circuit of asynchronous decimal counter from 0 till 9 with decoder from "4 to 7". 104