Supplemental Material_revised

advertisement

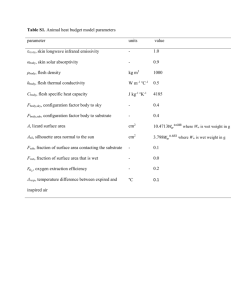

Supplemental Material Flexible Semi-Around Gate Silicon Nanowire Tunnel Transistors with a Sub-kT/q Switch Myeongwon Lee, Youngin Jeon, Minsuk Kim, and Sangsig Kim* Department of Electrical Engineering, Korea University, Seoul 136-713, Republic of Korea KEYWORDS. Silicon nanowire, subthreshold swing, band-to-band tunneling, tunnel field-effect transistor, flexible device, sub-kBT/q switch. AUTHOR INFORMATION Corresponding Author *E-mail: sangsig@korea.ac.kr 1 Fabrication of p+-i-n+ SiNWs via CMOS compatible top-down process Firstly, a 10-nm-thick pad layer of oxide SiO2 was grown on the surface of a Si substrate. The pad oxide layer serves as a stress relief layer to diminish the stress-induced dislocations that a nitride film exerts in the Si surface. And a 150-nm-thick Si3N4 film was then deposited by LPCVD. The role of this thin nitride film is a hard mask layer for etching the Si substrate, a hard mask layer for protecting the SiNWs from the wet chemical solution, and an oxygen diffusion barrier during thermal oxidation for reducing the dimension of the SiNWs. Next, the 400-nmwidth Si active lines were defined along the [110] direction by photolithography. After the plasma etching of the pad oxide layer and the nitride film followed by the stripping of the photoresist, the Si substrate was etched anisotropically until the desired trench depth was reached (Figure S1(a)). Next, crystallographic wet etching in tetramethyl ammonium hydroxide (TMAH, (CH3)4NOH; 25% diluted in water) solution was performed to obtain the inverted triangle-shaped Si lines (Figure S1(b)) This crystal orientation-dependent wet etch process was based on the fact that the (111) plane has only one dangling bond per unit cell while both the (100) and (110) planes have two dangling bonds per unit cell. Following a formation of the inverted triangleshaped Si lines through the dry and wet etching, the thermal oxidation of the Si lines was carried out in a wet ambient to reduce the size of the SiNWs (Figure S1(c)). Note that the thermal oxidation condition was 1050 ˚C for 350 minutes. Also, the Si necks of the SiNWs were thoroughly oxidized so that the SiNWs were electrically isolated from the Si substrate. Following a formation of the SiNWs, the nitride film was completely stripped in hot phosphoric acid at a temperature of 160 ˚C. In order to make the source and drain regions of the SiNWs doped, As+ ions with a dose of 3×1015 cm-2 and BF2+ ions with a dose of 5×1015 cm-2 were implanted as nand p-type dopants at ion energies of 50/120 keV and 30/80 keV, respectively. Then, the Si 2 substrate containing the SiNWs was annealed at 1000 ˚C for 5 s in a nitrogen ambient in order to activate the implanted dopants in the body of the SiNWs (Figure S1(d)). Thereafter, the SiNWs were released from the Si substrate by dipping the wafer in buffered oxide etchant (BOE) solution to remove the surrounding oxide layers thoroughly (Figure S1e). In order to reduce a diameter of the SiNW channels efficiently, the p+-i-n+ SiNWs were then selectively-etched in TMAH solution, where the doped-SiNW etching rate, R, goes as Ri >> Rn+ > Rp+ (Figure S1f). After the selective etching of SiNW channel regions, the diameter of SiNW channels is almost ~20 nm. Figure S1. Key process steps to generate selectively thinned p+-i-n+ SiNWs from a Si substrate. (a) Si trench etching with an oxide/nitride stack defining 400-nm-wide active Si lines. (b) Crystallographic wet etching in TMAH ((CH3)4NOH; 25% diluted in water) solution to generate triangular Si wires. (c) Thermal oxidation of the Si wires to reduce the size of SiNWs. (d) Masked source and drain implantations with As+ and BF2+ ions for n- and p-type dopants, respectively, followed by RTA annealing. (e) Release of the SiNWs via wet chemical etching in BOE solution. (f) Selective wet etching in TMAH solution to reduce a diameter of the SiNW 3 channels efficiently. Note that to provide clarity, crystalline connections to the supporting posts at the end of the SiNWs are not shown. The doping profiles of p+-i-n+ SiNWs in this study were analyzed using a two-dimensional process simulator (Silvaco Athena). As shown in Figure S2, It was confirmed that the boron and arsenic concentrations in the source and drain regions are approximately at the 1020 ~1021 cm-3 levels, and the ion penetration depth is ~150 nm, which is large enough to cover the entire SiNW height. Therefore, the ion implatation doping method is one of the appropriate ways to control the profile for doping in 3D structures like NWs. Figure S2. Simulated analysis for the arsenic and boron profiles in the SiNWs after two-step ion implantations (BF2+ 5×1015 cm-2 at 30/80 keV and As+ 3×1015 cm-2 at 50/120 keV, respectively) and RTA at 1050˚C for 5 s. The simulation was performed with using a two-dimensional process simulator (Silvaco Athena). Next, the channel and source/drain junction profiles of p+-i-n+ SiNWs were also analyzed via a two-dimensional process simulator. As shown in Figure S3, our simulation results show the abruptness of junction profiles for our present p+-i-n+ SiNWs; the SiNW shows the abrupt 4 change of the doping concentrations from abrupt degenerate source junction at the source/drainchannel interface. It means that p+-i-n+ SiNWs have abrupt junction profiles at source/drain and channel junction. Figure S3. Simulation analysis for the channel and source/drain junction profiles of SiNWs. The simulation was performed using a two-dimensional process simulator (Silvaco Athena). 5 Transfer method of p+-i-n+ SiNWs onto a flexible plastic substrate Figure S4. Method for transferring the as-aligned SiNWs from a Si substrate to a plastic substrate. (a) Lamination of UV-curable resin (Q-sys, NIR 01) by a spin coating process. (b) Contacting of the Si substrate containing the SiNWs with the plastic substrate. (c) Hardening of the resin by UV light exposure and separating the Si substrate from the plastic substrate. (d) Removal of the resin by immersing it in ethanol solution, leaving the SiNWs on the plastic substrate. 6