docx - digsys.upc.edu

EX 5 DIGITAL ELECTRONICS (GROUP 1BM2) G________

After completing the task and studying Units 2.1, 2.2, 2.3 and 2.4, students will be able to (check all that apply):

Explain the concept of memory in digital systems and why we talk about sequential systems for introducing the time variable. What is the meaning of storing or saving a bit of information?

Describe the characteristics of basic asynchronous 1-bit memory cells or latches SR and its variations D, JK and T with enable E input using a function table

Plot a timing-diagram for demonstrating the mode of operation of the basic latch cells

Describe the latch cell using the state diagram tool

Design latches and simple sequential systems using the direct method based on Chapter 1 techniques

Design timers and clocks based on the 555 integrated circuit

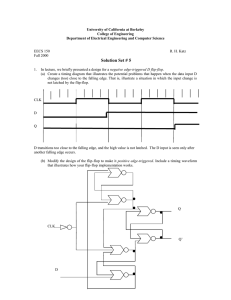

Explain using time-diagrams the notion of synchronicity in flip-flop cells

Design flip-flops and other simple synchronous systems using the canonical method

Produce a written solution for the exercise using the instructions from: http://epsc.upc.edu/projectes/ed/unitats/unitat_1_1/Criteris_Correccio_Exercici.pdf

Work cooperatively in a team of 3 members using the method described in: http://epsc.upc.edu/projectes/ed/problemes/metode_resolucio_cooperativa_recomanat.pdf

-

-

Write down the most significative doubts or questions you have had while or after completing the task:

-

-

-

-

-

STATEMENT:

and fully agree with the contents (i.e., results, conclusions, analyses, simulations) of this document, and (3) acknowledged by name anyone outside this group who assisted this learning team or any individual member in completing this document.

1

Today’s date: __________________

Active members

(1) ___________________________

(2) ___________________________

(3) ___________________________

Roles: (reporter, simulator, etc.)

_______________

_______________

_______________

Acknowledgement of individual(s) who assisted this group in completing this document:

(1) _______________________

(2) _______________________

Study time

(in hours)

Group work Sessions TGA,

TGB

Individual

Sessions

TGC

Student 1

Student 2

Student 3

1

Which is the easiest way to control a simple motor?

Design a simple asynchronous sequential system by direct method: an ON/OFF motor control system as shown

in Fig. 1. Verify your design in Proteus-VSM downloading the project file from the ED web page.

VCC

MOTOR CONTROL SYSTEM

D4

1N4148

RL1

4V

RUN

B1

120V

RUN

STOP Z

R2

1k

Q1

BC547

R1

12k

DC-MOTOR

120V

STOP

D1

ON-OFF-CONTROL

GND

RA

100MEG

Fig. 1 Schematic of the control system to drive a high power motor load a) Specifications: function table; state diagram; timing diagram.

Run Stop

0

0

0

1

Z

+

Z

0

Function

Do nothing

Stop (OFF)

2

1

1

0

1

1

Z

Run (ON)

Do nothing b) General architecture using direct method and design of the combinational system using Chapter 1 methods: a.

Using the method of decoders b.

Using the method of multiplexers c.

Using a canonical structure NOT-AND-OR d.

Using NOR c) Proteus-VSM schematic capture and verification

Limiting the number of the motor’s ON/OFF cycles using a timer

2 Produce a timer to connect to the previous control system using the classic 555 integrated circuit. Its mission will be to prevent activating the motor (RUN) before that a time of 12 s has elapsed. Therefore, only 4 cycles of

RUN/STOP will be permitted per minute. a.

Following the explanations in the didactical Unit 2.4,

analyse the circuit in Fig. 2. Deduce the waveforms

and the design equation which gives T

0

= f(R1, C1)

555 Timer delay = K · Rx · Cx

CHIP 555 constant K = 1.1

R2

10k

R1

4

R

VCC

Q

DC

U1

3

7

?

5

CV

+

C1

2

TR TH

6

555

TRIGGER b.

Connect the timer module to the motor control system using logic

Fig. 2 A 555-based timer

3

Controlling the motor by means of a one-button remote control

Design the block diagram of an infrared emitter-receiver which has to be able to interface the previous motor activator system by means of a single pushbutton. Use your imagination, ask for information, surf the web, and discuss with your colleagues.

3

4

Cells for storing bits.....the basic brick of any sequential system and everything in electronics!

Print and study the concept maps of the didactical units: 2.2, 1-bit asynchronous memory cells, latches; and 2.3, synchronous memory cells, flip-flops; Write down your doubts in a sheet of paper and try to answer them with your

excitation waveforms are applied at the inputs.

S

R

Q

E

D

Q

CLK

CD

D

Q t

D

E

Latch

D

Q

Q_L

(use the transparent D-type latch function table) t

(use the RS latch function table)

Fig. 3 D-type (data) and RS latches

S

R

Latch

RS

Q

Q_L

(SD = 0) t

(use the D-type flip-flop function table)

CLK

D

SD

Q

JK-FF

Q_L

CD

K

Q

SD

CLK

J t

(use the JK flip-flop function table)

CLK

J

SD

Q

JK-FF

K

Q_L

CD

(CD = 0)

Fig. 4 JK and D flip-flops

6

5

4 Design an internal circuit using the direct method for all four 1-bit memory cells and demonstrate their functioning by a simulation in Proteus. a.

Function table and symbol b.

State diagram and internal architecture for direct method c.

Truth table for the design if the combinational block d.

Circuit capture in Proteus and simulation for verification

Design an internal circuit using the canonical method for all the four 1-bit memory cells if an RS flip-flop is used as the state register. Demonstrate their functioning by a simulation in Proteus. a.

Specs: function table, symbol, state diagram, time diagram b.

Canonical internal architecture using RS flip-flop. Transforming a RS latch with enable input to obtain a RS flip-flop c.

Code the states. In this case, trivially state reset (Q = 0), and set (Q = 1) d.

Draw the state register e.

Design the CS2 f.

Design the CS1 using transition table and design table for the RS flip-flop g.

And capture your schematic and demonstrate the way it works

Design an 8-bit wide synchronous D-type flip-flop with enable using JK flip-flops as the state register for each 1-

3

4

7

8

13

14

17

18

D1

D2

D3

D4

D5

D6

D7

D8

Q1

Q2

Q3

Q4

Q5

Q6

Q7

Q8

2

5

6

9

12

15

16

19

11

1

CLK

E

74LS377

Fig. 5 Example of a commercial chip D-type flip-flop with enable

7 And finally, use the 555 to build a rectangular wave of 5 V and 100 KHz to be used as the clock synchronization signal for flip-flops. Use the Proteus oscilloscope to demonstrate your design.

5

6

SD

CLK

J

K

Q

Fig. 6 Example of a square wave CLK signal t

DIGITAL ELECTRONICS

Working plan

1

for solving the exercise EX 5

G________

Explain succinctly how the cooperative group has organize the realization of the exercise: i.e., which has been your working plan; in which way has you divided the task fairly so that more or less all of you are doing a similar amount of work; how have you learned each other’s materials; what has been worked out in class time (sessions A and B) and what has been resolved in sessions C; and so on... white down also your impressions or opinions about the subject and how your group work is going 2 ...

1 This document, filled before delivering the exercise, will be included in the group learning portfolio

2 Check similar documents in http://epsc.upc.edu/projectes/ed/unitats/ED_05-06_Q1_Autoavaluacio_Grup_Base.pdf

, and http://epsc.upc.edu/projectes/ed/unitats/que_va_malament_al_grup.pdf

7

8

--------------------------------- -------------------------------------- ---------------------------------------

Active members’ signatures