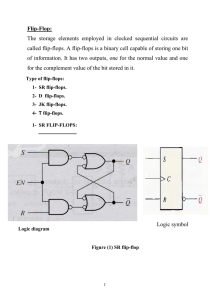

Flip-Flops

Lecture 13

Flip-Flops

Section 5.4

Schedule

3/10 Monday Latches (1)

3/12 Wednesday Flip-flops

3/13 Thursday

3/17 Monday

Flip-flops, D-latch

Spring break

3/19 Wednesday Spring break

3/20 Thursday Spring break

3/24 Monday Analysis of clocked sequential circuit (1)

3/26 Wednesday Analysis of clocked sequential circuit (2)

3/27 Thursday Clocked sequential circuit

5.1-5.3

5.4

5.5

5.5

Please bring a functional random number generator to class on Thursday

(3/13).

• Review

– D latch

• Applications

• Flip-flops

– D flip-flops

• Reset

– JK flip-flops

– T flip-flop

Outline

D Latch

Using a Latch as a Memory

Element

Caution for a D latch: once a clock enables a D latch, the output changes as soon as the input changes – this is not desirable if you do not want the output to change continuously and all the latches use a common clock.

Uses of Flip-flops

D Flip-Flop

Negative Edge triggered D Flip-Flop

Clk=1

Y=D hold

1

0

Negative Edge triggered D Flip-Flop

Clk=0

Q=Y

0 hold

1

Negative Edge triggered D Flip-Flop

Clk=1

1 Y= 1 0 hold

1

0

Negative Edge triggered D Flip-Flop

Clk=0

1 0-> 1

Q=Y hold

0

1

Verilog Modeling

I1

𝐶𝑙𝑘𝑏

I2

Positive Edge Triggered D Flip-flop

𝐶𝑙𝑘𝑏

I1 I2

D-Type Positive Edge Triggered

Flip-Flop (CLK=0)

0

0

1

1

CLK =0, maintain the present state

D-Type Positive Edge Triggered

D=0 as Clk= 0→ 1

Flip-Flop

1

0

0→ 1

1

1 → 0

0

1 Q changes to 0

D-Type Positive Edge Triggered

D=1 as Clk= 0→ 1

Flip-Flop

0

1

0→ 1

1 → 0

1 → 1

1

0 Q changes 1

D-Type Positive Edge Triggered

D= 0→ 1 as Clk= 1

Flip-Flop

1

S’

S

S’ 1

0 → 1 revise

1

The flip-flop is unresponsive to changes in D

Please explore different possible value of S on your own.

This will work even for S=R=1 and S=R=0.

Symbol of D Flip-Flops

reset and preset

• When power is first turned on, the state of the flip-flops is unknwon.

– Reset is used to initialize the output to a 0.

– Preset is used to initialize the output to a 1.

Reset Feature

1

0

0

When Reset is 0, Q is set to 0.

1

0

D Flip-flop with reset

Typo in the book. Should be 1 instead.

JK Flip-Flops

D=JQ’+K’Q

Positive edge D flip-flop

The next value of D is determined by JQ’+K’Q.

At the rising edge of D Flip-flop, Q is updated with the value of D.

D=JQ’+K’Q

• J=1,K=1→D=Q’

• J=0, K=0 →D=Q

• J=0, K=1 →D=0

• J=1, K=0 →D=Q’+Q=1

Verilog Implementation

T Flip-Flop

T Flip-Flop from D Flip-Flop

DT

𝑄 rst

D=TQ’+T’Q

If T=1, D=Q’

If T=0, D=Q.

Q is updated with D at the next rising edge.

Verilog Implementation of a T-FF

DT

𝑄 rst