ECE 3430 * Introduction to Microcomputer Systems

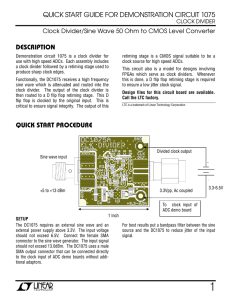

advertisement

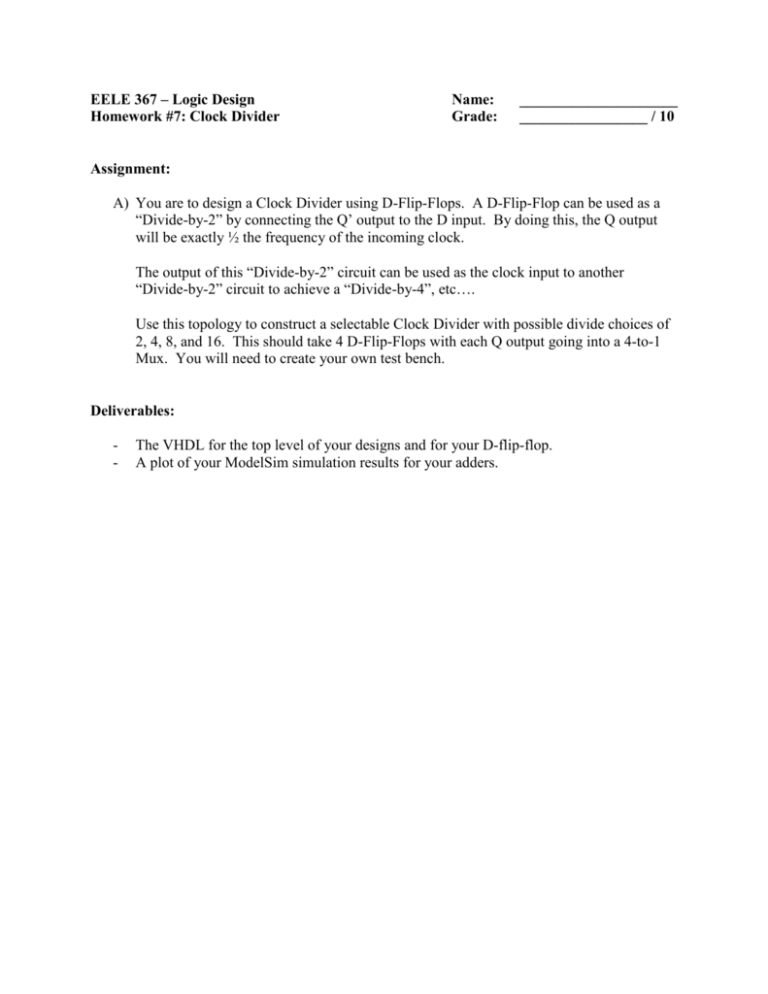

EELE 367 – Logic Design Homework #7: Clock Divider Name: Grade: _____________________ _________________ / 10 Assignment: A) You are to design a Clock Divider using D-Flip-Flops. A D-Flip-Flop can be used as a “Divide-by-2” by connecting the Q’ output to the D input. By doing this, the Q output will be exactly ½ the frequency of the incoming clock. The output of this “Divide-by-2” circuit can be used as the clock input to another “Divide-by-2” circuit to achieve a “Divide-by-4”, etc…. Use this topology to construct a selectable Clock Divider with possible divide choices of 2, 4, 8, and 16. This should take 4 D-Flip-Flops with each Q output going into a 4-to-1 Mux. You will need to create your own test bench. Deliverables: - The VHDL for the top level of your designs and for your D-flip-flop. A plot of your ModelSim simulation results for your adders.