docx - digsys.upc.edu

advertisement

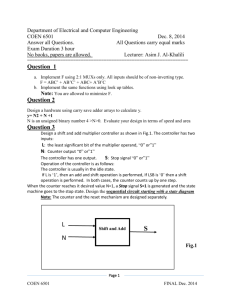

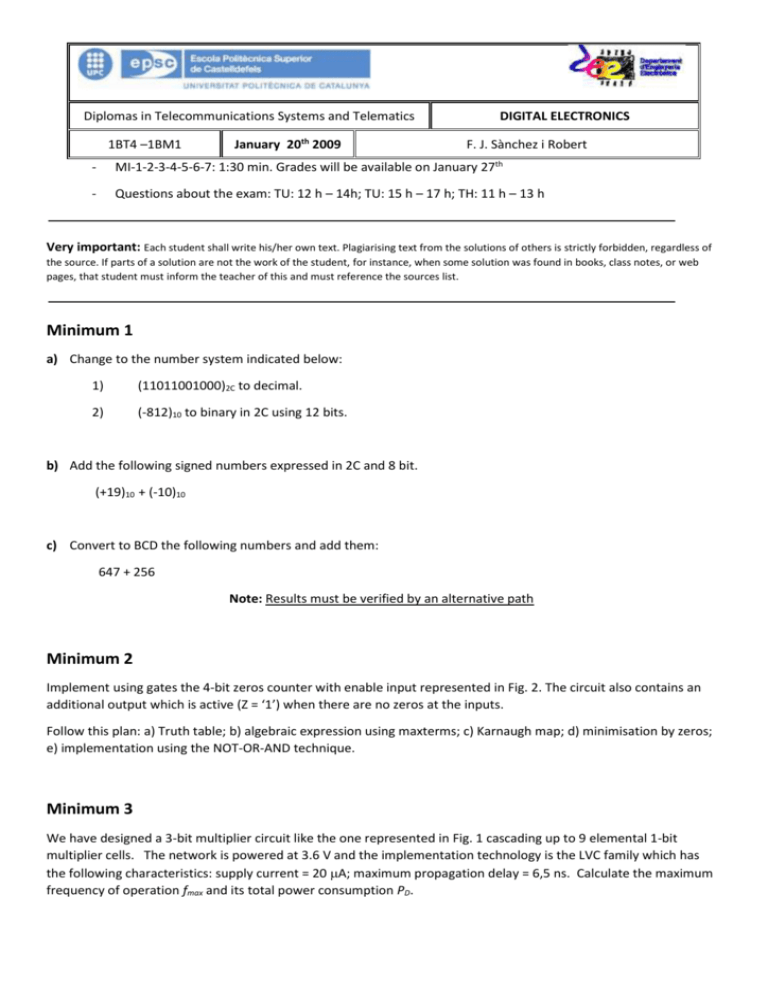

Diplomas in Telecommunications Systems and Telematics 1BT4 –1BM1 January 20th 2009 DIGITAL ELECTRONICS F. J. Sànchez i Robert - MI-1-2-3-4-5-6-7: 1:30 min. Grades will be available on January 27th - Questions about the exam: TU: 12 h – 14h; TU: 15 h – 17 h; TH: 11 h – 13 h Very important: Each student shall write his/her own text. Plagiarising text from the solutions of others is strictly forbidden, regardless of the source. If parts of a solution are not the work of the student, for instance, when some solution was found in books, class notes, or web pages, that student must inform the teacher of this and must reference the sources list. Minimum 1 a) Change to the number system indicated below: 1) (11011001000)2C to decimal. 2) (-812)10 to binary in 2C using 12 bits. b) Add the following signed numbers expressed in 2C and 8 bit. (+19)10 + (-10)10 c) Convert to BCD the following numbers and add them: 647 + 256 Note: Results must be verified by an alternative path Minimum 2 Implement using gates the 4-bit zeros counter with enable input represented in Fig. 2. The circuit also contains an additional output which is active (Z = ‘1’) when there are no zeros at the inputs. Follow this plan: a) Truth table; b) algebraic expression using maxterms; c) Karnaugh map; d) minimisation by zeros; e) implementation using the NOT-OR-AND technique. Minimum 3 We have designed a 3-bit multiplier circuit like the one represented in Fig. 1 cascading up to 9 elemental 1-bit multiplier cells. The network is powered at 3.6 V and the implementation technology is the LVC family which has the following characteristics: supply current = 20 A; maximum propagation delay = 6,5 ns. Calculate the maximum frequency of operation fmax and its total power consumption PD. Fig. 1 Combinational system to multiply 3-bit unsigned numbers Minimum 4 We aim to design a combinational circuit to count the number of zeros which are present at its 8 inputs in any order. See the functional block in Fig. 3. The circuit gives the binary number corresponding to the zeroes count. For instance, for these two input combinations: ‘01101101’, ‘11100011’, the output vector will be F[3..0] = ‘0011’. The block also have an input enable line E, and a zero output Z that is ‘1’ when there are no zeros and E = ‘1’. X3 X2 X1 X0 X[7:0] CC 4-input zeros counter 8 F2 F1 F0 Z E CC 8-input zeros counter with enable and no- zeros detection E Fig. 2 4 F[3:0] Z Fig. 3 a) Represent the internal architecture for the block in Fig. 3 if we intend to build it using the basic modules like the ones shown in Fig. 2 and other combinational circuits. b) Design using gates or by the methods of decoders or multiplexers all the circuits from your schematic. c) Explain the way you will design a 16-inputs zeros counter. Minimum 5 Our aim is to analyze the asynchronous circuit represented in Fig. 4 found in an application note referring to the 74LS93 chip. a) Draw a timing diagram which includes inputs (CLK, CD) and the outputs (Q3, Q2, Q1, Q0) in order to shown the way it works. b) What is this circuit used for? Which is the circuit’s main problem if it is discarded for precision applications? CLK CD Q0 Q1 Q2 Q3 Fig. 4 Asynchronous circuit Minimum 6 Our aim is to design a sequential block to control an electronic dice. The random number generator depicted in Fig. 5 produces the six different 3-bit binary numbers for a dice decoder. Every time that the PLAY switch is kept pressed (P = 0), a random number in the range 1 to 6 is produced due to the high frequency clock which makes the output completely unpredictable. Fig. 5 An electronic dice. Fig. 6 State diagram and standard procedure for designing FSM Minimum 7 Using standard blocks like the one represented in Fig. 7 and other circuits if necessary, build a modulo-24 BCD downcounter (…01, 00, 23, 22, …, 01, 00, 23, …). You have to start drawing the entity to be designed, then proposing an internal architecture, and finally, implementing every block in your schematic. 4 I[3..0] U-D_L CE LD 4-bit universal counter CLK TC CD 4 Q[3..0] Fig. 7 A synchronous modulo-16 binary universal counter.