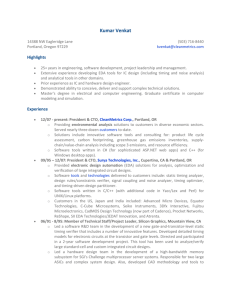

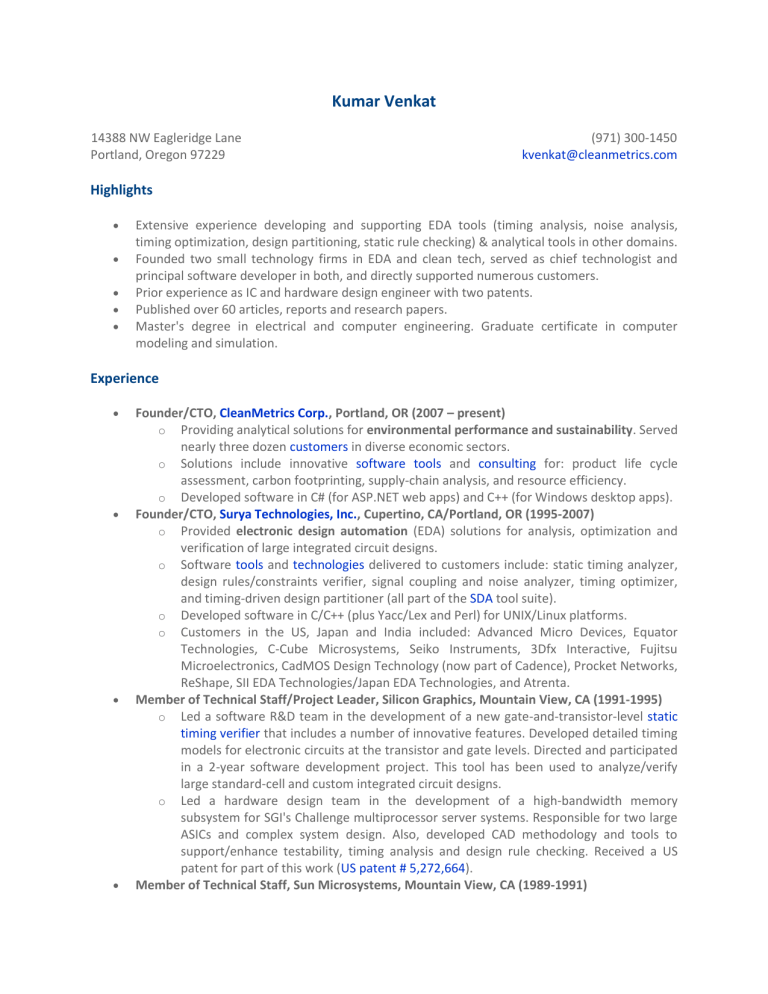

KumarVenkat

Kumar Venkat

14388 NW Eagleridge Lane (971) 300-1450

Portland, Oregon 97229 kvenkat@cleanmetrics.com

Highlights

Extensive experience developing and supporting EDA tools (timing analysis, noise analysis,

timing optimization, design partitioning, static rule checking) & analytical tools in other domains.

Founded two small technology firms in EDA and clean tech, served as chief technologist and principal software developer in both, and directly supported numerous customers.

Prior experience as IC and hardware design engineer with two patents.

Published over 60 articles, reports and research papers.

Master's degree in electrical and computer engineering. Graduate certificate in computer modeling and simulation.

Experience

Founder/CTO, CleanMetrics Corp.

, Portland, OR (2007 – present) o Providing analytical solutions for environmental performance and sustainability. Served nearly three dozen customers in diverse economic sectors. o Solutions include innovative software tools and consulting for: product life cycle assessment, carbon footprinting, supply-chain analysis, and resource efficiency. o Developed software in C# (for ASP.NET web apps) and C++ (for Windows desktop apps).

Founder/CTO, Surya Technologies, Inc.

, Cupertino, CA/Portland, OR (1995-2007) o Provided electronic design automation (EDA) solutions for analysis, optimization and verification of large integrated circuit designs. o Software tools and technologies delivered to customers include: static timing analyzer,

o o design rules/constraints verifier, signal coupling and noise analyzer, timing optimizer, and timing-driven design partitioner (all part of the SDA tool suite).

Developed software in C/C++ (plus Yacc/Lex and Perl) for UNIX/Linux platforms.

Customers in the US, Japan and India included: Advanced Micro Devices, Equator

Technologies, C-Cube Microsystems, Seiko Instruments, 3Dfx Interactive, Fujitsu

Microelectronics, CadMOS Design Technology (now part of Cadence), Procket Networks,

ReShape, SII EDA Technologies/Japan EDA Technologies, and Atrenta.

Member of Technical Staff/Project Leader, Silicon Graphics, Mountain View, CA (1991-1995) o Led a software R&D team in the development of a new gate-and-transistor-level static timing verifier that includes a number of innovative features. Developed detailed timing models for electronic circuits at the transistor and gate levels. Directed and participated in a 2-year software development project. This tool has been used to analyze/verify large standard-cell and custom integrated circuit designs. o Led a hardware design team in the development of a high-bandwidth memory subsystem for SGI's Challenge multiprocessor server systems. Responsible for two large

ASICs and complex system design. Also, developed CAD methodology and tools to support/enhance testability, timing analysis and design rule checking. Received a US patent for part of this work ( US patent # 5,272,664 ).

Member of Technical Staff, Sun Microsystems, Mountain View, CA (1989-1991)

o Designed a secondary cache-controller chip for Sun's SuperSparc microprocessor. Also, designed the scan/JTAG test logic for the chip. Contributed to CAD methodology including timing analysis, synthesis and circuit verification. Received a US patent for part of this work ( US patent # 5,987,570 ).

Senior Design Engineer, Intel Corp., Santa Clara, CA

Education

Portland State University o Graduate Certificate in computer modeling and simulation. GPA: 4.0.

Stanford University & University of South Florida o Additional graduate studies in electrical/computer engineering. GPA: 4.0.

University of Texas at El Paso o MS in electrical & computer engineering. GPA: 4.0.

University of Madras o BS in electrical engineering. Grade: Honors.

Selected Publications

Timing Verification of Dynamic Circuits , IEEE Journal of Solid-state Circuits, 1996.

Timing Verification of Dynamic Circuits , Custom Integrated Circuits Conference, 1995.

Follow these guidelines to design testable ASICs, boards and systems , EDN, 1993.

Generalized Delay Optimization of Resistive Interconnections Through an Extension of Logical

Effort , IEEE International Symposium on Circuits and Systems, 1993.

A Structured Design for Test Methodology , IEEE VLSI Test Symposium, 1993.

Link to recent publications on environmental modeling, analysis and performance metrics.