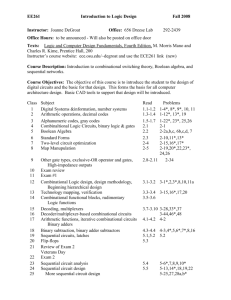

Lecture 8

advertisement

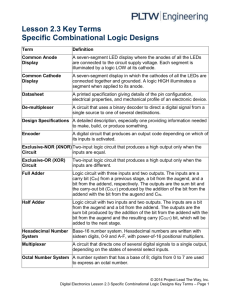

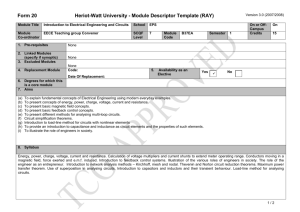

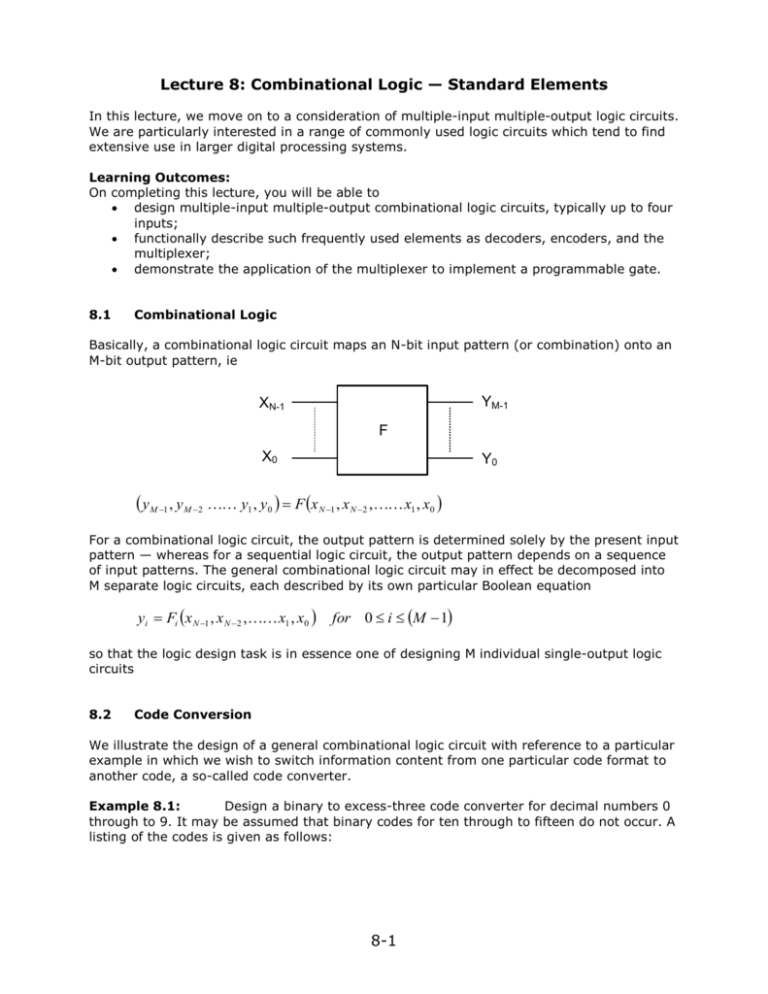

Lecture 8: Combinational Logic — Standard Elements In this lecture, we move on to a consideration of multiple-input multiple-output logic circuits. We are particularly interested in a range of commonly used logic circuits which tend to find extensive use in larger digital processing systems. Learning Outcomes: On completing this lecture, you will be able to design multiple-input multiple-output combinational logic circuits, typically up to four inputs; functionally describe such frequently used elements as decoders, encoders, and the multiplexer; demonstrate the application of the multiplexer to implement a programmable gate. 8.1 Combinational Logic Basically, a combinational logic circuit maps an N-bit input pattern (or combination) onto an M-bit output pattern, ie YM-1 XN-1 F X0 Y0 y M 1 , y M 2 y1 , y0 F x N 1 , x N 2 , x1 , x0 For a combinational logic circuit, the output pattern is determined solely by the present input pattern — whereas for a sequential logic circuit, the output pattern depends on a sequence of input patterns. The general combinational logic circuit may in effect be decomposed into M separate logic circuits, each described by its own particular Boolean equation yi Fi x N 1 , x N 2 , x1 , x0 for 0 i M 1 so that the logic design task is in essence one of designing M individual single-output logic circuits 8.2 Code Conversion We illustrate the design of a general combinational logic circuit with reference to a particular example in which we wish to switch information content from one particular code format to another code, a so-called code converter. Example 8.1: Design a binary to excess-three code converter for decimal numbers 0 through to 9. It may be assumed that binary codes for ten through to fifteen do not occur. A listing of the codes is given as follows: 8-1 Number 0 1 2 3 4 5 6 7 8 9 X3 0 0 0 0 0 0 0 0 1 1 X2 0 0 0 0 1 1 1 1 0 0 X1 0 0 1 1 0 0 1 1 0 0 X0 0 1 0 1 0 1 0 1 0 1 Y3 0 0 0 0 0 1 1 1 1 1 Y2 0 1 1 1 1 0 0 0 0 1 Y1 1 0 0 1 1 0 0 1 1 0 Y0 1 0 1 0 1 0 1 0 1 0 Treating the above listing as a truth table for our four-input four-output logic circuit, and noting that states 1010 to 1111 may considered as “don’t cares,” we form the Karnaugh map for each of the four individual functions and the associated minimum Boolean equation: X1 1 1 1 x x x x 1 1 x x X2 Y3 = X3 + X2X1 + X2X0 X2 Y2 = X2'X0 + X2'X1 +X2X1'X0' X3 X0 X1 1 1 1 1 x x x x 1 x x X3 X0 8-2 X1 1 1 1 1 X2 x x X3 1 x x x x Y1 = X1'X0' + X1X0 X0 X1 1 1 1 1 X2 x x x x x x Y0 = X0' X3 1 X0 Rather than consider these as four independent logic circuits, we look for terms (and thus sub-circuits) common to the four equations: Y3 X 3 X 2 X 1 X 2 X 0 X 3 X 2 X 1 X 0 Y2 X 2 X 0 X 2 X 1 X 2 X 1 X 0 X 2 X 1 X 0 X 2 X 1 X 0 Y1 X 1 X 0 X 1 X 0 X 1 X 0 X 1 X 0 Y0 X 0 This set of equations yields the following logic circuit: 8-3 X0 Y0 X1 X0 Y1 X1 X0 X2 Y2 X2' X2 Y3 X3 Clearly there are hardware savings resulting from the common terms. We now proceed to discuss a number of frequently used combinational logic blocks. 8.3 The Multiplexer The idea behind the multiplexer is one of data selection. D3 D2 D1 X D0 S1 S0 The unit has a number of data inputs Di, usually an integral power of two. If the unit has 2N data lines then it also has N input select lines. The binary pattern on the select lines specifies which one of the data lines is routed through to the single output. This functionality is captured in the following abbreviated truth table: S1 0 0 1 1 S0 0 1 0 1 8-4 X D0 D1 D2 D3 By inspection we have X S1 S 0 D3 S1 S 0 D2 S1 S 0 D1 S1 S 0 D0 and the corresponding logic diagram is D3 S1 S0 D2 S1 S0' X D1 S1' S0 D0 S1' S0' We note a structural correspondence between the equation for the multiplexer and the general canonical sum-of-products equation for any two-variable logic function: F ( A, B) f 3 AB f 2 AB f1 AB f 0 AB f3 f2 f1 f0 D3 D2 X D1 X D0 S1 S0 A B By applying the A,B inputs to the data selection nodes S1, S0, and the f3, f2, f1, f0 coefficients to the D3, D2, D1, D0 inputs, the multiplexer can be used to implement any two-variable logic function. In this sense, it can be regarded as an implementation of the two-input fully programmable logic gate. 8-5 8.4 Other Logic Elements D3 S1 D2 D1 D0 S0 A decoder is a logic circuit with N inputs and 2N outputs. Only one of the output lines is activated with a 1, that corresponding to the binary code present at the input. Again the following table specifies the function in abbreviated truth table form. S1 0 0 1 1 S0 0 1 0 1 X3 0 0 0 1 X2 0 0 1 0 X1 O 1 0 0 X0 1 0 0 0 A set of Boolean equations can be written for the four outputs and the corresponding logic diagram can be determined. D3 X1 D2 D1 D0 X0 An encoder is the opposite of the decoder; it has 2N inputs and, assuming only one input line is activated (with a 1), it produces at the output the binary code corresponding to that input which is activated. This is captured in the following truth table: D3 0 0 0 1 D2 0 0 1 0 D1 0 1 0 0 D0 1 0 0 0 X1 0 0 1 1 X0 0 1 0 1 Again, the logic equation and diagram follow directly. A so-called priority encoder allows for the possibility of more than one input being activated. However, the element will have a prioritising protocol whereby if two or more inputs are activated, only the activated input with the highest priority will have its binary code at the output. Generally, D3 will have higher priority than D2 which will have higher priority than D1, etc. 8-6 8.4 Conclusion In this lecture, we have covered the general problem of combinational logic design and introduced a number of standard functional elements such as the multiplexer, decoder, and encoder. When designing integrated circuits, these standard functional elements come as pre-designed standard cells in addition to the primitive gates such as NAND, NOR, etc, thus simplifying the system design task. 8-7