Slides

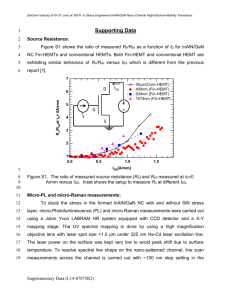

advertisement

Vertically scaled 5 nm GaN channel Enhancement-mode N-polar GaN MOS-HFET with 560 mS/mm gm and 0.76 W-mm Ron Uttam Singisetti*, Man Hoi Wong, Jim Speck, and Umesh Mishra ECE and Materials Departments University of California, Santa Barbara, CA 2011 Device Research Conference Santa Barbara, CA, USA *uttam@ece.ucsb.edu 1 Outline • Next generation GaN electronic devices • N-polar GaN HEMTs • Vertically scaled channel devices • Results and Conclusion 2 Next-generation mm-wave GaN devices John Albrecht, DARPA 1.3 W at 75 GHz Fujitsu, CSIC 2010 3 W at 87 GHz Caltech, HRL ISSSTT, 2011 W-band GaN power amplifiers − GaN HEMTs: Power-switching, microwave, W-band power amplifiers −Future GaN devices for beyond mm-wave and to sub-mm-wave bands −Higher operating voltages than traditional III-Vs and Si robust and rugged mixed signal ICs 3 Device goals and structure −Aggressive dimensional scaling (Lg and Lsd ) −Vertical scaling with back-barrier and high-k dielectric − Parasitic resistances and capacitances scaling −Maintain high breakdown voltage 4 Ultra-scaled N-polar HEMTs No electron barrier N-polar inverted HEMT N-polar GaN − No barrier to electron on top of 2-DEG grading to narrowgap InN low resistance contacts (0.027 W-mm)1 − AlGaN back confinement of 2-DEG, control short channel effects2 − Record high gm = 1105 mS/mm demonstrated4 in D-mode − E-mode devices 1. S.Dasgupta, APL 2010, 2. S. Rajan, IEEE TED 2011 3. NIdhi, DRC 2011 5 E-mode device structure and design AlN 4 AlN GaN 0 Al2O3 4 0 3.0 0 EF -1 GaN 2.0 1.5 1.0 -2 E V 15 20 25 30 35 AlN 3 40 2 1 GaN:Si n+ Graded InGaN (In: 0% to 65%) GaN InN channel 0 EF -1 -2 -3 -4 -3 0.5 0 20 40 60 80 100 Depth (nm) -4 20 n (x10 cm ) 1 GaN -3 Energy (eV) 2 EC 10 Under gate 2.5 GaN:Si 5 Depth (nm) 19 SiNx 3 Top AlN depletes 2-DEG under gate EV -6 AlN n(x) EF -2 -4 4 AlxGa1-xN:Si 0.05<x<0.25 Energy (eV) Energy (eV) 2 EC 40 60 Depth (nm) 80 0.0 100 Under S/D contacts* Under sidewall AlN removed under sidewall * S.Dasgupta, APL 2010 6 Short channel effect and vertical scaling 8 nm GaN channel2 20 nm GaN channel1 Vt roll-off with gate length Poor saturation at sub-100nm Lg • Vth roll off with gate length • Vertical scaling needed to maintain E-mode at sub-50 nm gate lengths • Vertical scaling for high Rds at sub-50-nm gate lengths Need 5 nm GaN channel for sub-50 nm devices 1. U.Singisetti, EDL 2010, 2. U.Singisetti, APEX 2011 7 Ultra-thin channel challenges: Mobility QW thickness flutuations GaN • Need 5 nm thick GaN channel for sub-50 nm devices • Mobility drops with decreasing GaN channel thickness • Interface roughness, surface roughness scattering increases* * U.Singisetti, ISCS 2011 8 Mobility dependence on Si doping Si : 5 e18 cm-3 Si : 2 e 19 cm-3 • Low mobility in high-3D Si density samples • High Si density may lead to rougher interface 9 Ultra-thin channel challenges: surface depletion • Surface depletion increases in thin channels • Lower charge in the access regions lead to higher source resistance 10 5nm-GaN channel device design • Graded back-barrier high mobility and t reduce the effect of trap* • 4.5 nm of Al2O3 gate dielectric • 1.6×1013 cm-2 in the sidewall access regions after top-AlN etch * M -H Wong, DRC 2011. 11 Device fabrication process* * U.Singisetti, EDL 2010. 12 DC characteristics • Reduced short channel effects due to vertical scaling and graded barrier1 • Peak gm = 560 mS/mm, peak Id = 1.3 A/mm • Positive threshold voltage of 1.3 V * M -H Wong, DRC 2011. 13 DC characteristics: Ron and Rs Gate InN InN Gate No InN • Record low Ron = 0.61 W-mm* for Lg = 115 nm • InN growth optimization for complete coverage near the gate • Regrowth sheet resistance = 100 W/sq, rc = 5 W-mm 14 RF performance: peak ft • peak ft = 115 GHz at Vds = 4.5 V and Vgs = 2.5 V • low fmax = 30 GHz due to thin W gate ( ~ 1500 W/sq) 15 RF performance : small-signal model Measured (circles) Modeled (line) S21/5 S12*3 S11 S22 • Equivalent circuit model 16 RF performance: bias dependence • Vgs corrosponding to peak ft is 2.5 V • Absence of drain delay 17 Conclusions and future work • Demonstrated vertically scaled 5-nm GaN channel MOS-HFET devices • E-mode with Vth = 1.3 V, peak gm = 560 mS/mm, peak Id = 1.3 A/mm • Record low Ron = 0.61 W-mm, for 115 nm E-mode GaN HEMTs • peak ft = 115 GHz for 120 nm gate length device Future work • Scale the gate length to 50 nm • Top gate for fmax • Scale the gate dielectric (HfO2, ZrO2) This work was supported by DARPA NEXT program 18 New measurements post DRC • peak ft = 122 GHz at Vds = 5.5 V and Vgs = 2.5 V • ft-Lg product of 14 GHz-mm 19 New measurements post DRC • maximum Ion/Ioff ratio ~ 2×105 • Breakdown voltage 8. 6 V • dielectric breakdown 20