wed_ei7_0925_friedl

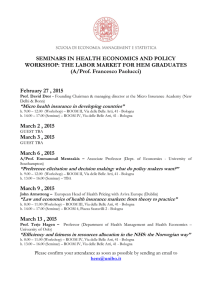

advertisement

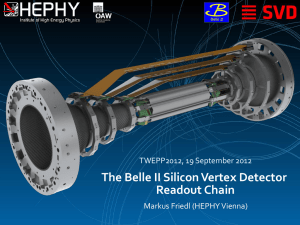

VCI, 13 February 2013 The Belle II Silicon Vertex Detector Markus Friedl (HEPHY Vienna) for the Belle II SVD Group Introduction Front-End Electronics Performance Summary M.Friedl (Belle II SVD Group): The Belle II SVD 13 February 2013 2 Introduction Front-End Electronics Performance Summary M.Friedl (Belle II SVD Group): The Belle II SVD 13 February 2013 3 KEKB and Belle @ KEK (1999-2010) KEKB ~1 km in diameter Belle Asymmetric machine: 8 GeV e- on 3.5 GeV e+ Belle Linac KEKB About 60km northeast of Tokyo Center of mass energy: Y(4S) (10.58 GeV) High intensity beams (1.6 A & 1.3 A) Integrated luminosity of 1 ab-1 recorded in total Linac Belle mentioned explicitly in 2008 Physics Nobel Prize announcement to Kobayashi and Masukawa M.Friedl (Belle II SVD Group): The Belle II SVD 13 February 2013 4 SuperKEKB/Belle II Upgrade: 2010–2015 Aim: super-high luminosity ~81035 cm-2s-1 11010 BB / year LoI published in 2004; TDR published in 2010 Refurbishment of accelerator and detector required nano-beams with cross-sections of ~10 µm x 60 nm 10 mm radius beam pipe at interaction region http://belle2.kek.jp M.Friedl (Belle II SVD Group): The Belle II SVD 13 February 2013 5 Belle II Vertexing Subdetectors Silicon Vertex Detector (SVD) 4 layers of DSSDs Pixel Detector (PXD) 2 layers of DEPFET pixels M.Friedl (Belle II SVD Group): The Belle II SVD 13 February 2013 6 Belle II Vertexing Environment Low energy machine (10.58 GeV) – multiple scattering Needs very low mass detector PXD DEPFET sensors are thinned to 75 µm SVD uses “Origami chip-on-sensor” concept High luminosity – occupancy/pile-up Need small sensitive area and/or fast readout PXD has small cell size (50 x 50 µm2) SVD has fast shaping (50 ns) and hit time reconstruction (~3 ns) Radiation – 100 kGy Magnetic field – 1.8 T M.Friedl (Belle II SVD Group): The Belle II SVD 13 February 2013 7 Silicon Vertex Detector Concept Use largest possible (6”) double-sided sensors (DSSDs) Minimize relative amount of structural material Fast shaping readout Minimize occupancy Fast readout implies higher noise Noise is mainly determined by input capacitance Place readout chips as close as possible to sensor strips Minimize capacitive load by avoiding long fanouts Use efficient CO2 cooling Allows thin cooling pipes M.Friedl (Belle II SVD Group): The Belle II SVD 13 February 2013 8 Belle II Vertex Detector Pixel Detector – 8M pixels 2 DEPFET layers at r = 14, 22 mm Excellent and unambiguous spatial resolution (~15 µm) Coarse time resolution (20 µs) Silicon Vertex Detector – 220k strips 4 DSSD layers at r = 38, 80, 104, 135 mm Good spatial resolution (~12/25 µm) but ambiguities due to ghosting Excellent time resolution (~3 ns) Combining both parts yields a very powerful device! M.Friedl (Belle II SVD Group): The Belle II SVD 13 February 2013 9 Introduction Front-End Electronics Performance Summary M.Friedl (Belle II SVD Group): The Belle II SVD 13 February 2013 10 Front-End Geometry 4 layers arranged in ladders Outer 3 layers have slanted forward part Limited acceptance angle (17°…150°) allows to place services outside (cyan cones) while minimizing material within M.Friedl (Belle II SVD Group): The Belle II SVD 13 February 2013 11 Double-Sided Silicon Sensors 3 different types required Large rectangular sensors – 123 x 58 mm2 (HPK) Small rectangular sensors – 123 x 38 mm2 (HPK) Trapezoidal sensors – 123 x 58…38 mm2 (Micron) Production is in progress Presently ~60% delivered M.Friedl (Belle II SVD Group): The Belle II SVD 13 February 2013 12 Origami Chip-on-Sensor Concept Low-mass double-sided readout Flex fanout pieces wrapped to opposite side All chips aligned on one side single cooling pipe (D = 1.6 mm) 3-layer kapton hybrid CF sandwich ribs APV25 chips (thinned to 100µm) cooling pipe Side View (below) DSSD fanout for n-side (z) flex fanout wrapped to p-side (r-phi) wrapped cooling pipe flex fanout APV25 (thinned to 100µm) Kapton Airex Sensor support ribs M.Friedl (Belle II SVD Group): The Belle II SVD 13 February 2013 13 Origami Prototype Modules Single Origami module Double Origami module M.Friedl (Belle II SVD Group): The Belle II SVD 13 February 2013 14 Sensor underneath flex circuit End ring (support) APV25 chips Origami ladder Pitch adapter bent around sensor edge Cooling pipe M.Friedl (Belle II SVD Group): The Belle II SVD 13 February 2013 15 Introduction Front-End Electronics Performance Summary M.Friedl (Belle II SVD Group): The Belle II SVD 13 February 2013 16 General SVD Readout Scheme Based on existing prototype system DATCON ONSEN (2007) verified in lab and beam tests Finesse Transmitter Board (FTB) FADC ~2m Junction ~10m copper box copper cable cable Unified optical data link (>20m) COPPER 1748 APV25 chips Front-end hybrids Rad-hard DC/DC converters Analog level translation, data sparsification and hit time reconstruction M.Friedl (Belle II SVD Group): The Belle II SVD 13 February 2013 Unified Belle II DAQ system 17 APV25 Front-End Chip MUX gain 128:1 Differential MUX current output amp inverter pipeline preamp shaper APSP S/H Developed for CMS by IC London and RAL 70,000 chips running in the CMS Tracker since 2008 40 MHz clock; 128 channels; 192 cells deep analog pipeline 50 ns (adjustable) shaping time 0.25 µm CMOS process (>100 MRad tolerant) Low noise: 250 e + 36 e/pF Multi-peak mode (read out several samples along shaping curve) M.Friedl (Belle II SVD Group): The Belle II SVD 13 February 2013 18 Junction Box CERN-made DC/DC converters for front-end powering Comparative measurement: no noise penalty M.Friedl (Belle II SVD Group): The Belle II SVD 13 February 2013 19 FADC Block Diagram Jitter Cleaner Delay CLK Controls V/I Monitoring Junction Box FIR ADCs Signals Level Translation Controls Central FPGA VME FPGA Slow Controls Data Data FADC Controller VME bus GbE FTB HV LV Analog & digital level translation between bias and GND Digitization, signal conditioning (FIR filter), data processing Central FPGA is an Altera Stratix IV GX M.Friedl (Belle II SVD Group): The Belle II SVD 13 February 2013 20 FADC: Overall Concept 9U VME Indicator LEDs VME Altera P1 Delay Analog level translation Bus ADCs CLK distribution Stratix 4 GX daughter board Jitter Cleaner Hybrid Connectors P2 FE control & monitoring Digital (controls) level translation GbE Delay CLK distribution M.Friedl (Belle II SVD Group): The Belle II SVD P3 module (needs much space for level translation circuits) Circuit is designed, now PCB layout is made 13 February 2013 21 The “Human” Touch… M.Friedl (Belle II SVD Group): The Belle II SVD 13 February 2013 22 FTB: Link to DAQ and PXD Firmware development ongoing Optical link tests at 2.54 and 3.175 Gb/s successful Second iteration of PCB for minor corrections underway SVD data are also streamed to PXD for online data reduction M.Friedl (Belle II SVD Group): The Belle II SVD 13 February 2013 23 Introduction Front-End Electronics Performance Summary M.Friedl (Belle II SVD Group): The Belle II SVD 13 February 2013 24 Hit Time Reconstruction Benefits Belle I SVD VA1TA Tp~800ns Threshold Time over threshold ~ 2000ns (measured) APV25 Reduction ~12.5 Tp~50ns Threshold Time over threshold ~ 160ns (measured) Pulse shape processing RMS(tmax)~3ns Sensitive time window ~ 20ns Belle II SVD Reduction ~8 Total reduction ~100 Sufficient to cope with a 40-fold increase in luminosity M.Friedl (Belle II SVD Group): The Belle II SVD 13 February 2013 25 Achieved Hit Time Resolution Results achieved in beam tests with several different types of Belle II prototype modules (covering a broad range of SNR) Peak time precision vs. SNR 10 2...3 ns RMS Will be done in FPGA (using lookup tables) – simulation successful KEK Nov 08 standard KEK Nov 08 doubled IPRE 8 KEK Nov 08 31.8 Mhz SPS Aug 09 run042 7 SPS Aug 09 run043 Trms [ns] accuracy at typical cluster SNR (14...24) SPS June 2008 9 SPS Aug 09 run6873 6 SPS Aug 09 run012 SPS Aug 09 run019 5 Theory 4 3 2 Close to theoretical limit 1 (G. De Geronimo, in “Medical Imaging” by K. Iniewski) 0 0 M.Friedl (Belle II SVD Group): The Belle II SVD 5 10 15 20 25 30 Cluster SNR 13 February 2013 26 Z Vertex Resolution Belle II (PXD & SVD) will be a factor 2 better than Belle (SVD only) M.Friedl (Belle II SVD Group): The Belle II SVD 13 February 2013 27 Introduction Front-End Electronics Performance Summary M.Friedl (Belle II SVD Group): The Belle II SVD 13 February 2013 28 Summary Belle II Vertex Detector consists of Pixel Detector (PXD): unambiguous spatial resolution Silicon Vertex Detector (SVD): precise timing Silicon Vertex Detector 4 layers of 6” double-sided silicon sensors APV25 front-end chip with 50 ns shaping time Origami chip-on-sensor readout concept for low mass Highly efficient CO2 cooling Schedule R&D completed, construction has started Now building final prototypes (pre-series) M.Friedl (Belle II SVD Group): The Belle II SVD 13 February 2013 29