Scaling of MOS circuits - KIT

advertisement

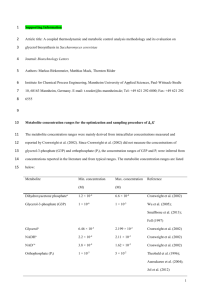

• What is Scaling? • Proportional adjustment of the dimensions of an electronic device while maintaining the electrical properties of the device 10 Feature Size (m) 10 6 3 1.5 1 1 0.8 0.6 0.35 0.25 0.18 0.13 0.09 0.1 1965 1970 1975 1980 1985 Year 1990 1995 2000 2005 • Impact of scaling is characterized in terms of several indicators: Minimum feature size Number of gates on one chip Power dissipation Maximum operational frequency Die size Production cost 1) Full Scaling (Constant Electrical Field) • Ideal model – dimensions and voltage scale together by the same scale factor 2) Fixed Voltage Scaling • Most common model until recently – only the dimensions scale, voltages remain constant 3) General Scaling • Most realistic for today’s situation – voltages and dimensions scale with different factors • Device scaling modeled in terms of generic scaling factors: 1/α and 1/β 1/ β : scaling factor for supply voltage VDD and gate oxide thickness D 1/α: linear dimensions both horizontal and vertical dimensions • Gate area Ag Where L: Channel length and W: Channel width and both are scaled by 1/α • Thus Ag is scaled up by 1/α2 • Gate capacitance per unit area Co or Cox Where εox is permittivity of gate oxide(thin-ox)= εins εo and D is the gate oxide thickness scaled by 1/ β • Thus Cox is scaled up by • Gate capacitance Cg Thus Cg is scaled up by β * 1/α2 = β/α2 • Parasitic capacitance Cx • Cx is proportional to Ax/d where d is the depletion width around source or drain and scaled by 1/ α Ax is the area of the depletion region around source or drain, scaled by (1/α2 ). • Thus Cx is scaled up by • Carrier density in channel Qon • where Qon is the average charge per unit area in the ‘on’ state. • Co is scaled by β and Vgs is scaled by 1/β • Thus Qon is scaled by 1 • Channel Resistance Ron • Where μ = channel carrier mobility and assumed constant • Thus Ron is scaled by 1 • Gate delay Td • Td is proportional to Ron*Cg • Td is scaled by • Maximum operating frequency fo • fo is inversely proportional to delay Td and is scaled by • Saturation current Idss • Both Vgs and Vt are scaled by (1/β). Therefore, Idss is scaled by • Current density, J= Idss/A • where A is cross sectional area of the • Channel in the “on” state which is scaled by (1/ α 2) • So, J is scaled by • Switching energy per gate Eg • So Eg is scaled by • Power dissipation per gate Pg • Pg comprises of two components: static component Pgs and dynamic component Pgd: Where, the static power component is given by: And the dynamic component by: Since VDD scales by (1/ β) and Ron scales by 1, Pgs scales by (1/ β2). Since Eg scales by (1/ α2β ) and fo by (α2 / β), Pgd also scales by (1/ β2). Therefore, Pg scales by (1/ β2). • Power dissipation per unit area Pa • Power – speed product PT