UNIT-6-Mixed-Type-Description - KIT

advertisement

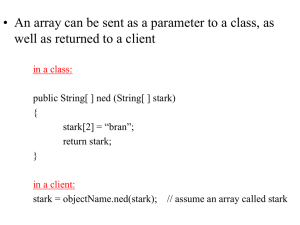

UNIT 6: Mixed-Type Description Writing with several styles (data flow, behavioral, structural,..) in the same module 7.1 Why Mixed-Type Description? Each type (style) has its own advantages. The system can be divided into segments, each segment is described using the most suitable style HDL Programming Fundamentals 7.2 VHDL User-Defined Type type week_days is (mon, tues, wed, th, fr, sat, sun); type states is (S0, S1, S2, S3); type grades is (A, B, C, D, F, I); If we write signal scores : grades; Then scores can take A, B, C, D, F, or I HDL Programming Fundamentals 7.3 VHDL Packages Packages may include type and subtype declarations, constant definitions, function and procedure, and component declarations. Listing 7.2 An Example of a VHDL package library ieee; use ieee.std_logic_1164.all; package codes is type op is (add,mul, divide, none); end; use work. codes; entity ALUS2 is port (a, b: in std_logic_vector(3 downto 0); cin: in std_logic; opc :in op; z: out std_logic_vector(7 downto 0); cout: buffer std_logic); end ALUS2; HDL Programming Fundamentals 7.3.1 Implementation of Arrays 7.3.1.1 Single-Dimensional Arrays a) VHDL type datavector is array (3 downto 0) of wordarray; subtype wordarray is std_logic_vector (1 downto 0); b) Verilog reg [1:0] datavector[0:3]; This declares an array by the name of datavector; it has 4 elements; each element is 2 bits. An example of this array is: datavector[0] = 2'b01; datavector[1] = 2'b10; datavector[2] = 2'b10; datavector[3] = 2'b11; HDL Programming Fundamentals Example 7.1 Find the greatest among N elements of an Arrays a) VHDL Description library IEEE; use IEEE.STD_LOGIC_1164.all; --Build a package for an array package array_pkg is constant N: integer := 4; --N+1 is the number of elements in the array. constant M: integer := 3; --M+1 is the number of bits of each element --of the array. subtype wordN is std_logic_vector (M downto 0); type strng is array (N downto 0) of wordN; end array_pkg; library IEEE; use IEEE.STD_LOGIC_1164.ALL; use work.array_pkg.all; -- The above statement makes the package array_pkg visible in --this module -- A program to find the greatest value among elements of an array entity array1 is generic (N:integer :=4; M: integer := 3); --N+1 is the number of elements in the array; M=1 is the --number of bits of each element. Port ( a : inout strng; end array1; z : out std_logic_vector (M downto 0)); HDL Programming Fundamentals architecture max of array1 is begin com: process (a) variable grtst: word4; begin --enter the data of the array. a <= ("0110", "0111", "0010", "0011", "0001"); grtst := "0000"; lop1: for i in 0 to N loop if (grtst <= a(i)) then grtst := a(i); report " grtst is less or equal than a"; -- use the above report statement if you want to monitor the --progress of the program else report "grtst is greater than a"; -- Use the above report statement to monitor the --progress of the program end if; end loop lop1; z <= grtst; end process com; end max; HDL Programming Fundamentals b) Verilog Description module array1( start ,grtst ); parameter N = 4; parameter M = 3; input start; output [3:0] grtst; reg [M:0] a[0:N]; /*The above statement is declaring an array of N+1 elements; each element is M bits. */ reg [3:0] grtst; integer i; always @ (start) begin a [0] = 4'b0110; a[1] = 4'b0111; a[2] = 4'b0010; a[3] = 4'b0011; a[4] = 4'b0001; grtst = 4'b0000; HDL Programming Fundamentals for (i = 0; i <= N; i= i +1) begin if (grtst <= a[i]) begin grtst = a[i]; $display ( " grtst is less or equal than a"); // use the above statement to monitor the program end else $display ( " grtst is greater than a"); // use the above statement to monitor the program end end endmodule HDL Programming Fundamentals Example 7.2 Multiplication of two signed N-Element Vectors Using Arrays Listing 7.4 7.3.1.2 Two-Dimensional Arrays VHDL allows for multidimensional arrays. Standard Verilog allows only for single dimensional array. In VHDL, two dimensional arrays are described by the use of type statements. For example, the statements: subtype wordg is integer ; type singl is array (2 downto 0) of wordg; type doubl is array (1 downto 0) of single describe a two dimensional array; each single dimensional array has 3 elements; each element is an integer. An example of such two dimensional array is the array y y = ((10 5 6), (3 -2 7)) The elements of the array y are: y(0)(0) = 7 refers to element 0 of array 0 y(1)(1) = 5 refers to element 1 of array 1 y(2)(0) = 3 refers to element 2 of array 0 y(2)(1) = 10 refers to element 2 of array 0 HDL Programming Fundamentals Example 7.3 Two-Dimensional Array HDL Programming Fundamentals Example 7.4 Matrix Addition 14 9 7 1 2 8 7 9 3 7 3 2 12 5 4 5 9 2 3 3 4 3 3 10 8 + 7 4 4 6 3 5 1 3 9 3 3 9 7 7 2 14 18 6 8 6 8 4 11 5 9 Listing 7.6 HDL Programming Fundamentals 7.4 Mixed-Type Description Examples Example 7.5 HDL Description of an Arithmetic-Logic Unit (ALU) HDL Programming Fundamentals Table7.1 Operation Code (opc) 00 01 10 11 Operation Addition Multiplication Integer Division No Operation HDL Programming Fundamentals Example 7.6 HDL Description of a 16x8 Static RAM. Listing 7.8 HDL Programming Fundamentals Table 7.2 Function Table of Static RAM. CS R_ Data_out 0 x Z (high impedance) 1 1 M (ABUS) 1 0 Memory function The memory is deselected. This is a read; M refers to memory locations. contents of memory location pointed by ABUS is placed on the output data. This is a write cycle; data in the Data_in are stored in M(ABUS) HDL Programming Fundamentals Example 7.7 Description of a Finite Sequential State Machine Listing 7.9 HDL Programming Fundamentals Case Study 7.1 HDL Description of a Basic Computer Listing 7.10 HDL Programming Fundamentals Table 7.3 operation codes for operations. Operation in Mnemonic OP Code HALT ADD MULT DIVID XOR PRITY NAND CLA 000 001 010 011 100 101 110 111 HDL Programming Fundamentals HDL Programming Fundamentals HDL Programming Fundamentals Table 7.4 Contents of Memory of the Basic Computer Location in Hex Instruction in Mnemonic or Data in Hex Memory Contents (8 bits) in Hex 0 CLA E0 1 ADD 9 29 2 XOR A 8A 3 MULT B 4B 4 DIVID C 6C 5 XOR D 8D 6 NAND E CE 7 PRITY A0 8 HALT 00 9 C 0C A 5 05 B 4 04 C 9 09 D 3 03 E 9 09 F 7 07 HDL Programming Fundamentals HDL Programming Fundamentals Summary Mixed-Type Description has been covered Packages are an essential construct in VHDL code. It may include: User-defined types, Components, Functions, and Procedures. VHDL, in contrast to Verilog, allows for multidimensional arrays. HDL Programming Fundamentals