An Example MicroArchitecture - CS Department

CS 3A: Introduction to

Computer Organization

Example MicroArchitecture

Tannenbaum 4.1.1, 4.1.2

Department of Computer Science

Saddleback College

Shannon Alfaro

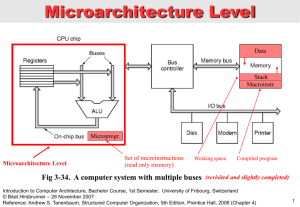

MicroArchitecture Level

• A brief look at our levels again…

– We’ve looked at the lowest level : Digital

Logic Level

– Now we’ll look at the

MicroArchitecture

Level

Big picture

Design of MicroArchitecture

• Depends on ISA being implemented

• ISA: RISC: 1 instruction/cycle; SPARC

CISC: 1 instruction/(>1cycle); Pentium

• Want to: explain general principles of microarchitecture design but

THERE ARE NONE!! EACH IS UNIQUE

Example MicroArchitecture

• Chosen a subset JVM for integer operations: IJVM : Integer Java Virtual

Machine

• Our microarchitecture will contain a microprogram (in ROM) whose job is to:

– Fetch

– Decode

– Execute _________ instructions

1 blank

Example MicroArchitecture

• Imagine the design of MicroArchitecture as the following code:

• The microprogram has a set of variables

• Values represent the ________ of the computer

1 blank

Example MicroArchitecture

• IJVM Instructions: short; usually 1-2 fields

Opcode Operand

Operation to

Perform register locations/ variables

• Every instruction has an ________

• Many instructions have _________

• Model of Execution: fetch-execute cycle

2 blanks

The Language to be

High Level

Instructions

Implemented

IJVM: ISA Instructions

Compiler/

Assembler

MicroProgram in CPU

MicroInstructions

Memories…..

• Remember When???

CPU = Controller + Datapath

• Datapath: contains

– ALU

– Registers

– inputs & outputs (not shown)

IJVM Datapath

• Datapath: contains

– 32-bit registers

• registers are accessible only by micro-program at the microarchitecture level.

– B-BUS : Contents of Registers

– C-BUS : Output of ALU & can write to multiple registers at once

– ALU

IJVM Datapath

• Datapath: contains an ALU:

– just like what we constructed in chapter 3

(remember our decoder +

Adder/Subtractor & Logic gates?)

– Needs 2 inputs:

A(left) register H (1 source)

B(right) Bus B (9 sources)

Stack Based Machine

• Stack Based Machine: Operands are placed on a stack & result is stored on the stack

• SP: top of stack pointer

• LV: pointer to local variables

IJVM Instruction Set

Compiling Java to IJVM

IJVM Arithmetic Logic Unit

• ALU Operation:

– To load H :

• choose an ALU function that

1. Passes the value at the B input through the ALU

2. Writes value back into H i.e. identity of B

ALU Truth Table

IJVM Arithmetic Logic Unit

• ALU Operation:

– Read & Write in Same Cycle

• Can happen with magic & timing

ALU Truth Table

1st half of cycle you read register

2nd half you write

Datapath Timing

• Propagation Delay

– Just as in our homework problem, there is a delay before the output of our gates is stable

• Δx before values is stable; then ALU & shifter can begin computation

• Δy: ALU & Shifter outputs are stable

• Δz: results propagated along C bus to registers

• Rising Edge: Registers Latch values into memory cells

•Δw time passes before valid

Datapath Timing

• Propagation Delay

– Just as in our homework problem, there is a delay before the output of our gates is stable

• Δy: ALU & Shifter outputs are stable

• Δz: results propagated along C bus to registers

• Rising Edge: Registers Latch values into memory cells

•Δx before values is stable

•then ALU & shifter can begin computation

Datapath Timing

• Propagation Delay

– Just as in our homework problem, there is a delay before the output of our gates is stable

• Δz: results propagated along C bus to registers

• Rising Edge: Registers Latch values into memory cells

•Δy: ALU & Shifter outputs are stable

Datapath Timing

• Propagation Delay

– Just as in our homework problem, there is a delay before the output of our gates is stable

• Δz: results propagated along C bus to registers

• Rising Edge: Registers Latch values into memory cells

•Δz: results propagated along C bus to registers

Datapath Timing

• Propagation Delay

– Just as in our homework problem, there is a delay before the output of our gates is stable

•Rising Edge: Registers Latch values into memory cells

Datapath Timing

• To Implement this requires:

• Rigid timing

• ______clock cycle

• _________________ propagation delay

• Fast load of registers from C Bus

2 blanks

Datapath Timing

• Things to Note:

– Falling Edge Signals Start of Bus Cycle

– Rising Edge Signals End of Bus Cycle

– ____ units are operating ____ the time. The values are garbage until the known delay has passed.

• Clock Length >= Δw + Δx + Δy + Δz

2 blanks

Memory Operations

• 2-ways to address memory:

– 32-bit word-addressable memory

– Memory Address Register ( MAR )

– Memory Data Register ( MDR )

– 8-bit byte-addressable memory port

– Program Counter ( PC ) = MBR [7…0]; Read Only

Memory Operations

• Register Combinations

– MAR/MDR : used to read/write ISA-level data words

– PC/MBR : used to read the executable ISA-level program (consists of a byte stream)

• NOTE: MBR: additional open arrow

– determines whether the MBR value placed on Bus is +ive or –ive

MicroInstructions

• Recall… ALUs, Register, Buses

– All have control signals

– Actions determined by their truth table.

• IJVM Datapath

– 29 signals needed to control all of our components.

– values of signals control which portions of the circuit are contributing to the final result of the bus cycle.

These signals together create our

Binary Micro-Instruction

MicroInstructions

• Signals are divided up into 5 functional groups:

• 9 signals to control writing data from the C bus into registers

• 9 signals to control enabling registers onto the B bus for

ALU input

• 8 signals to control the ALU and shifter functions

• 2 signals (not shown) to indicate memory read/write via

MAR/MDR

• 1 signal (not shown) to indicate memory fetch via PC/MBR

Memory Read Operation

• 1st Bus Cycle:

– Memory Address is loaded into MAR

• 2nd Bus Cycle:

– Data is fetched from Memory & stored in registers

• 3rd Bus Cycle:

– Data can now be used in an instruction

Memory Read Operation

• NOTE:

– We can start another instruction during the 2nd bus cycle

– not one that needs this information from the previous read

MicroInstruction Format

• 36-signals to 1 IJVM instruction

• Groups:

Addr: Contains the address of a potential next microinstruction

JAM: Determines how next microinstruction is selected

MicroInstruction Format

• Groups:

JAM: Determines how next microinstruction is selected

N: ALU result was negative

A-B= -ive A < B

Z: ALU result was zero

A-B = 0 A = B

MicroInstruction Format

• Groups:

ALU: controls the ALU & shifter functions

C: Selects which registers are written from the C Bus

Mem: Memory Functions

B: Selects the B bus source

Finally….

• Here we are!!!

Our Controller

+ Datapath !!!

Sequencer

• Responsible for stepping through the sequence operations necessary for execution of a single ISA instruction . of

• Produce 2 kinds of information on each cycle

– state of every control signal in the system

– address of the microinstruction that is to be executed next

Control Store

• Holds microprogram : can be implemented as memory

(memory cells) or logic gates

Control Store

• Accessed through

MBR & MDR

• Holds microinstructions… NOT

ISA instructions

• Properties:

– 512 words

– 1 word = 36-bit microinstruction

• Has it’s own address register: MicroProgram

Counter (MPC)

• Has it’s own data register:

MicroInstruction

Register (MIR)

Important Difference….

• Main Memory:

– Program Instructions; executed sequentially(except for branches) : a = a+b; a = a-b; a = a + b;

• Control Memory:

– Control words contain information on how to control datapath for the operation.

– It is a Read Only Memory.

– Next Instruction is part of instruction is in the Control Memory

Micro Program Responsibilities

• The microprogram needs to:

• __________________

• ______________________________________

2 blanks