Slide 1

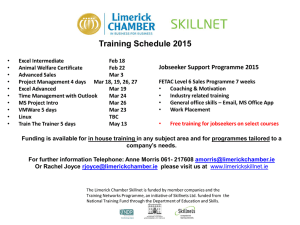

advertisement

AKT211 – CAO

03 – SAP-1

Ghifar

Parahyangan Catholic University

Sept 12, 2011

Outline

SAP-1

SAP-1

SAP-1

SAP-1

Characteristic

Architecture

Components

Instruction Set & Cycle

SAP Overview

• Simple As Possible

• Describe the simplest computer

workings

• Designed for academic purposes

only

• 1st step evolution to advanced

computer development

SAP-1 Characteristics

•

•

•

•

•

Hardwire Architecture

2 8-bit general registers

1 8-bit output registers

8-bit ALU (additional, subtraction)

4-bit instructions and 4-bits operands

– (cccc oooo)

• cccc = OP CODE

• oooo = OPERAND

• 16x8 address RAM for mixed

program and data

• 12 control signals

SAP-1 Architecture

CPEPL’MCE’ L’IE’IL’AEA SUEUL’BL’O

Program Counter

•

•

•

•

•

OUTPUT: 0000-1111 (0-F)

CLK: Clock cycle

CLR: reset output to 0000

Cp: (PC) (PC)+1

Ep: (PC) bus W

Memory Address Register (MAR)

•

•

•

•

INPUT: 4 bits

OUTPUT: 8 bits

CLK: Clock cycle

Lm:

– 0 : (MAR) bus W

Random Access Memory (RAM)

•

•

•

•

Store instruction & data

INPUT: 8 bits from MAR

OUTPUT: 8 bits to bus W

CE:

– 0 : (RAM) bus W

Instruction Register (IR)

• Read an instruction from

RAM

• INPUT: 8 bits from RAM

• OUTPUT:

– 4 bits to bus W

– 4 bits to CU

• LI :

– 0 : (IR) 8-bit input

• E I:

– 0 : (IR) 4-bit bus W

CU/Sequencer

• Control all execution flow

• INPUT: 4 bits from IR

• OUTPUT:

– 12 bits to be distributed to all

components

(microinstruction)

– CPEPL’MCE’ L’IE’IL’AEA

SUEUL’BL’O

Accumulator (ACC)

• Register buffer for storing

temporary computation

result

• INPUT : 8-bit from bus W

• OUTPUT :

– 8-bit to bus W

– 8-bit to ALU

• L’A :

– 0 : ACC bus W

• EA :

– 1 : ACC bus W

ALU

• Adder & Subtractor Only

• INPUT :

– 8-bit from ACC

– 8-bit from B register

• Output :

– 8-bit to bus W

• SU :

– 1 : substract

– 0 : add

• EU :

– 1 : ALU bus W

B Register

• Buffer for arithmetic

operation

• INPUT : 8-bit from bus W

• Output : 8-bit to ALU

• L’B :

– 0 : B bus W

Output Register

• Output port

– The processed data can be

accessed by output device via

this register

• INPUT : 8-bit from ACC via

bus W

• OUTPUT : 8-bit to output

device

• L’O :

– 0 : Output Register

bus W

Binary Display

• An output device that

consists of 8 LEDs

• can be changed with any

other output devices

Instruction Set

#

Mnemonic

Operand

Num

Operation

Opcode

1 LDA

1

Load memory data to acc.

0000

2 ADD

1

Add acc. with memory data

0001

3 SUB

1

Sub acc. with memory data

0010

4 OUT

0

Move out the acc. Data

1110

5 HLT

0

Stop program

1111

Instruction Cycle

• Fetch Cycle

– T1 (Address State)

– T2 (Increment State)

– T3 (Memory State)

• Execution Cycle

– 3 step (T4, T5, T6), but the task of

each steps depends on the

instruction

Fetch Cycle - T0 (Initial State)

CON=

CP

EP

L’M

C’E

0

0

1

1

L’I E’I

1

1

L’A

EA

SU

EU

L’B

L’O

1

0

0

0

1

1

T1 (Address State)

CON=

CP

EP

L’M

C’E

0

1

0

1

L’I E’I

1

1

L’A

EA

SU

EU

L’B

L’O

1

0

0

0

1

1

T2 (Increment State)

CON=

CP

EP

L’M

C’E

1

0

1

1

L’I E’I

1

1

L’A

EA

SU

EU

L’B

L’O

1

0

0

0

1

1

• Increment the value of PC

T3 (Memory State)

CON=

CP

EP

L’M

C’E

0

0

1

0

L’I E’I

0

1

L’A

EA

SU

EU

L’B

L’O

1

0

0

0

1

1

Exectution Cycle (LDA Instruction)

• For LDA instruction, only T4 and

T5 states that will be actived

– T4 : memory address is sent from

IR to MAR

– T5 : data from memory is fetched

and send to ACC

– T6 : do nothing ! = T0

T4 (send IR value to MAR)

CON=

CP

EP

L’M

C’E

0

0

0

1

L’I E’I

1

0

L’A

EA

SU

EU

L’B

L’O

1

0

0

0

1

1

T5 (send RAM data to ACC)

CON=

CP

EP

L’M

C’E

0

0

1

0

L’I E’I

1

1

L’A

EA

SU

EU

L’B

L’O

0

0

0

0

1

1

Execution Cycle

• What about the execution cycle

for ADD / SUB / OUT instruction

?

SAP-1 Programming

• Problem :

– Write a program using SAP-1

computer that computes the

following operation :

16+20+24+28-32

SAP-1 Programming (2)

• Solution :

– Assign the data memory with this

data:

R9=00010000(16),RA=00010100(20),

RB=00011000(24),RC=00011100(28),

RD=00100000 (32)

– The codes:

1.

2.

3.

4.

5.

6.

7.

LDA R9

ADD RA

ADD RB

ADD RC

SUB RD

OUT

HLT

SAP-1 Programming (3)

PROGRAM/DATA MEMORY

Press start button

(PC) 0000

Start

LDA R9

(MAR) (PC)

R(MAR) 0000 1001

(PC) (PC)+1

IR 0000 1001

(MAR) IR(low)

(ACC) R(MAR)

{NOOP}

ADD RA

(MAR) (PC)

R(MAR) 0001 1010

(PC) (PC)+1

IR 0001 1010

(MAR) IR(low)

(B) R(MAR)

(ACC) (ACC)+(B)

ADD RB

.

.

.

fetch T1

fetch T2

fetch T3

exec T4

exec T5

exec T6

fetch T1

fetch T2

fetch T3

exec T4

exec T5

exec T6

(MAR)= 0000

(R) = (R0)

(PC) = 0001

(MAR)= 1001

(ACC)= 16

(MAR)= 0001

(R)= (R1)

(PC) = 0010

(MAR)= 1010

(B)= (RA)

(ACC)= 16+20

R0

R1

R2

R3

R4

R5

R6

R7

R8

R9

RA

RB

RC

RD

RE

RF

-

0000

0001

0001

0001

0010

1110

1111

xxxx

xxxx

0001

0001

0001

0001

0010

xxxx

xxxx

1001

1010

1011

1100

1101

xxxx

xxxx

xxxx

xxxx

0000

0100

1000

1100

0000

xxxx

xxxx

(LDA R9)

(ADD RA)

(ADD RB)

(ADD RC)

(SUB RD)

(OUT)

(HLT)

(16)

(20)

(24)

(28)

(32)

Busicom 141-PF

• 1st ever with a

microprocessor powered

by Intel 4004

• more instruction sets

compared to SAP-1

(46 : 5)

• Output : printer

THANK YOU