Machine Instructions/Assembly Language

advertisement

Machine Instructions

Operations

1

ITCS 3181 Logic and Computer Systems 2015 B. Wilkinson Slides4-1.ppt

Modification date: March 18, 2015

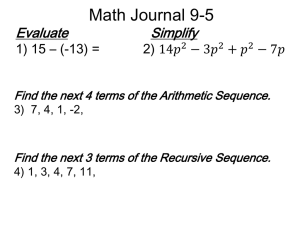

Instructions

We will use a simple instruction formats of a so-called reduced

instruction set computer (RISC), which has the characteristics:

• Simple, fixed length instruction format

• A few addressing modes

• Limited number of operations

• Designed to achieve high speed of execution

It was recognized in the 1980’s that such processors would

actually execute programs faster that the prevalent CISCs

(complex instruction set computers).

2

Instruction format

Our instruction format is quite similar to the G4/G5 PowerPC

and SUN Sparc processors and also similar but not identical to

that used in the assembly language simulator in the labs.

Intel 64/IA32 processor family -- uses a very complex and

archaic instruction format, based upon the early 8086

processor (which was themselves loosely based upon even

earlier Intel processors).

However Intel processors now convert this complex instruction

format (CISC) internally to simpler RISC formats for

performance reasons.

3

Some Key Features of Processor Used

1.Thirty-two 32-bit integer registers called R0 to R31

2. One register, R0, holds zero permanently

R31

R30

R29

R28

3 All arithmetic done only between registers:

- Three-register format

op-code, destination register, source register 1, source register 2

or

- Immediate addressing

op-code destination register, source register, constant

4. Memory operations limited to:

load register, and

R4

R3

R2

R1

R0

0000 … 0000

R31 holds return

address for

procedures.

R29 is a stack

pointer see later.

store register

using register indirect addressing plus offset only:

LD/LB destination register, offset[source register]

ST/SB source register, offset[source register]

4

Data Transfer

Instructions that copy the contents of one location to another

location.

Examples

Instruction

MOV R1,R2

LD R3,100[R2]

ST [R5],R4

Comments

;R1 = R2

;Contents of memory whose address is

;given by 100 + R2 copied to R3.

;Contents of R4 copied to memory loc.

;whose address held in R5. (Offset = 0)

Note LD and ST cause 32-bit transfers.

Use LB and SB to cause 8-bit transfers.

5

Arithmetic Instructions

Performs an arithmetic operation such as addition, subtraction,

multiplication or division.

Examples

ADD R1,R2,R3

SUB R5,R4,3

;R1 = R2 + R3

;R5 = R4 – 3

For literals (immediate addressing) differences in assembly language

notation. Might be written as:

SUB R5,R4,#3

;R5 = R4 - 3

SBI R5,R4,3

;R5 = R4 - 3

or

depending upon assembly language.

6

Logical Instructions

Performs bit-wise logical operation such as AND, OR, exclusiveOR, or NOT. AND, OR, exclusive-OR operate upon pairs of bits of

two operands.

Bit-wise AND, OR, Ex-OR, and NOT are available in C and Java

(although you probably did not come across them!):

C/Java Language Examples

y=y&1

z=z|2

;bit-wise AND y with the number 1

;bit-wise OR z with the number 2

7

Machine Instruction Examples

AND R1,R2,R3

if

then

R2 = 10100010100101011000010100001111

R3 = 01011011111010100010100010111010

R1 = 00000010100000000000000000001010

OR R1,R2,R3

if

then

;R1 = R2 “AND” R3

;R1 = R2 “OR” R3

R2 = 10100010100101011000010100001111

R3 = 01011011111010100010100010111010

R1 = 11111011111111111010110110111111

8

Shift Instructions

Moves the bits of a location one or more places left or right.

Again available in C/Java (although you probably did not come across

them!):

C/Java language Examples

y = y << 1

;shift y 1 place left 1

z = z >> 2

;shift z 2 places right

9

Machine Instruction Examples

Examples

SHL R1,R1,1

X = 0 or 1 see next slide

;Shift R1 left one place

1 0 1 0 1 1 1 1 0 1 0 1 ... 1 1 0 1

0 1 0 1 1 1 1 0 1 0 1 ... 1 1 0 1 X

SHR R1,R1,1 ;Shift R1 right one place

1 0 1 0 1 1 1 1 0 1 0 1 ... 1 1 0 1

X 1 0 1 0 1 1 1 1 0 1 0 1 ... 1 1 0

10

Arithmetical and Logical Shifts

Two types of shift usually provided:

“Logical” shift (SHL, SHR)

Fill free end with 0, i.e. X = 0.

“Arithmetic” shift (SAL, SAR)

Arithmetic shifts multiple/divide by 2.

Arithmetic shift right maintains value of sign bit, i.e. X = value of

original sign bit.

11

Example

Starting with a number 9

000 ... 0001001

Shift arithmetic left one place. Get 18

000 ... 0010010

Shift arithmetic right two places. Get 4

i.e. lost the 0.5.

000 ... 0000100

12

Note: Java has logical shift right - called unsigned right

shift, >>>.

Example

x = x >>> 2;

13

Question

What is the difference, if any, between arithmetic shift left and

logical shift left, i.e. what is the difference, if any, between:

SHL R1, R1, 1

and

SAL R1, R1, 1

Answer

Arithmetic shift left same as logical shift left (except

arithmetic overflow may be detected).

14

Question

What is the effect of the sequence?

SAR R1, R1, 1

SAL R1, R1, 1

Answer

Makes number even if odd, i.e. 5 would become 4

15

Rotate Instructions

Moves bits of location one or more places left of right in a circular

fashion.

Examples

ROL R1,R1,1 ;Rotate R1 left one place

1 0 1 0 1 1 1 1 0 1 0 1 ... 1 1 0 1

0 1 0 1 1 1 1 0 1 0 1 ... 1 1 0 1 1

ROR R1,R1,1 ;Rotate R1 right one place

1 0 1 0 1 1 1 1 0 1 0 1 ... 1 1 0 1

Version of

rotate exists

where the

rotate

passes thro a

Carry flag

within the

condition

code

register, see

later about

the CCR

1 1 0 1 0 1 1 1 1 0 1 0 1 ... 1 1 0

16

Control Flow

Compilers must translate statements such as:

if ((x != y) && (z < 0)) {

a = b + 5;

b = b + 1;

}

into machine instructions.

Unreasonable to try to provide a unique machine instruction for this

IF statement because of the vast number of possible IF statements.

Need to extract essential primitive operations for machine

instructions.

17

Decompose into simple IF statements of the form:

if (x relation y) goto L1;

where:

relation is any of usual relations allowed in high level languages

(<, >, >=, <=, ==, !=)

L1 is a label prefixed to an instruction to identify it.

18

i.e. translate

if ((x != y) && (z < 0)) {

a = b + 5;

b = b + 1;

}

...

into

Label

L1:

if (x == y) goto L1;

if (z >= 0) goto L1;

a = b + 5;

b = b + 1;

...

19

Several ways of implementing the IF statement.

if (x relation y) goto L1;

Here we will consider two ways:

1. Using one branch instruction

Used in our design and lab.

2 Using two instructions, one to determine whether relationship

is true, and another to branch to L1 if true.

Used by Intel and based upon a very old instruction set, so we

have to know about it.

20

1. Using one branch instruction

Single “branch” machine instruction compares two registers and

goes to the labeled location if the condition is true, i.e.

Bcond Rs1, Rs2, L1

changes the execution sequence to the instruction labeled L1 if

Rs1 cond Rs2 is true, where cond can be any of six possible

conditions, and Rs1 and Rs2 can be any of the 32 registers.

21

Conditional Branch Instruction op-codes

Bcond

Bcond

BL

BG

BGE

BLE

BE

BNE

Condition

High level language notation

Branch if less than

<

Branch if greater than

>

Branch if greater or equal to

>=

Branch if less or equal to

<=

Branch if equal

==

Branch if not equal

!=

22

Example

To implement

if (x == y) goto L1;

.

.

.

L1:

by a single machine instruction, we get:

BE R1,R2,L1

.

.

.

L1:

where the compiler allocates R1 for x and R2 for y.

23

Machine Instruction Encoding

The instruction

Bcond Rs1,Rs2,L1

requires an op-code (Bcond), the two source registers Rs1 and Rs2,

and L1 to be specified.

Op-code

Bcond

Rs1

Rs2

L1

Note: Bcond is either BL, BG, BGE, BLE, or BNE

24

Specifying “target” location L1

Several ways L1 could be specified in instruction:

(a) Absolute (direct) addressing

Address of L1 held in instruction.

(b) (PC) Relative addressing Distance from branch instruction to

labeled instruction stored in instruction.

Program counter, PC, holds the location of the instruction to be fetched from

memory next, see later.

25

(a) Absolute (direct) addressing

BE R1,R2,120

.

.

.

L1:

;location 120 say

Op-code

Bcond

Rs1

Rs2

120

Note: Absolute addressing will not used in our design.

26

(b) (Program counter) Relative Addressing

Specify target location as number of instructions from branch

instruction.

Reasoning:

• Mostly, conditional branch instructions used to implement small

changes in sequences or program loops of relatively short length,

so distance from branch to target (label) quite small compared to

full address of the labeled instruction.

• Also good programming practice to limit sequence changes to

short distance from current location to avoid difficult to read code.

• Also makes code relocatable. (i.e. code can be loaded anywhere in

memory without altering branch instructions.)

27

PC-Relative Addressing

The number of locations to the target is held in the instruction as

an offset.

Branch op-code

Offset

Offset is added to the program counter to obtain the “effective

address” of the target location.

28

(PC) Relative Addressing

Offset/displacement

BE R1,R2,+30 ; location 90 say

.

.

.

30

L1:

; location 120 (90 + 30)

Op-code

Bcond

Rs1

Rs2

We will deal with how to implement this later. Note: PC incremented by the size of

instruction, 4 here, after instruction fetched from memory in most implementations.

30

29

Question

How would one code:

if (x > y) x = 10;

with machine instructions where x and y are stored in R2 and R3

respectively?

Answer

BG R2, R3, L1

MOV R2, 10

L1:

30

2. Using two instructions, one to determine whether

relationship is true, and another to branch to L1 if true.

In this approach, we determine whether the Boolean condition in

if (x relation y) goto L1;

is true by subtracting y from x and recognizing whether the result is

positive or negative, zero, or not zero:

relation

<

>

>=

<=

==

!=

x-y

negative

positive and not zero

positive or zero

negative or zero

zero

not zero

31

Condition Code Register (CCR)

Contains a set of flags (single bits) used to be able to recognize the

different possible relationships (<, >, >=, <=, ==, !=) after the

previous arithmetic operation.

Flags in condition code register indicate a particular aspect of the

result of the last arithmetic instruction, i.e. positive or negative,

zero or not zero, …

32

Sign Flag (S or N flag)

(positive or negative)

Indicates whether previous arithmetic result is negative or positive.

S = 1 for negative result

S = 0 for positive result.

S is actually the most significant (sign) bit of the result of the

previous arithmetic operation

33

Zero Flag

Zero flag, Z:

Z = 1 for result = 0

Z = 0 for result != 0

(Note zero is a positive number.)

34

Condition Code Register

Condition Code register normally closely linked to the ALU

(Arithmetic and Logic Unit):

Processor

Internal buses

S – Sign flag

Z – Zero flag

Source operands

ALU

Answer

Condition code

register

S

Z

Sample allocation of bits

(There are other bits used not yet described)

35

Using Condition Code Register

Decompose IF statement such as:

if (x relation y) goto L1

into two sequential operations:

1. Subtract y from x which sets condition code register according

to result

2. Read condition code register and “branch” to L1 if specific

condition indicated

36

Step 1 Subtract and Set Condition Code Register

All arithmetic instructions set condition code register according to

the result of the arithmetic operation, but a compare instruction

specifically provided, similar to a subtract instruction except result is

not stored anywhere, only the CCR flags set according to the result.

Example

CMP R1, R2

;R1 - R2, sets CCR flags

37

Step 2 Reading Condition Code Register and

Branching

A conditional branch instruction used to examine the values stored in

the condition code register to determine whether the specific

condition exists and to branch if it does.

All six conditions usually available:

BL

BG

BGE

BLE

BE (or BZ)

BNE (or BNZ)

Branch if less than

Branch if greater than

Branch if greater or equal to

Branch if less or equal to

Branch if equal

Branch if not equal

38

Example

Suppose x held in R1 and y held in R2. The if statement:

if (x == y) goto L1;

could be implemented by sequence of two instructions, CMP and

BE:

CMP R1,R2

BE L1

;Compare contents of R1, R2 (x, y)

;Go to L1 if equal

L1:

39

Example

Suppose x held in R1 and y held in R2. The if statement:

if (x == y) goto L1;

could be implemented by sequence of two instructions, CMP and BE:

Condition code register

Z = 1 if R1 - R2 = zero otherwise Z = 0

S

Z

Write

CMP R1,R2

BE L1

;Compare contents of R1, R2 (x, y)

;Go to L1 if equal

L1:

40

Example

Suppose x held in R1 and y held in R2. The if statement:

if (x == y) goto L1;

could be implemented by sequence of two instructions, CMP and

BE:

Condition code register

Z = 1 if R1 - R2 = zero otherwise Z = 0

S

Z

Read

Write

CMP R1,R2 ;Compare contents of R1, R2 (x, y)

BE L1 ;Go to L1 if equal

L1:

41

More complex constructions

if - then - else

Suppose we had to implement:

if (a < b) c = a; else a = c;

...

assuming that the variables a, b, and c are assigned to registers R1,

R2, and R3 respectively.

42

Leads to:

CMP R1,R2

BL L1

MOV R1, R3

L1:

L2:

MOV R3,R1

...

;Compare R1, R2 (x, y)

;Go to L1 if a less than b

;a = c

Skip over c = a, unconditionally

;

c = a;

We need to alter the instruction sequence unconditionally. With the

instructions we know about so far, it could be done with:

CMP R1, R1

BE L2

;if (x == x) goto L2;

but there is a special instruction called a jump instruction to do it.

43

JUMP Instructions

Causes an unconditional change of execution sequence to a new

location.

Necessary to implement more complicated IF constructs, FOR, and

WHILE loops.

Using J as the opcode mnemonic, the jump instruction is:

J L1

;goto to L1

44

With jump instruction:

L1:

L2:

CMP R1,R2

BL L1

MOV R1, R3

J L2

Go to L2

MOV R3,R1

...

;Compare R1, R2 (x, y)

;Go to L1 if a less than b

;a = c

;c = a;

45

For loops

Suppose we had to implement the C/Java code sequence:

for (i = 1; i < 10; i++)

a = a * i;

...

Let us assume i is held in register R1, and x is held in register R2.

Possible solution

L2:

L1:

MOV R1, 1

CMP R1,10

BGE L1

MUL R2,R2,R1

ADD R1,R1,1

J L2

...

;i = 1

;Compare R1 with 10

;Go to L1 if end of loop

;a = a * i

;increment i

46

Jump Instruction with Register-Indirect

Addressing

An “address register” specified in instruction holds the address of

the location holding the next instruction to be executed.

Examples

J [R1]

;jump to location whose address in R1

J 100[R1]

;jump to location whose address given

;by R1 + 100

Target address specified as absolute address, rather than relative

address.

Used to implement high level language SWITCH statements. Also

return from procedures see next section.

47

Avoiding Condition Code Register

It turns out that the CCR approach has disadvantages when one

tries to implement a high performance processor, and does not

really suit RISC designs.

Makes it much more difficult to design a high-performance

processor.

CCR approach requires two sequential instructions with no

instructions allowed in between that affect the CCR. (All

arithmetic/logic instruction affect CCR.)

For the most part we will use single instruction in our designs.

An alternative to the CCR is to use a general purpose register in

place of CCR to hold “conditions.”

48

Simplified version of branch instruction

Bcond Rs1, L1

where Rs1 is compared against zero rather than Rs2.

Do subtract operation previous to this instruction, placing result

in Rs1.

49

Question

How would one code:

if (x > y) goto L1;

where x and y are stored in R2 and R3 respectively using previous

simplified version of branch instruction?

Answer

SUB R4, R2, R3

BG R4, L1

50

One version of branch instruction in MIPS

processor (Lab)

Use a general purpose register set to 1 of 0 if one register is less

than another.

SLT Rs1,Rs2,Rs3

;Rs1 = 1 if Rs2 < Rs3

together with a simple branch instruction that only tests condition

equal or not equal.

51

Questions

52