instruction

advertisement

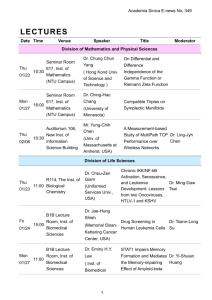

ARM CPU Internal I Prof. Taeweon Suh Computer Science Education Korea University Overview • For the sake of your understanding, we simplify the CPU and its system structure Real-PC system CPU FSB (Front-Side Bus) Main Memory (DDR) Address Bus Simplified ARM CPU North Bridge Data Bus DMI (Direct Media I/F) Memory (Instruction, data) South Bridge 2 Korea Univ Actual ARM Connection • ARM CPU has separate connections to memory (caches) ARM920T Instruction fetch Address Bus Instruction Cache Data Bus Address Bus ARM CPU core Address Bus Data Bus Data Cache Data Bus Memory Instruction/ Data access Data access 3 Korea Univ Overview • Microarchitecture is composed of datapath and control Datapath operates on words of data • Datapath elements are used to operate on or hold data within a processor • Datapath elements include the register file, ALU, muxes, and memory Control tells the datapath how to execute instructions • Control unit receives the current instruction from the datapath and tells the datapath how to execute that instruction • Specifically, the control unit produces mux select, register enable, ALU control, and memory write signals to control the operation of the datapath • Essential ARM instructions Data processing instructions: add, sub, cmp, and, or Memory access instructions: ldr, str Branch instructions: b, bl 4 Korea Univ Instruction Execution in CPU • Generic steps of the instruction execution in CPU Fetch uses the program counter (PC) to supply the instruction address and fetch instruction from memory Decoding decodes instruction and reads operands • Extract opcode: determine what operation should be done • Extract operands: register numbers or immediate from fetched instruction Execution • Use ALU to calculate (depending on instruction class) Arithmetic or logical result Memory address for load/store Branch target address ARM CPU core Fetch with PC PC = PC +4 • Access memory for load/store Address Bus Data Bus Address Bus Next Fetch Execute • PC target address or PC + 4 Decode Instruction/ Data Memory Data Bus 5 Korea Univ Instruction Fetch ARM CPU core Increment by 4 for the next instruction 4 Add Memory reset clock Address PC Out 32 instruction 32-bit register (flip-flops) • What is PC on reset in ARM? PC = 0x0000_0000 6 Korea Univ Memory • Memory is classified into RAM (Random Access Memory) and ROM (Read-Only Memory) RAM is classified into DRAM (Dynamic RAM) and SRAM (Static RAM) DDR is a kind of DRAM • DDR is a short form of DDR (Double Data Rate) SDRAM (Synchronous DRAM) • DDR is used as main memory in modern computers 7 Korea Univ Simple ARM Test Code assemble 8 Korea Univ Instruction Decoding • Instruction decoding separates the fetched instruction into the fields Opcode determines which operation the instruction wants to do • Control logic should be designed to supply control signals to datapath elements (such as ALU and register file) Operands • Register numbers in the instruction are sent to the register file • Immediate field is either sign-extended or zero-extended depending on instructions* *It seems immediate is zero-extended in ARM case. If you write “add r1, r2, #-12”, assembler generates “sub r1, r2, 12”. The shifter operand could be “logical (or arithmetic) shift right a register by immediate. In this case, the register is zero-filled or signed-filled in the shifted vacant bits 9 Korea Univ Schematic with Instruction Decoding ARM CPU Opcode Control Unit RegWrite Register File Inst[19:16] (=Rn) R0 Inst [3:0] (=Rm) R1 R2 32 Rn 32 Rm R3 instruction Inst[15:12] (=Rd) wd 32 … R14 R15 (PC) RegWrite Memory imm 8 zeroextended 4 32 Add Out 32 reset clock 10 PC Address Korea Univ Instruction Execution #1 • Arithmetic and logical instructions Examples: add, adc, sub, sbc, cmp, mov, and, or … Two source operands • One is always a register • The other has two basic forms: Immediate or register (optionally shifted) add opcode: 0100 add r1, r2, r3 sub opcode: 0010 sub r1, r2, r3 11 # r1 = r2 + r3 # r1 = r2 – r3 Korea Univ Data Processing Instruction Formats Source: ARM Architecture Reference Manual 12 Korea Univ Schematic with Instruction Execution #1 ARM CPU opcode Control Unit ALUSrc RegWrite Register File Inst[19:16] (=Rn) R0 Inst [3:0] (=Rm) R1 R2 32 Rn ALUSrc R3 instruction Inst[15:12] (=Rd) wd 32 … 32 ALU Rm mux R14 R15 (PC) RegWrite Memory imm 8 zeroextended 4 32 Add Out 32 reset clock 13 PC Address Korea Univ Instruction Execution #2 • Memory access instructions ldr, str instructions ldr R1, [R2, #4] // R1 <= [R2 + 4] str R1, [R2,R3] 14 // [R2 + R3] <= R1 Korea Univ Memory Access Instruction Formats • Load and Store Word or Unsigned Byte instructions Source: ARM Architecture Reference Manual 15 Korea Univ Schematic with Instruction Execution #2 ARM CPU opcode MemWrite MemtoReg 8-or-12 ALUSrc RegWrite Control Unit Inst [3:0] (=Rm) R0 32 Inst[15:12] (=Rd) wd 32 … WriteData Rn ReadData R1 R2 ALUSrc R3 instruction Memory Rd Register File Inst[19:16] (=Rn) MemWrite 32 ALU Address Rm MemtoReg mux R30 R31 mux 8-or-12 Memory imm 8 12 ldr str zeroextended 4 Out 32 R1, [R2, #4] // R1 <= [R2 + 4] R1, [R2, R3] // [R2 + R3] <= R1 32 Add reset clock 16 PC Address Korea Univ Instruction Execution #3 • Execution of the branch and jump instructions b, bl instructions b target (offset) Destination = (PC + 8) + sign-extend (imm << 2) 17 Korea Univ Schematic with Instruction Execution #3 (B) ARM CPU opcode branch Control Unit MemWrite Memory Register File Inst[19:16] (=Rn) R0 Inst [3:0] (=Rm) R1 R2 Rd 32 Rn ReadData ALUSrc R3 Inst[15:12] (=Rd) instruction wd 32 … WriteData 32 ALU Address Rm MemtoReg mux R14 R15 (PC) mux 8-or-12 imm 12 imm 24 zeroextended branch mux Add 32 Memory 4 32 Add Out Sign extension <<2 reset clock 32 18 Note that Branch Destination = (PC+8) + (sign-extend) (imm << 2)} PC Address Korea Univ