Xilinx CPLD Introduction: Overview & Design

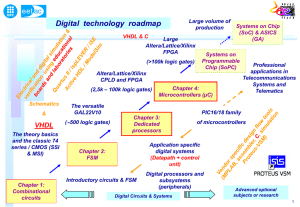

advertisement

Introduction to Xilinx CPLDs Agenda • • • • • • • CPLD Introduction XC9500 Family Overview CoolRunner XPLA3 Overview CoolRunner-II Overview IQ Products for Automotive and Industrial Software Updates and Online Support Customer Success Stories Introduction to CPLDs 2 Complex Programmable Logic Device macrocells interconnect macrocells A hybrid of PLD blocks & interconnect for mid-size logic designs Introduction to CPLDs 3 Specification CPLD Design Flow libraries HDL Schematic Capture Synthesis netlist CPLD Design Flow Gates of the design ... Verification Simulation 0100 1110 1100 1111 test vectors Implementation Translate Fitting Download/ Program Timing Analyzer Back-Annotation device System Debug printed circuitboard Introduction to CPLDs 4 ... are “fitted” to the CPLD High Performance • Pin-to-Pin combinatorial • Maximum registered delay frequency – Time from input, thru interconnect to output (ns) CPLD – Fastest operation of flip-flops (MHz) CPLD Macrocell TPD (ns) Introduction to CPLDs 5 fMAX (MHz) Wide Package Offering • • • • High pin count package for lots of I/Os Maximum logic with minimal I/Os Logic consolidation for space (vs. discrete devices) Lower cost packaging A smaller CPLD package means a smaller board! CPLD Introduction to CPLDs 6 CPLD CPLD Voltage Integration 5v, 3.3v, 2.5v, 1.8v and 1.5v • 3.3v & 2.5v is the current market trend moving to 1.8v and below for portable and low power applications • Cost reduction to eliminate 5v supply and regulators with 5v tolerance • Some components will not migrate to 3.3v or below • Need to interface with 3.3v, 2.5V, 1,8v and/or 1.5v components CPLD 3.3/2.5/1.8v 3.3v* 5v* 5v* 5v* 5v* 5v* 1.5v* 1.8v* 2.5v* * 3.3v CPLD required to interface with 5v, 3.3v & 2.5v components * 2.5v CPLD required to interface with 3.3v, 2.5v & 1.8v components *1.8v CPLD required to interface with 3.3v, 2.5v, 1,8v & 1.5v components Introduction to CPLDs 7 System Integration Advantage Introduction to CPLDs 8 System Level Savings • High volume economies of scale – Single chip for multiple system solutions • Increase volume means reduction in all related costs • Reference designs – Minimize risk and shorten design cycle • Lowest cost per I/O – Examples include • On The Fly (OTF) reconfiguration – Two devices for the price of one Introduction to CPLDs 9 Designers Need Low Power • Longer lasting battery life • Lower overall system cost (eliminate fans/ reduce power supplies) • Increased system reliability • Fits into hand-held applications Introduction to CPLDs 10 CPLD Advantage over Discrete Logic High Speed CMOS Logic 74HC373 74HC373 XPLATM Architecture 74HC373 74HC137 SOL 24 74HC137 74HC374 74HC374 74HC374 TQFP 100 74HC137 TSSOP 24 74HC157 74HC157 74HC00 74HC00 Equivalent to 74HC20 74HC20 74HC138 74HC21 74HC138 74HC21 XCR3128XL 74HC138 Or XCR3064 XL SOL 24 3.3V parts in the same package bridging two densities for added design flexibility Discrete Part No. Function 74HC373 Octal D-type transparant latch 3 74HC374 Octal D-Type Flip Flop 3 74HC157 Quad 2-input multiplexer 2 74HC00 Quad 2 input NAND 2 74HC21 Dual 4 input AND 2 74HC20 Dual 4 input NAND 2 74HC138 3 to 8 line decoder 3 Introduction to CPLDs 11 Qty Real design example: Aircraft Passenger Handset - Smaller PCB with less layers (lower cost) - 7 to 3 layers! - One part to purchase & stock, less inventory - One part to pick and place in manufacture, saving time - Design can be changed and enhanced without PCB re-layout - even in the field - Stock and purchase one part instead of 17 in this example! Units Shipped Xilinx CPLD High Volume Shipments 1996 1997 1998 1999 2000 2001 2002 • Xilinx currently ships >10M CPLD units per Qtr • WW CPLD market share growing at >1% per Qtr Introduction to CPLDs 12 2003 est CPLD Product Portfolio – 1.8V RealDigital core – 1.5V - 3.3V I/O – SSTL, HSTL, LVCMOS, LVTTL – Lower power • DataGATE – Clocking features • Clock Divide • CoolCLOCK • DualEDGE – I/O banking Introduction to CPLDs 13 – – – – 3.3V core 2.7V - 5V I/O LVCMOS, LVTTL Low power • Fast Zero Power – – – – 2.5V core 1.8V - 3.3V I/O LVCMOS, LVTTL I/O banking – 3.3V core – 2.5V - 5.0V I/O – LVCMOS, LVTTL Quick Design Capability with CPLDs Product Lifetime Dynamics Units Cellular Target high volume, short production life applications PDA PC Games TV 1 Years in Production 2 New products stay in volume for shorter periods, Time To Market is critical! Introduction to CPLDs 15 ASIC Development Take Too Long! • Product life cycles maybe shorter than ASIC development time – Multiple ASIC spins may miss the market window – Smaller than expected run rates may not justify the ASIC development cost • Long ASIC development times do not allow last minute design revision changes – Revisions leave little time to run in production – Programmable logic allow customers to address market changes quicker Introduction to CPLDs 16 ASICs Give Designers Only ONE Chance Freeze design here No chance for last minute design changes ASIC Spec Design & Verification Silicon Prototype System Integration Silicon Production First Ship Re-programming allows last minute design changes CPLD Spec Design & Verification System Integration First Ship Freeze design here CPLD flexibility allow performance analysis and late HW/SW changes meeting customer needs and improves Time To Market with faster, lower risk designs Introduction to CPLDs 17 CoolRunner Reference Designs • Shorten design cycle time – Eliminate code porting costs for next design cycle • Re-use of HDL is reliable and stable • Minimize design risk by using reference designs – Availability of reference designs prepares you for unexpected system changes • Update main processor but it does not incorporate correct bus interface • Further improve customer’s Time To Market – Proven designs for quick turn requirements Introduction to CPLDs 18 Faster Designs with FREE CoolRunner Reference Designs Application PDA Datacom Bus Interface Memory Wireless Multimedia Microcontroller Reference Design XPATH Module Design Springboard Module Design 8 Channel DVM Springboard SECDED N x N Crosspoint Switch IrDA and UART UARTs 16b/20b Encoder/Decoder SPI Compact Flash Interface I2C Bus Controller SMBus Controller Manchester Encoder/Decoder NAND Interface Interface to DDR SDRAM Wireless Transceiver MP3 Player 8-bit Microcontroller 8-bit Microcontroller 8051 Microcontroller Interface Reference Number XAPP356 XAPP147 XAPP146 XAPP383 XAPP380 XAPP345 XAPP341 XAPP336 XAPP386 Coming soon XAPPXXX XAPP333 XAPP353 XAPP339 XAPP354 XAPP384 XAPP358 XAPP328 XAPP387 XAPP387 XAPP349 Language Macrocell VHDL Pocket C, VHDL Pocket C, VHDL VHDL VHDL VHDL or Verilog VHDL or Verilog VHDL VHDL VHDL VHDL or Verilog VHDL VHDL or Verilog VHDL or Verilog VHDL VHDL VHDL VHDL & C VHDL & C VHDL 225 67 184 66 193 87 61 76 128 131 158 55 9 156 219 107 212 57 Target Device XC2C384 XC2C128 XC2C256 XC2C128 XC2C256 XC2C128 XC2C128 XC2C128 XC2C256 XC2C128 XC2C256 XC2C256 XC2C64 XC2C32 XC2C256 XC2C256 XC2C256 XC2C128 XC2C256 XC2C64 Free VHDL design code: www.xilinx.com/products/xaw/coolvhdlq.htm Introduction to CPLDs 19 % Utilized 58 52 71 52 75 67 47 59 50 51 61 85 28 60 86 84 83 89 CoolRunner-II Design Kit Introduction to CPLDs 20 Development Board & Cable Support Xilinx CPLD Family Manufacturer XC9500 Memec XC9500 CoolRunner XPLA3 Memec Memec CoolRunner XPLA3 CoolRunner XPLA3 Memec Memec CoolRunner XPLA3 CoolRunner II CoolRunner II Memec Memec Memec CoolRunner XPLA3 (XCR3256XL) Silica CoolRunner II All CPLDs Silica Xilinx CoolRunner II Xilinx Description XC9572XL Deveolpment Board XC9572XL Dev board, JTAG cable & WebPACK CD XPLA3 Development Board XPLA3 Dev Board, WebPACK CD & JTAG Cable Sprinboard Development Board Sprinboard Development Board, WebPACK CD, JTAG cable, Pocket C Software CoolRunner II Development Kit Part Number DS-KIT-95XL DS-KIT-95XL-PAK DS-KIT-XPLA3 DS-KIT-XPLA3-PAK DS-KIT-SPRINGBOARD DS-KIT-SPRINGBOARDPAK DS-KIT-2C64 CoolRunner II Development Kit, WebPACK CD & JTAG Cable DS-KIT-2C64-PAK XPLA3 Evaluation kit with JTAG cable ADS-XLX-X3-EVL CoolRunner II Evaluation board XC2C64 & XC2C256 ADS-XLX-CR2-EVL JTAG Parallel Cable HW-JTAG-PC CoolRunner II Demo Board XC2C64 Note: There may be regional variations because of different mains voltages - check locally for full part number Introduction to CPLDs 21 CPLD Software Improvements in 6.1 • Ease of use – Improved CPLD process flow • Single process (Implement Design) will pull the design through the entire fitting process • Granular control still possible for power users by expanding individual processes XC9500XL / XV – New design creation aids Product Overview • New project wizard leads the user through the project creation process • Add existing source / Create new source processes - assist in getting started faster – Centralized process properties menu • Web Update – Built in utility checks for service packs and supplemental CPLD updates – Downloads and installs update in single step Introduction to CPLDs 22 File Number Here Xilinx CPLD Process Leadership Non-Volatile Technology Year used in Memories Year used in SPLD/CPLD SPLD/CPLD Pioneer Bipolar Fuse 1973 1978 MMI (AMD) EPROM 1979 1984 Altera EP-series 5V EEPROM 1986 1991 Lattice ispLSI 5V FLASH 3.3V FLASH 2.5V FLASH 1990 1993 1996 1995 1998 2000 Xilinx XC9500 Xilinx XC9500XL Xilinx XC9500XV Introduction to CPLDs 23 Higher Voltage CPLD Solutions To Fit Every Need • • • • • 5 / 3.3 / 2.5V core 36-288 macrocells High Performance Superior pin-locking Low cost Introduction to CPLDs 24 XC9500 Families XC9500 XC9500XL XC9500XV 5V core 3.3V core 2.5V core XC9500/XL/XV Family Features Overview CPLD Designer Needs High Performance Time to Market Fit in Existing Flow Package offering 5v,3.3v & 2.5v Lowest cost Introduction to CPLDs 25 • • • • • • • • • • High fMAX = 278 MHz Fast TPD = 3.5nS Instant productivity software tools Best pin-locking capability Best ISP/JTAG support Support for all ATE manufacturers Advanced packaging including CSP XC9500XL for 3.3v (5v tolerant & 2.5v I/O) XCR9500XV for 2.5v (1.8v & 3.3v I/O) Best CPLD pricing in the industry! XC9500XL / XV Families 3.3v ISP 2.5v ISP Macrocells Usable Gates tpd (ns) XC9500XL tpd (ns) XC9500XV Registers fSYSTEM XC9500XL XC9500XV Packages XC9536XL XC9536XV 36 800 5 4 36 178 200 XC9572XL XC9572XV 72 1600 5 5 72 178 178 PC44 PC44 CS48 CS48 VQ44* VQ44* VQ64 VQ64 TQ100 XC95144XL XC95144XV 144 3200 5 5 144 178 178 XC95288XL XC95288XV 288 6400 7.5 6 288 125 151 TQ100 TQ144 TQ144 CS144 PQ208 BG256 FG256* CS280* Introduction to CPLDs 26 XC9500 5V Family XC9536 XC9572 Macrocells 36 72 108 144 216 288 Usable Gates 800 1600 2400 3200 4800 6400 5 7.5 7.5 7.5 10 15 36 72 108 144 Max. User I/Os 34 72 108 133 Packages 44VQ 44PC 84PC 100TQ 100PQ 160PQ 100TQ 100PQ 160PQ tPD (ns) Registers 48CSP Introduction to CPLDs 27 44PC 84PC 100TQ 100PQ XC95108 XC95144 XC95216 216 166 160PQ 208HQ 352BG XC95288 288 192 208HQ 352BG XC9500 5V Family XC9536 XC9572 Macrocells 36 72 108 144 216 288 Usable Gates 800 1600 2400 3200 4800 6400 5 7.5 7.5 7.5 10 15 36 72 108 144 216 288 34 72 108 133 166 192 84PC 100TQ 100PQ 160PQ 100TQ 100PQ 160PQ 160PQ 208HQ 352BG 208HQ 352BG TPD (ns) Registers Max. User I/Os Packages 44VQ 44PC 48CS Introduction to CPLDs 28 44PC 84PC 100TQ 100PQ XC95108 XC95144 XC95216 XC95288 XC9500XL 3.3V Family XC9536XL XC9572XL XC95144XL XC95288XL Macrocells 36 72 144 288 Usable Gates 800 1600 3200 6400 tPD (ns) 5 5 5 6 Registers 36 72 144 288 Max. User I/Os 36 72 117 192 PC44 VQ44 CS48 VQ64 PC44 VQ44 CS48 VQ64 TQ100 Packages Introduction to CPLDs 29 TQ100 CS144 TQ144 TQ144 PQ208 BG256 FG256 CS280 XC9500XV 2.5V Family XC9536XV XC9572XV XC95144XV XC95288XV Macrocells 36 72 144 288 Usable Gates 800 1600 3200 6400 tPD (ns) 5 5 5 6 Registers 36 72 144 288 Max. User I/Os 36 72 117 192 PC44 VQ44 CS48 PC44 VQ44 CS48 TQ100 Packages Introduction to CPLDs 30 TQ100 CS144 TQ144 TQ144 PQ208 FG256 CS280 XC9500/XL/XV Family Features Driving the ISP Revolution • • • • • Complete support of ISP designer’s Product Life Cycle Provides industry’s best pin-locking CPLD at lowest price Complete “state-of-the-art” software support CPLDs key part of the Xilinx “total logic solution” Benefits of ISP: – No need for costly device programmers, fewer board re-spins, less scrap and re-work, reduces design and development time scales, enables field upgrades, eliminates unnecessary package handling, CPLD CPLD Introduction to CPLDs 31 x Program the whole board not each chip! XC9500/XL/XV Family Features Most Complete JTAG Testability • IEEE Std 1149.1 boundary-scan – Testability & advanced system debug/diagnosis – 8 instructions supported (incl. CLAMP) • Full support on all family members • 1532 Industry-standard ISP interface • Complete 3rd party support • Benefits of JTAG: Improved testability, higher system reliability, cheaper test equipment, shorter test time, reduced spare board inventories, reduces device handling. Introduction to CPLDs 32 XC9500/XL/XV Family Features Innovative CSP Packaging • New 48-pin Chip Scale Package (CSP) – 1/3 size VQFP-44, 82% smaller than PLCC-44 – Big board space benefits • New 144-pin CSP (117 user I/Os) • Uses standard IR surface mounting process • Supports industry’s high growth market segments – Communications, Computers, Consumer PC44 5.6X Introduction to CPLDs 33 XC9500/XL/XV Family Features New price points open up new apps • Motherboards for PCs and servers • PC peripherals and add-on cards – DVD players/controller cards – Graphics cards • Automotive – Engine control – Automotive navigation systems (GPS) • Consumer – LAN / DSLAM – Video Games/Toys Introduction to CPLDs 34 CPLD Software Improvements in 6.1 • Ease of use – Improved CPLD process flow • Single process (Implement Design) will pull the design through the entire fitting process • Granular control still possible for power users by expanding individual processes CoolRunner – New design creation aids XPLA3 Product Overview • New project wizard leads the user through the project creation process • Add existing source / Create new source processes - assist in getting started faster – Centralized process properties menu • Web Update – Built in utility checks for service packs and supplemental CPLD updates – Downloads and installs update in single step Introduction to CPLDs 35 File Number Here XCR3000XL Family Features Overview CPLD Designer Needs High Performance Time to Market Package offering Low power • • • • High fMAX = 200MHz Fast TPD = 5nS Instant productivity software tools Best ISP/JTAG support • World’s Smallest BGAs (CP56) • Industry’s 1st & most efficient architecture PLA • Ultra low power operation • No power/performance tradeoffs • Low Power = High Reliability THESE PARTS ARE FOR LOW POWER APPLICATIONS! Introduction to CPLDs 36 CoolRunner XPLA3 Family XCR3032XL XCR3064XL XCR3128XL XCR3256XL XCR3384XL XCR3512XL Macrocells 32 64 128 256 384 512 Usable Gates 800 1600 3200 6400 9600 12800 5 6 6 7.5 7.5 7.5 fSYS (MHz) 175 145 145 140 127 127 Packages VQ44 (36) VQ44 (36) (max user I/O) PC44 (36) PC44 (36) CS48 (36) CS48 (40) PQ208 (164) PQ208 (172) PQ208 (172) FT256 (164) FT256 (212) FT256 (212) FG234(220) FG234 (260) tPD (ns) CP56 (48) VQ100 (68) VQ100 (84) CS144 (108) TQ144 (108) TQ144 (120) CS280 (164) Introduction to CPLDs 37 XCR3000XL Family Features Low Power • Dynamic Battery Life – Populated with 16 bit counters @ 20MHz – 2 AA batteries – Non CoolRunner devices in low power mode 200 180 160 140 120 100 80 60 40 20 0 CY37128 M4A3 M4LV 7000A 3000A ISPLSI2128VE XC95144XL XCR3128XL Hours of operation 3.3V CPLD Low Power Leadership! Introduction to CPLDs 38 Competitive Device Families XCR3000XL Family Features Extra ‘Hidden’ Benefits of Low Power • Eliminates Expensive Heat Sinks & Cooling Fans – Heat Sinks: $ 0.50 - $ 12.00 – Fans: $ 3.50 and up • Decreases Power supply component size for: – High Performance – Small Portable Form Factors • Computing Lap & Palm Enclosures • Higher product density Less Heat = Higher Performance, Cost Savings & Reliability! Introduction to CPLDs 39 Thermal Emissions Comparison Ambient Xilinx XCR3256XL-7TC144 Cypress CY37256VP160-100AC Lattice M4LV-128/64-10YC Altera EPM7256AETC144-7 Altera EPM3256ATC144-7 25 30 35 40 45 50 Degrees Centigrade 55 60 Lattice ispLSI2192VE-100LT128 • Devices programmed with 16 bit counters with the MSB brought out to an LED and operated at 50MHz • Where applicable, competitive devices were in non-turbo mode • Note the MACH4 device is 128 macrocells, Lattice is 192 macrocells (largest in the family) Introduction to CPLDs 40 Thermal Characteristics Altera 3K Test IR00004.ISI The Altera MAX3000A 256 macrocell device was powered up in low power mode and loaded with a 16 bit counter and clocked at 50MHz. A thermal imaging camera measured the Altera device (P1) to be @ 40.23ºC, (P2) was a CoolRunner XCR3256XL device @ 30.03ºC, the back ground temperature was 22.88ºC (P3) Introduction to CPLDs 41 Higher System Reliability Infant Mortality Constant Failure FITS Wear out Temperature Time Activation Energy EA Aggravated by Temperature! Increased Temperature = Decreased Reliability Introduction to CPLDs 42 Lower Power = Smaller Packages 17.6 mm 44 PLCC 12 mm 7 mm 12 mm 48 CS 6 mm Introduction to CPLDs 43 7 mm 6 mm 56 CP 17.6 mm 44 VQ • XPLA3 supports small industry standard packages • New Chip Scale Packaging – CS48 – CP56 The RealDigital CPLD A New Class of CPLD with High Performance and Ultra Low Power without Compromise! CPLD Sense amp Designs Have Migration Limits 0.60µ 0.50µ 5.0 Volt Devices 3.3 Volt Devices 0.35µ High speed and low power barrier 2.5 Volt Devices 0.25µ CR-II FZP 1.8 Volt, 0.18µ Devices 0.18µ Sense amps don’t scale well Sense amp based CPLD technologies don’t scale effectively beyond 0.18µ Introduction to CPLDs 45 High Level Architecture Clock and Control Signals Function Block 1 MC1 MC2 I/O Function Block n 16 FB MC1 MC2 16 FB I/O I/O I/O MC16 16 Fast Inputs AIM PLA 16 40 I/O MC16 Fast Inputs I/O Blocks I/O Blocks 40 I/O Introduction to CPLDs 46 PLA 16 16 Function Block Architecture 40 From AIM MC 1 PLA Array 40x56 To I/O Block 16 56 Product Terms MC 16 3 Global Set/Reset Introduction to CPLDs 47 Feedback to AIM Global Clocks Logic Allocation Advantage PAL: Requires 4 product terms! A B Indicates ‘used’ junction Indicates ‘unused’ junction Indicates ‘fixed’ junction Introduction to CPLDs 48 A C Can NOT share common logic PLA: Requires only 3 product terms! X Y B X=A&B#C Y = A & B # !C C X Y Common logic may be shared in CoolRunner-II FB Inputs from AIM 40 Macrocell Architecture application notes: http://www.xilinx.com/apps/epld.htm PLA Array 49 P terms Macrocell 4 Control Terms from I/O Block (Fast Input) Feedback to AIM PTA PTB PTC PTA CTS GSR GND VCC GND S D/T to I/O Q FIF Latch DualEDGE CTC PTC Introduction to CPLDs 49 GCK0 GCK1 GCK2 PTC CE CK R PTA CTR GSR GND I/O Block Characteristics HSTL & SSTL VCCIO to AIM Input Hysteresis to Macrocell (Fast Input) VREF for Local Bank VREF I/O Pin 128 macrocell and larger devices 3.3V - 1.5V Input Slewrate from Macrocell Enabled Control Term PTB GTS[0:3] CGND Open Drain Disabled Introduction to CPLDs 50 VCCIO Weak Pullup/Bus Hold I/O Pin / 4 I/O Flexibility XC2C32 XC2C64 XC2C128 XC2C256 XC2C384 XC2C512 I/O Banks 1 1 2 2 4 4 LVTTL33, LVCMOS 18, 25, 33 & 15*I/O SSTL3-1(3.3v), SSTL2-1 (2.5v), HSTL1 (1.5v) Input hysteresis control Slew rate control CoolCLOCK DataGATE Clock doubler Clock divider Bus hold output Hot pluggable Note: 1.5v inputs need hysteresis Introduction to CPLDs 51 RealDigital Design Advantage Turbo vs Non Turbo Larger R = slower response Vcc & less power A B C Sense amplifier 0.25mA each - Standby Higher ICC at Fmax • Traditional CPLDs - bipolar sense amp product terms – Always consumes power – Even at standby – Performance is traded for power consumption as devices get larger Introduction to CPLDs 52 A B C D RealDigital: CMOS Everywhere - Zero Static Power • CoolRunner-II RealDigital design uses 100% CMOS for product terms – Virtually no standby current – Combines high performance & ultra low power – No power limits on device size Reducing Power • Icc = C x V x f • To reduce power: – Lower capacitance – Lower voltage – Lower frequency 0.18 m lowers capacitance Low VCC @ 1.8V How can we reduce the frequency? ~ 200mA Traditional Sense Amp Designs Icc ~ 100mA Note: 128 MC device estimate Introduction to CPLDs 53 Frequency ~ 200MHz Low Power CPLDs • CoolRunner XPLA3 – Low power – 3.3V core with 5V tolerance • CoolRunner II – – – – Ultra Low Power Lowest Cost Feature Rich 1.8V core with 1.5v to 3.3V compatibility And our parts still run on GRAPEFRUIT! Introduction to CPLDs 54 Beware! Not all ‘Low Power’ Logic is Created Equal! • Some logic devices have ‘power down’ modes – Complicates timing models (non-deterministic) – Power down modes slow timing (TPD / Fmax) when used • Some logic devices ‘shut down’ when not active – Latency periods apply for wakeup (typ. 50ns) – No power savings when operating • Choose Logic to simplify design process – No speed / power tradeoffs – Simple timing models Introduction to CPLDs 55 500mV Input Hysteresis • Supports simple oscillation schemes • Ideal for slow edge rate, noisy signals – – – – Analog comparators & sensors Hall effect switches IR inputs R/C oscillators V CoolRunner-II In • Eliminate external Schmitt trigger buffers • Reduces power consumption with slow signals Introduction to CPLDs 56 _ + CoolRunner-II Solving Signal Integrity Challenges • Noisy, slow analog signals – – – – Hall Sensor R/C Oscillator XTAL input RFI, EMI effects Input hysteresis • With input hysteresis – Analog signals function as digital inputs – Saves power by non-linear operation – Added noise immunity Introduction to CPLDs 57 DualEDGE: Performance Enhancing • • • • In all CoolRunner-II devices Edge detect doubles clock up to 500MHz Selectable on a per macrocell basis Ideal for Double Data Rate (DDR) memory devices Doubler Introduction to CPLDs 58 Clock Divider: Power Efficient Divider • 128, 256, 384 & 512 macrocell • 2,4,6,8,10,12,14 or 16 digital clock divide • Reduce external oscillators • 50% duty cycle • Reduces cross talk Divide by 4 System Clock Sync Reset Div_clock Phase bit = 0 Div_clock Phase bit = 1 Introduction to CPLDs 59 CoolCLOCK • Further power reduction plus performance – Combination of clock divider & DualEDGE (clock doubler) – Divide incoming clock by two (lowing total power), then double at macrocell for high speed requirements Global Macrocell Input Divide by 2 Doubler Divider Introduction to CPLDs 60 CPLD Original frequency Output DataGATE • Another low power enhancement – Control DataGATE signal externally or internally – User programmable on/off switch for specific inputs • Only enable inputs when necessary • Great for power reduction on wide logic interfaces – Latch data when valid, reduces unnecessary signal toggling DataGATE Diagram DataGATE control signal Input pin Introduction to CPLDs 61 Gated internal signal The Best Design Security Easy To Use New Capabilities 1532 in system programming 1149.1 JTAG boundary scan Fast Programming times Multiple levels of security Affect different mechanisms Interconnects are buried Multiple security signals Scattered and layered Xilinx WebPACK™or Foundation ISE Software Introduction to CPLDs 62 RealDigital CPLD Advantage RealDigital Features 0.18m design with 100% digital core Advanced I/O’s Superior clock management Enhanced security Advanced packaging Single world class software environment Introduction to CPLDs 63 Customer Benefits High performance up to 385MHz, TPD = 3.0ns (32mc) Ultra low power, 16mA typ. standby with no price premium 500mV input hysteresis for improved noise immunity LVTTL, LVCMOS, SSTL, HSTL (1.5v to 3.3v capable) DataGATE for lower power consumption I/O banking for voltage integration (up to 4 banks) DualEDGE increased performance > 500MHz toggle rate Reduced power consumption Clock divide & CoolCLOCK Multiple levels of security for ultimate design protection Smallest footprint chip scale High performance BGA with higher I/O per macrocell Lowest cost quad flat pack One software system for all Xilinx products - ISE Free web download or CD - WebPACK Design fit optimizing - WebFITTER Power estimator - XPower Chip Scale Packaging Leadership 17.6 mm 44 PLCC 12 mm Uses standard IR techniques for mounting to PC board Introduction to CPLDs 64 6 mm Supports high-growth market segments: Communications, Computers, Consumer, especially wireless 6 mm 8 mm 56 CP 12 mm 132 CP 17.6 mm 44 VQFP 8 mm Lower Power = Smaller Packages • 56-Ball 0.5mm CSP • Provides 44 I/O’s – 0.5mm pitch • 36 mm2 footprint • Ideal for handheld & portable applications – – – – PDAs Portable PCs Cellular Phones Telecom & Networking Equipment – Network Appliances Introduction to CPLDs 65 Best Package Offering for High Volume Applications Smallest form factor chip scale packages CP56 (6 x 6mm) CP132 (8 x 8mm) Optimized packaging • Smallest size chip scale • Highest performance BGA • Highest I/O count • Small size VQ44 (10 x 10mm) VQ100 (14 x 14mm) • Lowest cost flat pack FT256 (17 x 17mm) PC44 (16.5 x 16.5mm) TQ144 (20 x 20mm) Small form factor, highest performance, BGA packages FG324 (23 x 23mm) PQ208 (28 x 28mm) Package widths drawn to scale. Introduction to CPLDs 66 CoolRunner-II Family Overview Features XC2C32 XC2C64 XC2C128 XC2C256 XC2C384 XC2C512 Macrocells 32 64 128 256 384 512 FToggle (MHz) 500 454 416 416 416 416 FSYSTEM (MHz) 385 270 263 238 217 217 Max I/O 33 64 100 184 240 270 I/O Banks 1 1 2 2 4 4 LVCMOS, LVTTL 1.5, 1.8, 2.5, 3.3 Yes Yes Yes Yes Yes Yes HSTL, SSTL No No Yes Yes Yes Yes DualEDGE Yes Yes Yes Yes Yes Yes DataGATE, CoolCLOCK No No Yes Yes Yes Yes Standby Power (uW) 28.8 30.6 34.2 37.8 41.4 45.0 Multiple Levels of Security Yes Yes Yes Yes Yes Yes Packages (size, type) VQ44 (10 x 10mm, leaded) PC44 (16.5 x 16.5mm, leaded) CP56 (6 x 6mm, chip scale) VQ100 (14 x 14mm, leaded) CP132 (8 x 8mm, chip scale) TQ144 (20 x 20mm, leaded) PQ208 (28 x 28mm, leaded) FT256 (17 x 17mm, BGA) FG324 (23 x 23mm, BGA) Introduction to CPLDs 67 Maxium User I/O 33 33 33 33 33 45 64 80 100 100 80 106 118 173 184 118 173 212 240 173 212 270 PDA: CoolRunner Reference Design Example Flash SRAM Battery Battery Compact Flash SMBus mP Microprocessor LCD LCD SPI Keypad Indicates a CoolCORE Introduction to CPLDs 68 Touch Screen IrDA LED LED UART Docking Docking Cradle Cradle Exploiting Our Technology Lead Feature Size (micron) 0.35 0.25 CPLDs 0.18 Clipper 0.13 FPGAs Schooner 0.09 0.07 2000 Introduction to CPLDs 69 2001 2002 2003 2004 2005 XCR3000XL & XC2C Low Power Features Open Up New Applications Portable / Consumer PDAs Cell phones MP3 players Laptops Docking stations Battery powered scanners PDA add-on modules Digital cameras Portable dictation systems Gas meters Handheld meters Smart Card Readers Payphones Medical Portable syringe pump Home monitoring system Blood analyzer Introduction to CPLDs 70 Telecom “Neighborhood” Multiplexors Bay Stations Routers Multiplexors PBXs WLAN Central office switches Speech recognition systems PC Peripheral PCMCIA cards Portable computer displays White board scanners Memory cards High Performance Workstations and servers Video graphics cards Storage Systems One Ultimate CPLD Solution for All Designs High Performance 3.0ns TPD, FMAX 385Mhz Improved features Storage Systems, Routers Introduction to CPLDs 71 Low Cost 0.18µ = small die size Lowest cost packaging Lowest Power 9.9mW 16µA typical stand-by Set-Top Box, Cell phone Handheld, Portable Equipment IQ CPLDs for Industrial and Automotive Applications Introducing IQTM Products • Why IQ? – New range of devices with an extended Industrial Temperature option – Consists of CPLD and FPGA families already available in I Grade - and the addition of selected devices with an extended temperature ‘Q’ grade option – IQ - it’s the intelligent choice for Automotive designers!! • For FPGAs Q grade means: – -40°C to +125°C Junction Temperature • For CPLDs Q Grade means: – -40°C to +125°C Ambient Temperature Ambient = the temperature of the air surrounding the device Junction = is the temperature of the die in the package Introduction to CPLDs 73 Industrial and Automotive CPLDs 512mc • Low power 2.5V • 5V tolerant • Small packaging 288mc • Lowest cost 3.3V • 5V tolerant • Small packaging • 3.3V tolerant • Small packaging • Up to 4 I/O banks 3.3V 2.5V Introduction to CPLDs 74 Core Voltage • • • • • • • • • Lowest power Highest speed Advanced features Additional security Smallest packages Lowest cost 3.3V tolerant 1.5V compatible Up to 4 I/O banks 1.8V CPLD Software Improvements in 6.1 • Ease of use – Improved CPLD process flow • Single process (Implement Design) will pull the design through the entire fitting process • Granular control still possible for power users by expanding individual processes CPLD Software – New design creation aids Update and Online Support • New project wizard leads the user through the project creation process • Add existing source / Create new source processes - assist in getting started faster – Centralized process properties menu • Web Update – Built in utility checks for service packs and supplemental CPLD updates – Downloads and installs update in single step Introduction to CPLDs 75 File Number Here Xilinx Online Software Solutions • Web-deliverable desktop and online design solutions for new, high volume markets • Industry’s broadest PLD product offering in a single downloadable solution • Enables fastest time-to-market – Easy to use design tools – Easy to obtain via the web – No license required • Software upgrades available for online purchase Introduction to CPLDs 76 ISE 6.1i Software Improvements Ease of Use • Improved CPLD process flow – Single process (Implement Design) will pull the design through the entire fitting process – Detailed control still possible for power users by expanding individual processes • New design creation aids – New project wizard leads the user through the project creation process – Add existing source / create new source processes - assist in getting started faster • Centralized process properties menu Introduction to CPLDs 77 ISE 6.1i Software Improvements • Web updates – Built in utility checks for service packs and supplemental CPLD updates – Downloads and installs update in single step Introduction to CPLDs 78 ISE 6.1i Software Improvements • HTML report improvements – Integrated browser in the project navigator environment – Addition of the timing report to HTML format – Improved graphical presentation and equation representation • CPLD support in PACE Pin Assignment and Constraint Editor Introduction to CPLDs 79 What’s New in ISE 6.1i • CoolRunner-II – Supported in XPower • Saturn support – All devices in all ISE configurations – Supported in XPower • ISE WebPACK availability – Web release on Sept 22 – Free CDs available from the Xilinx Online Store • Shipping charges apply – 3,400 downloads per month and growing! Introduction to CPLDs 80 Buy Products Online • Links to the Xilinx eCommerce page From WebFITTER From WebPACK Introduction to CPLDs 81 Additional Web Based Information • For additional CoolRunner-II product information http://www.xilinx.com/products/coolrunner2 • For other Xilinx CPLD related product information http://www.xilinx.com/products/cpldsolutions • For CoolRunner-II resource CD http://www.xilinx.com/forms/coolrunner_literature Introduction to CPLDs 82 CPLD Software Improvements in 6.1 • Ease of use – Improved CPLD process flow • Single process (Implement Design) will pull the design through the entire fitting process • Granular control still possible for power users by expanding individual processes Customer – New design creation aids Success Stories • New project wizard leads the user through the project creation process • Add existing source / Create new source processes - assist in getting started faster – Centralized process properties menu • Web Update – Built in utility checks for service packs and supplemental CPLD updates – Downloads and installs update in single step Introduction to CPLDs 83 File Number Here CPLD Success Stories Customer 1 Design Win Factors High Performance Market: Time to Market Application: Digital Audio Broadcast Car Fit in Existing Flow Package offering Automotive Radio 5v & 3.3v Device: Low cost Competition: Lattice Low power Reasons: XC9572XL-10TQ100I Pin Locking Pricing Easy to use software Introduction to CPLDs 84 CPLD Success Stories Customer 2 Design Win Factors High Performance Market: Time to Market Application: Switching Host Board Fit in Existing Flow Datacom Processor Package offering 5v & 3.3v Devices: XC95144XL-10TQ100C Low cost Competition: ASIC Low power Reasons: High performance Pin-locking Flexible interface I/Os Introduction to CPLDs 85 CPLD Success Stories Customer 3 Design Win Factors High Performance Time to Market Fit in Existing Flow Market: Consumer Application: MP3 Player Package offering Device: 5v & 3.3v Competition: None, no one could Low cost Low power XCR3032A-VQ44C meet low power Reasons: Low power Low Cost, small package Web-based software Introduction to CPLDs 86 CPLD Success Stories Customer 4 Design Win Factors High Performance Market: Time to Market Application: Fingerprint Point-of-Sale Fit in Existing Flow Package offering Consumer Terminal 5v & 3.3v Device: XC95216 Low cost Competition: None Low power Reasons: On-the-fly changes 133 MHz performance Pin-locking Superior technical support Introduction to CPLDs 87 CPLD Success Stories Customer 5 Design Win Factors High Performance Market: Commercial Time to Market Application: Hand-held Cable TV Fit in Existing Flow Package offering Tester 5v & 3.3v Device: XC95288XL Low cost Competition: Quicklogic Low power Reasons: Design Flexibility Price Performance Introduction to CPLDs 88 CPLD Success Stories Customer 6 Design Win Factors High Performance Time to Market Market: Application: Voice Synthesis Fit in Existing Flow Server Module Package offering 5v & 3.3v Low cost Low power Device: XCR3128 Competition: Lattice Reasons: Introduction to CPLDs 89 Telecom Power! CPLD Success Stories Customer 7 Design Win Factors High Performance Time to Market Market: Application: Microcontroller Fit in Existing Flow Package offering 5v & 3.3v Low cost Low power Instrumentation Emulator Device: XCR3128VQ100C Competition: Altera Reasons: Power Performance ISP Capabilities Introduction to CPLDs 90 5V Motor Control Test Equipment Security Systems Cable Modems Car Nav. Systems Cash Registers Surveillance cameras Set Top Boxes Access Controls Fax Machines Gaming Machines Industrial Control 3.3V Tape Drives Power Supplies Modems Access Controls Fax Machines Gaming Machines Industrial Control DAB Car Radios TFT LCD Interface Radio Comms Train Controller Slot Machine Digital Printer 2.5V Telecomm Base Stations Encoders Decoders DECT Phones Line Cards Industrial Control LOW POWER 3.3V Remote Controls Digital Cameras PDAs Smart Phones Test Equipment Web Pads Medical Equipment Label Printers Mobile phone add-ons MP3 Players Web pads Payphones Smart Card Readers Hand Held Games USB Applications Utility Meters Data Logger LOW POWER 1.8V Portable PDAs Remote Controls Test Equipment Medical Consumer Cell Phones MP3 Players Set Top Box Hand Held Games High Speed Telecom Switches Routers XC9500 • 5v, 36-288 macrocells • Low Cost • 5ns / 200MHz • Best Pin Locking • JTAG • High Endurance (10,000 program cycles) Introduction to CPLDs 91 • 3.3v, 36-288 macrocells • Low Cost • Best Pin Locking • JTAG • High Performance • High Endurance • 5ns / 200MHz • 2.5v, 36 - 288 macrocells • Low Cost • Best Pin Locking • JTAG • High Performance • High Endurance • 20 year data retention • 4ns / 250 MHz • 3.3v, 32-512 macrocells • Low Power • JTAG • Logic Flexibility • 5ns / 200MHz • Static power <100uA • 20 year data retention • 5V tolerant I/Os • 1.8v, 32-512 macrocells • Ultra Low Power • Schmitt Trigger Inputs • CoolCLOCK, DataGate • 3.5ns / 303MHz • Static power <100uA • I/Os - LVTTL, LVCMOS SSTL & HSTL Xilinx CPLD Summary • XC9500/XL/XV fast, higher voltage, low-cost – For mainstream 5v, 3.3v & 2.5v designs – Great architectural features (ISP, JTAG, pin-locking) • Coolrunner XPLA3 low power Pioneering low power 3.3v product with 5v tolerant I/O – Lowest power 3.3v CPLD - 3x better than nearest 3.3v competitor – • CoolRunner-II High Performance and Low Power Higher Performance & High Speed (385MHz) at 1.8V – Enhanced clocking & I/O feature set – Lowest power consumption • DataGATE for even lower power operation – Higher system reliability & system security – Introduction to CPLDs 92