EEE515_using_LPM_memories_in_your_VHDL

advertisement

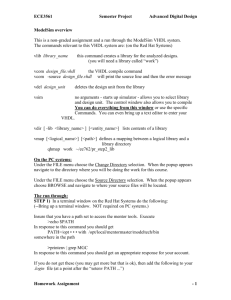

Using LPM Megafunctions in your own VHDL Ian McCrum • The Megafunctions wizard in Altera gives you a powerful and easy way to build custom parts • It creates a .vhdl file but also a .cmp file and a _inst.vhdl file – The .cmp file is the VHDL you insert to declare a component – The optional _inst.vhdl file is a template to instantiate the component – it lists the port names in a convenient way – The VHDL file is a simple wrapper that feed the appropriate values from the wizard to the altera libsray part • There are several ways to use these. • If you are a beginning VHDL modeller (programmer) then the first is the easiest • If you are an experienced VHDL programmer – familiar with packages and all the VHDL constructs then method 2 is handy. Example Design If a ROM contains contents and these are latched through a register a counter can be designed. Assume the ROM contents are such that address 0 contains 1, address 1 contains 2 address 2 contains 3, …. address 31 contains 1, Thus on power up the Q output is 0000 and the ROM has address inputs sitting at 0000. The ROM contents of 00001 are sitting at the D-type inputs but are not latched into the D-types until the clock. After the clock the output is now 00001 and the next ROM location is addressed. To use the megafunction wizard Start the Megafunction option under the tools menu or the BDF designer (below) Start a project, e.g called v_lpm. Use a foldercalled v_lpm. All relevant files end up here. Create a bdf file and select the insert component menu item Select the Megawizard Plug-in Manager at the bottom Make sure you give a sensible filename – in the correct folder pick VHDL as the output file Pick the correct part Fill in the next few screens Sensibly (read them and think!) Memory contents A .mif file is a simple text file, you can create this within Quartus by using the “NEW” menu item under the File menu. Or use a text editor and place the file in the project folder and specify it in the window on the left A mif file can have 2 types of comments. Single line comments begin with a ; or multiline comments by % delimiting symbols. The radix can be unsigned decimal, binary or hex. You must specify the DEPTH (number of addresses) and WIDTH (in bits.) Don’t use … At the end of the wizard… You can tick the _inst.vhd if you like, but make sure you have the .cmp file. You can actually delete, or not save, the bdf file, we used it to give us access to the wizard, it has created the .vhd and .cmp files for us Now: create a top level VHDL file and set as the top level entity Type in the following : (and think about what it means) The contents Of the .cmp file This is an instance of our LPM part You could insert the _inst.vhd here Here is the actual commented file spread over a couple of pages The megawizard actually created the file below Gives access to a package of altera parameterizable parts This is the text the wizard produces – it sets various generic data that is passed to the library part. The body of the .vhd file – This instantiates a altsyncram part and gets it to behave like a ROM. The code just passes data to the component. If you have sufficient data about the LPM parts you can directly instantiate them into your code. Provided you include the library and uses clauses of altera_mf you can avoid the two step way of doing things Second example of a MEGAfunction - created with the wizard – direct from the tools menu This is a suitable replacement for part of the datamemory module. The CYCLONE III ep3C16488 allows use of 56 M9K memory blocks. Each block can be 9kbits and allows widths of 32. We create a datamemory of 4096 locations each of 32 bits width. This uses 16 M9K blocks – less than a quarter of the available resource. We can create a register file and a instruction memory as well. The datamemory is a a one port RAM cell and does not need output clocking. The input clocking may be a nuisance and we may need to generate and gate the clock in out logic. Look and think about the circled items on the next few slides. Some screenshots of the MEGAWizard