SiliconAid Solutions, Inc. Confidential

advertisement

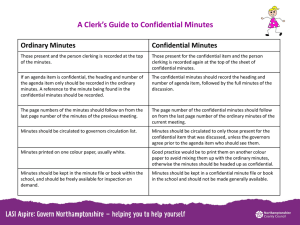

SAJE SiliconAid JTAG Environment Overview – Very Short SiliconAid Solutions, Inc. Confidential SAJE JTAG Product Summary Synthesis Verification Debugger JTS JTV JTD Generate P1687 JTAG Designs Verify BSDL and JTAG Design Provide JTAG Debug environment SiliconAid Solutions, Inc. Confidential P1687 Activities • • • • • YES – P1687 Exists and works SiAid is making significant investment Alpha software demos available Beta Software in development Partnering with key companies SiliconAid Solutions, Inc. Confidential P1687 Simplified Basic Flow Wrap IP Wrap Existing IPs with 1500 wrapper P1687 Synthesis Automatically integrate wrapped IP, and enhance for P1687 insert JTAG with P1687 compliant structures Pattern Conversion Convert Wrapped IP vectors into Chip Generate Testbench Verify JTAG and generate testbench to Simulate SiliconAid Solutions, Inc. Confidential level JTAG patterns sim all test including IP patterns The BIG PICTURE Insert JTAG and 1687 Logic JTS Generate Simulation and Chip Vectors Exhaustive semantic and compliance JTV checking Simulate CHIP (JTD) Verify JTAG and generate Leverages Design data testbench to sim all test to drive and debug including IP patterns JTAG hardware SiliconAid Solutions, Inc. Confidential Subset of Patterns for Board level support (SVF) BOARD Matches Vectors by Vector: Simulation, CHIP, and BOARD Board SVF Debug Flow Board Test Board Test Fails Generate Patterns Debugger SiliconAid Solutions, Inc. Confidential Verify JTAG and generate testbench to sim all test including IP patterns Simulate JTV - Typical ATE Flow Company A BSDL J T V • No Verilog Netlist • No Simulation Your Specific Guidelines SiliconAid Solutions, Inc. Confidential STIL Vector file 1687 Network GUI Serial ATPG SiliconAid Solutions, Inc. Confidential 1687 Board SVF Debug Flow Board Test Board Test Fails 1687 ATPG Board or ATE Debugger SiliconAid Solutions, Inc. Confidential Understands 1687 network and BSDL, Generates selected tests, SVF output Interactive debugger – leverages design info into ATE and Board tests SiliconAid Solutions JTAG DEBUGGER TOOL (JTD) SiliconAid Solutions, Inc. Confidential WHY JTD • New Product Introduction/Evaluation • Proto-typing pre-Silicon on Xilinx Boards • Works in concert with ATE testers • Debug capabilities to identify internal registers failing on TDO • Tracks JTAG state machine on vector per vector basis • Fast, easy, quick way to drive and observe standard JTAG signals • Leverages JTV output to enhance debugging capability SiliconAid Solutions, Inc. Confidential JTD Major Features • Hardware Interface using USB 2.0 • JTAG 5 pin connector • Can drive evaluation board, Apps board, burn in board, ATE tester board, and more….. • Compares expected values for TD0 • Supports run till FAIL, STEP, etc.. • Leverages patterns from JTV • Supports external SVF patterns SiliconAid Solutions, Inc. Confidential Initial JTD Window Debugger run JTAG State and controls Machine Viewer Online Help and patterns Displays Fails Displays expected apps notes on actual register and actual data in waveforms SiliconAid Solutions, Inc. Confidential Debugger Window Flow Control Header Info Fails Results Window log Window SiliconAid Solutions, Inc. Confidential Command line Register Viewer Failing bits are graphically displayed and bit descriptions pop up when clicked. Black – Expect 1 White – Expect 0 Red - Failed SiliconAid Solutions, Inc. Confidential Waveform Viewer Capturing internal registers not accessible via pins on the device. SiliconAid Solutions, Inc. Confidential JTAG State Machine Status Status is graphically displayed real time as the vectors are steps in the debugger window SiliconAid Solutions, Inc. Confidential DEMO JTD USB 2.0 JTAG Signals TMS TDI TDO TCK TRST SiliconAid Solutions, Inc. Confidential Apps Board What is JTV ? SiliconAid Solutions, Inc. Confidential SiliconAid Solutions JTAG VERIFICATION TOOL (JTV) SiliconAid Solutions, Inc. Confidential JTV - Purpose • Verification support for JTAG providers – Focus is chip-level verification • Provide an efficient means to – – – – Insure correct JTAG functionality on first-pass silicon Deliver a verified BSDL file for customer usage Deliver high quality production test vectors Diagnose fab-related pad or JTAG logic yield problems • Goal is to – Eliminate customer BSDL and/or JTAG-related problems SiliconAid Solutions, Inc. Confidential JTV Design Flow Diagram SiliconAid Solutions, Inc. Confidential SAJE JTV simplified Flow JTAG Generation BSDL •Legacy Designs •Any 3rd Party tool •Internally developed SAJE JTV •Independent verification that BSDL matches your Design •Verifies Design is IEEE 1149.1 & 1149.6 compliant •Generates full suite of Production test vectors •Generates verilog testbench & tests for verification •Proven technology on hundreds of production designs •More than 12 years + of success Production Ready Patterns User selectable test Testbench Netlist with JTAG Any 3rd Party Simulator SiliconAid Solutions, Inc. Confidential Board Companies Specific Benefits • • • • • Screen for incoming BSDL Chip level ATE pattern Board Level targeted patterns for a chip No Verilog required Standardized test bench for all incoming design (if chip provider supplies verilog) SiliconAid Solutions, Inc. Confidential Incoming BSDL and Verilog Process Flow Company A Company B Company C J T V Company X Checker Company D Company X Specific Guidelines SiliconAid Solutions, Inc. Confidential Release to Production JTV - Typical ATE Flow Company A BSDL J T V • No Verilog Netlist • No Simulation Company X Specific Guidelines SiliconAid Solutions, Inc. Confidential STIL Vector file Summary • Simulation, ATE, and Board can have same patterns applied – Helps solve the NPF problems! • Alpha 1687 Flow available • JTD - Debugger works at chip level and plans to support board level in the future • JTV is a mature product with 15+ years of continual history and usage • 1149.1 and 1149.6 Chip verification and compliance checking • Verifies BSDL matches design • SVF Patterns will soon be portable to board test • Tools be used in a custom or JTAG synthesis design flow • Leverages Design data in ATE and Board Debug SiliconAid Solutions, Inc. Confidential Jim Johnson : President email: jim.johnson@siliconaid.com phone: (512) 694-4261 SiliconAid Solutions, Inc. Confidential SiliconAid Solutions, Inc. Confidential