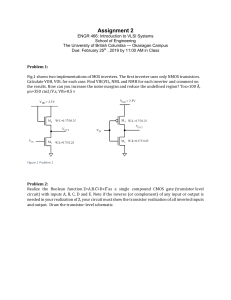

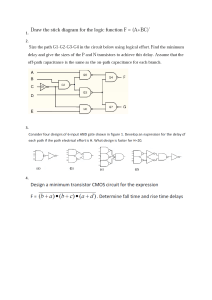

Assignment 2 B Tech (E.C.) Semester- IV CMOS VLSI Design (EC-403) Q.1 Select most appropriate option (1 to 5). 1. In the case of simultaneous switching, compared to NOR2 gate, NOR3 gate (a) is slower and having a higher VIL. (b) is faster and having a lower VIL. (c) is slower and having a higher VIH. (d) is faster and having a lower VIH. (e) none of above 2. The threshold voltage for each transistor for given figure is 2V. For this circuit to work as an inverter, Vi must take the values (A) -5 V and 0 V (B) -5 V and 5 V (C) -0 V and 3 V (D) 3 V and 5 V 3. In the CMOS inverter circuit shown, if the transconductance parameters of the NMOS and PMOS transistors are K’n=K’p= 40 µA/V2, and their threshold voltages are VTn= VTp= 1V, the current I is (A) 0 A (B) 25 µA (C) 45 µA (D) 90 µA 4. In the CMOS circuit shown, electron and hole mobilities are equal, and M1 and M2 are equally sized. The device M1 is in the linear region if (A) Vin < 1.875 V (B) 1.875 V < Vin < 3.125 V (C) Vin > 3.125 V (D) 0 < Vin < 5 V 5. Consider the following statements in connection with the CMOS inverter in figure where both the MOSFETs are of enhancement type and both have a threshold voltage of 2V Statement 1: T1 conducts when Vi 2V. Statement 2 : T1 is always in saturation when V0=0V. Which of the following is correct? (A) Only statement 1 is TRUE (B) Only statement 2 is TRUE (C) Both the statements are TRUE (D) Both the statements are FALSE 6. 30/01/2025 Q.2. In the CMOS inverter circuit shown in following figure, the input Vi makes a transition from VOL= 0V to VOH=5V. Determine the high-to-low propagation delay time tpHL when it is driving a capacitive load CL of 20 pF. Device data: nMOS: VTN=1V;Bn= 40 µA/V2, λ=0; pMOS: VTp=1-V;Bp= 20 µA/V2, λ=0; Q.3 Find out operating region at each point(A,B,C,D,E) in DC characteristic of NOT gate. Q.4. A typical CMOS inverter has the voltage transfer characteristics(VTC) curve as shown in the figure. Evaluate the value of the inverter threshold VINV (Switching Voltage VM), which is the value of the input at which Vo falls by