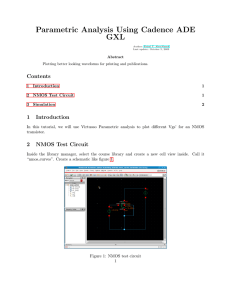

Exp No.1 18.12.2023 CHARACTERISTICS OF NMOS AND PMOS TRANSISTORS USING CADENCE VIRTUOSO TOOL AIM: To design bias circuit for both NMOS and PMOS transistors and analyse the drain characteristics and transfer characteristics using Cadence Virtuoso EDA Tool. SOFTWARE USED: Cadence Virtuoso 6.1.8 for design and ADE L tool for analysis. PROCEDURE: Transfer Characteristics: ▪ Begin by setting the Gate-Source Voltage (VGS) to a constant value of 1.8V. ▪ Next, designate the Drain-Source Voltage (VDS) as a variable, naming it 'VDS'. ▪ After making these adjustments, click the 'check' button to confirm your settings and then save them. ▪ Now, access ADE L by navigating to the 'launch' option and selecting 'ADE L' to open the ADE L tab. ▪ In the ADE L tab, choose 'analysis' and configure it for 'dc analysis'. ▪ Specify the components you want to include in the sweep, and set the sweep parameters as follows: start at 0V and end at 1.8V. ▪ To plot the drain current, go to 'Outputs' in the ADE L tab and select 'Outputs to be plotted', then choose 'drain'. ▪ Copy the necessary variables by going to 'variables', selecting 'copy from cell view', and then navigating to 'Tools' to initiate a 'parametric analysis'. ▪ Define the limits or range for the variable VDS. ▪ Finally, run the analysis to generate the waveform. Drain Characteristics: ▪ Initiate the configuration by setting the Drain-Source Voltage (VDS) to a constant 1.8V. ▪ Make the Gate-Source Voltage (VGS) a variable, labeling it as 'VGS'. ▪ After configuring, validate your settings by clicking the 'check' button and saving the configuration. ▪ Access the ADE L tab by going to 'launch' and selecting 'ADE L'. ▪ In the ADE L tab, choose 'analysis' and set it to 'dc analysis'. ▪ Customize the sweep parameters by selecting the components for the sweep and defining the parameters: starting at 0V and ending at 1.8V. ▪ To plot the drain current, navigate to 'Outputs' in the ADE L tab, then 'Outputs to be plotted', and choose 'drain'. ▪ Copy the necessary variables from the cell view by going to 'variables', selecting 'copy from cell view', and then access 'Tools' to initiate a 'parametric analysis'. ▪ Establish the limits or range for the variable VGS. ▪ Execute the analysis to generate the waveform. SIMULATION RESULTS: Bias circuit for NMOS transistor. Transfer characteristics of NMOS transistor. Drain characteristics of NMOS transistor. Bias circuit for PMOS transistor. Transfer characteristics of PMOS transistor. Drain characteristics of PMOS transistor. RESULT: Bias circuits were designed for both NMOS and PMOS transistors, followed by a thorough analysis of their drain and transfer characteristics employing the Cadence Virtuoso Electronic Design Automation (EDA) Tool.