Addressing memory on Intel 8086

advertisement

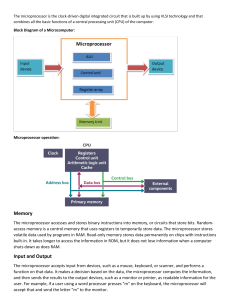

1. Addressing memory on Intel 8086. - Address bus: 20 bits, which mean the hardware is limited to 220 𝑏𝑖𝑡𝑠 = 1𝑀𝐵 - Register size is 16 bits - Effective address and segmentation of memory. 2. Memory segmentation. - A segment is just an area in memory. - The total memory (RAM) is divided into segments of various sizes. - The process of dividing memory into different segments is called segmentation: Code, data, stack, extra. - These registers are 16-bit in size. - Each register stores the base address (starting address) of the corresponding segment. 3. Effective address. - The 20-bit address of byte is called its effective address (physical address) - It is specified as a logical address. - Logical address is in the form of: Base: Offset. - 8086 uses 2 registers to form the effective 20-bit address. - One of these registers is one of segment register (CS, DS, SS, ES) and the other is called the offset register. 4. Architectural model of 8086. - Instructions are stored in RAM & must be fetched. - Then decoded into micro instructions. - Then executed using ALU. - Results are written either to register or to RAM. - The 8086 CPU is divided into two independent functional parts: the bus interface unit (BIU) and the execution unit (EU). - Bus Interface Unit. BIU fetches instruction codes. It stores fetched instruction codes in a FIFO register called QUEUE. It handles transfer of data and addresses between the processor and memory/IO on the buses. It reads data from memory and I/O devices. It writes data to memory and I/O devices. It computes and sends out addresses. BIU contains: Segment register (CS, DS, SS, ES) – A segment points to the starting address of a memory segment (Ex: the code segment register points to the starting address of the code segment). The maximum capacity of a segment may be up to 64KB. Instruction pointer: points to the address (offset) of the next instruction to be executed. Its content is automatically incremented when the execution of a program proceeds further. The contents of the IP and code segment register are used to compute the memory address of the instruction code to be fetched. This is done during the fetch cycle. 6-byte instruction queue. - Execution Unit (EU) The execution unit is responsible for decoding and executing all the instructions. It receives opcode of an instruction from the QUEUE. It decodes it and then executes it. It tells BIU where to fetch the instructions or data from. It has 16-bit ALU, which can perform arithmetic and logical operations on 8-bit as well as 16-bit data. Execution unit contains: general purpose registers, stack pointer, base pointer, index registers, ALU, flag register, instruction decoder, timing & control unit.