Gate-coupled field-effect transistor pair amplifier

advertisement

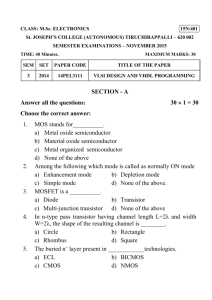

United States Patent [191 [11] [45] Swanson [54] GATE-COUPLED FIELD-EFFECT TRANSISTOR PAIR AMPLIFIER [75] Inventor: [73] Assignee: Patent Number: Date of Patent: 4,518,926 May 21, 1985 Attorney, Agent, or Firm—-Volker R. Ulbrich [57] ABSTRACT Enc J’ Swanson’ Readmg’ Pa’ AT&T Bell Laboratories, Murray An enhancement mode (104, 204, 404) and a depletion mode (102, 202, 402) pair of N-channel MOS transistors [21] Hill, N-JAppl' NO’: 451,025 have their drain-source conduction paths connected in series and provided with a bias current means (120, 220, 122] Filed: together as an input node. In one embodiment (100) [51] [52] Int (13 I _________________ __ H031? 3/16; H031: 3/45 US. Cl. .................................. .. 330/253; 330/277; 330/288 Field of Search ............. .. 330/253, 257, 269, 277, 306, 410). The gates (106, 206, 308, 310) are coupled [58] Dec- 20’ 1982 their bulk regions are source-connected and the output (118) is from the source of the enhancement mode de vice (104) to obtain a source follower con?guration ampli?er. In a second embodiment (200), the output 330/288; 323/315, 316; 307/448, 450, 571, 574, (218) is taken from the drain (208) of the depletion mode 581 device (202) to obtain a common source con?guration [56] References Cited ampli?er. Two source follower pairs (302, 304) are US. PATENT DOCUMENTS input voltage ampli?er stage (300). A common source pair (402, 404) is disclosed in combination with an addi disclosed connected in parallel to form a differential 3.509.375 4/1970 Gormley ........................... .. 307/581 4.042.839 8/1977 Araki 4.069.431 l/l978 Kucharewslu 4.443,7l5 4/1984 ......... . . . . .. 330/269 X 330/253 X Fox ............................... .. 307/581 X Primary Examine/'—James B. Mullins tional enhancement mode transistor (406) to form a current mirror (400). 6 Claims, 4 Drawing Figures 8310 O-IN US. Patent May21,1985 Sheet} of2 . * 20s “12m 204 4,518,926 1 4,518,926 2 FIG. 4 is a schematic circuit diagram of a current GATE-COUPLED FIELD-EFFECT TRANSISTOR PAIR AMPLIFIER BACKGROUND OF THE INVENTION The invention relates generally to electronic ampli? mirror circuit in accordance with a fourth example of the invention. DETAILED DESCRIPTION In the discussion of the Figures below, it is assumed particularly to those using MOSFET (metal oxide sili that all the transistors are N-channel MOS ?eld-effect devices. Input or output voltage of a circuit from an appropriate node is with respect to some reference volt con ?eld effect transistors). age, such as ground potential. ers which use ?eld-effect transistors, and relates more Individual MOSFET devices can be connected as ampli?ers in various known ways e.g. common source, common gate, common drain, source follower, etc. to provide different characteristics of operation as desired EXAMPLE OF FIG. 1 The FIG. 1 shows a source follower ampli?er 100 in accordance with one embodiment of the invention to suit a particular purpose. Two such devices can also 15 which includes a pair of dimensionally similar MOS be connected together to provide a variety of possible input and output characteristics which are not obtain able with just one device. One example of this in the commonly used “casc0de" con?guration, in which a ?rst-stage device is connected in a common-source con?guration, with its output going to the input of a second device connected in a common-gate con?gura tion. The resulting structure is an ampli?er having a high input impedance, low noise, and a high gain. transistors 102, 104 having their gates connected to gether as a signal input node 106. The ?rst, upper tran sistor 102 of the pair 102, 104 is a depletion mode device which has its drain 108 connected to a positive power supply voltage source VDD. The source 110 of the de pletion mode transistor 102 is connected to the drain 112 of the second, lower transistor 104, which is an enhancement mode device 104, at a common node 114. The source 116 of the enhancement mode transistor 104 When a pair of MOSFET devices is connected to 25 is an output signal node 118 of the ampli?er 100 and is provide ampli?cation, the gate of one of the devices must generally be provided with a bias voltage in order that the drain-to-source voltage of the other device will connected in series with a bias current source means 120. The bulk regions of both the transistors 102, 104 are tied to their respective sources 110, 116. However, the bulk region of the depletion mode transistor 102 may be suf?ciently high to put that other device into an 30 instead be connected to the source 116 of the enhance active operating condition in which it exhibits signifi cant gain. The need for such bias voltage usually re quires a voltage generator network on the same chip. The requirement for this network leads to increased ment mode transistor 104. The ampli?er 100 has the general characteristics of a source follower con?guration. While the gain is nomi nally unity, it has been measured as typically 0.9999, circuit complexity and degrades the performance of the 35 which compares favorably with the typical 0.9900 gain ampli?er in several respects. that would be expected for a simple source follower arrangement. Moreover, the power supply noise rejec~ SUMMARY OF THE INVENTION In accordance with the present invention an enhance» ment mode ?eld-effect transistor is connected together tion characteristics are greatly improved over those of a single transistor connected in a source follower con?gu ration, since the relatively high resistance presented to with a depletion mode ?eld effect transistor to provide the power supply voltage source VDD at the drain 108 a novel combination. The gates of the two devices are of the depletion mode transistor 102 greatly attenuates coupled together to form an input node. The drain any coupling of it to the common mode 114, from which it undergoes further attenuation to the output source conduction paths of the devices are connected in series with each other and to a bias current supply 45 node 118. means. The resulting gate-coupled transistor pair structure may be advantageously connected as a source follower ampli?er, with the output from the source of the en hancement mode device; as a common-source ampli?er, with the output from the drain of the depletion mode device; together with another, like pair for a differential input ampli?er stage; and, in conjunction with an addi tional enhancement mode transistor as a current mirror. BRIEF DESCRIPTION OF THE DRAWING FIG. 1 is a schematic circuit diagram of a source EXAMPLE OF FIG. 2 The FIG. 2 shows in accordance with another em bodiment of the invention a common source ampli?er 200 which includes an upper, depletion mode transistor 202 and a lower, enhancement mode transistor 204 with their gates coupled together to form an input node 206. The drain 208 of the depletion mode transistor 202 forms an output node 218 and is connected in series with 55 a current source 220. Its source 210 is coupled to the drain 212 of the enhancement mode transistor 204 at a common node 214. The source 216 of the enhancement mode transistor 204 is connected to a negative supply follower ampli?er circuit which includes an enhance voltage source V55. The bulk regions of both the tran ment mode and a depletion mode transistor connected 60 sistors 202, 204 are tied to their respective sources 210, together in accordance with one example of the inven 216. Again, the bulk region of the depletion mode tran tion. sistor may instead be connected to the source 216 of the FIG. 2 is a schematic circuit diagram of a common enhancement mode transistor 204. source ampli?er circuit in accordance with a second The ampli?er 200 has the general characteristics of a example of the invention. 65 common source con?guration. It has a high gain, due to FIG. 3 is a schematic circuit diagram of a differential greatly reduced output conductance at the output node input stage circuit in accordance with a third example 218, and very effective power supply noise rejection, of the invention. since the drain-source voltage of the enhancement tran 3 4,518,926 4 sistor 204 is very well controlled as a result of its gate depletion mode transistor may be connected either to coupling with the depletion mode transistor 202. the source of that transistor or to the source of the enhancement mode transistor. The choice for a particu lar circuit is primarily one based on available circuit chip area. What is claimed is: EXAMPLE OF FIG. 3 The FIG. 3 shows in accordance with a third embodi ment of the invention a differential input voltage ampli ?er stage 300 which includes two gate coupled transis tor pairs 302, 304, as described in the example of FIG. 1 above, connected in parallel with each other and in 1. The combination of a ?rst enhancement mode and a ?rst depletion mode ?eld effect transistor with their gates connected together and providing a linear input node, their drain-to-source conduction paths being con nected in series and provided with a substantially con stant bias current supply means for establishing a bias series with a current source 306, which couples the sources of their enhancement mode transistors to a neg ative supply voltage V53 ground. The differential inputs current therethrough. nodes 308, 310 are the coupled gate pairs. The output 2. The combination of claim 1 wherein said transis tors have the same conducting channel polarity. 3. The combination of claim 2 wherein the drain of said depletion mode transistor is connected to a first polarity supply voltage means and the source of said enhancement mode transistor is connected in series with nodes 312, 314 are at the drains of the depletion node transistors; the output signal is a differential current. The differential input stage 300 provides advantages similar to those obtained with the common source am pli?er 200 for each of the differential inputs. The gate coupled pair ampli?ers 302, 304 are advantageous over presently-used arrangements in that they increase the differential mode output impedance. 20 the bias current supply means to a second polarity sup ply voltage means, the gates providing an input node and the source of said enhancement mode transistor EXAMPLE OF FIG. 4 providing a substantially unity gain output node. 4. The combination of claim 2 wherein the source of The FIG. 4 shows in accordance with a fourth em bodiment of the invention a current mirror 400 which 25 said enhancement mode transistor is connected to a ?rst includes a gate-coupled pair of depletion mode and enhancement mode transistors 402, 404, respectively, polarity supply voltage means and the drain of said depletion mode transistor is connected in series with the together with an additional enhancement mode transis tor 406. The gates of the transistors 402, 404 are coupled to each other and to the gate and drain of the additional enhancement mode transistor 406. The additional en hancement mode transistor 406 has its bulk region tied bias current supply means to a second polarity supply voltage means, the gates providing an input node and the drain of said depletion mode transistor providing a voltage ampli?ed output node. 5. The combination of claim 2 comprising a second enhancement mode and a second depletion mode ?eld to its source and its source connected to the source of the ?rst enhancement mode transistor 404 at a common node coupled to a negative power supply voltage 35 effect transistor with their gates coupled together and their drain-source conduction paths connected in series with each other and in parallel with those of said ?rst source V55. The drain of the additional enhancement mode transistor 406 is connected in series with a current source 408 to an input current node 410. The drain of the depletion mode transistor 402 is connected to an output current mode 412. In response to an input current at the node 410 the transistors to form a common node of said ?rst and second enhancement transistors, said common node being connected in series with the bias current supply means to a power supply voltage means, the gates of said ?rst transistors and said second transistors provid ing differential input nodes and the drains of said ?rst and second depletion mode transistors providing re spective differential current output nodes. power supply noise rejection. The gate-coupled pair 45 6. The combination of claim 1 comprising a second enhancement mode transistor having its gate and its 402, 404 signi?cantly increases the output resistance of drain coupled to the gate of said ?rst transistors and the current mirror 400. current mirror 400 provides an ampli?er output current at node 412 which closely follows the input current in a ?xed ratio as chosen and has particularly effective connected in series with the bias current supply means to an input current node, the source of said ?rst and GENERAL CONSIDERATIONS The outputs of the above-described embodiments are second enhancement mode transistors being connected together to a ?rst polarity supply voltage means, the drain of said ?rst depletion mode transistor forming an typically taken with respect to ground potential. The term “ground” as used herein means any suitable refer output current node with a current mirror relationship to said input current node. ence potential. In general, for any ofthe gate-coupled transistor pairs in accordance with the invention the bulk region of the 55 65 * * * >l< *