SEC A - St.Joseph's College

advertisement

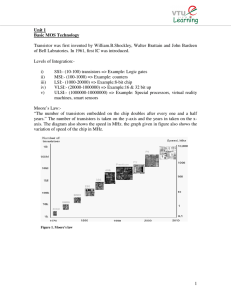

CLASS: M.Sc. ELECTRONICS 15N/401 St. JOSEPH’S COLLEGE (AUTONOMOUS) TIRUCHIRAPPALLI – 620 002 SEMESTER EXAMINATIONS – NOVEMBER 2015 TIME: 40 Minutes. MAXIMUM MARKS: 30 SEM SET PAPER CODE TITLE OF THE PAPER 3 2014 14PEL3111 VLSI DESIGN AND VHDL PROGRAMMING SECTION - A Answer all the questions: 30 1 = 30 Choose the correct answer: 1. 2. 3. 4. 5. MOS stands for__________. a) Metal oxide semiconductor b) Material oxide semiconductor c) Metal organized semiconductor d) None of the above Among the following which mode is called as normally ON mode a) Enhancement mode b) Depletion mode c) Simple mode d) None of the above. MOSFET is a __________. a) Diode b) Transistor c) Multi-junction transistor d) None of the above In n-type pass transistor having channel length L=2λ and width W=2λ, the shape of the resulting channel is ________. a) Circle b) Rectangle c) Rhombus d) Square The buried n+ layer present in ____________technologies. a) ECL b) BICMOS c) CMOS d) NMOS 6. 7. 8. 9. 10. 11. 12. 13. 14. For depletion mode transistor the gate is connected to the source, so it is always on and the mode is called __________. a) Pull down b) Enhancement pull down c) Depletion pull up d) None of the above The color code for polysilicon in stick diagram is ___________. a) Green b) Blue c) Black d) Red The sheet resistance Rs is__________. a) p/t b) pt c) p2t d) p2/At The lambda based rules require a minimum separation between thin oxide regions of __________. a) λ b) 2 λ c) 3 λ d) 4 λ Which among the following is a CAD tool? a) Layout editors b) DRC c) Circuit extraction d) All of the above DRC stands for __________. a) Design rule checker b) Design rule circuit c) Derived rule circuit d) None of the above Minimum size of the transistor is determined by _________. a) Process technology b) Physics of device c) Both (a) and (b) d) None of the above An ________ is the most basic building block in a design of VHDL programming. a) Entity b) Behavior c) Architecture d) None of the above The architecture describes the behavior of the _________. a) Entity b) Behavior c) Architecture d) None of the above 15. A single entity can have ________architectures. a) Single b) Multiple c) Double d) All the above 16. A _______Statement is used to bind a component instance to an entity-architecture pair. a) Package b) Behavior c) Configuration d) Driver 17. A ____________ is a collection of commonly used data types and subprograms used in a design. a) Package b) Driver c) Program d) Configuration 18. Which one of the following is a source on a signal? a) Package b) Driver c) Program d) Configuration 19. ________means for communication of dynamic data between entities. a) Signals b) variables c) constants d) Wires 20. _________ are used for local storage in process statements and subprograms. a) Signals b) variables c) constants d) Wires 21. _________types are used to represent numbers out of the range of integer values as well as fractional values. a) Integer b) Real c) Enumerated d) Physical 22. ________type is a very powerful tool for abstract modeling. a) Integer b) Real c) Enumerated d) Physical 23. The only predefined physical type in VHDL is________. a) WAIT b) TIME c) UNIT d) RANGE 24. _______are useful for modeling linear structures such as RAMs and ROMs. a) Array b) Record c) Variables d) None of the above 25. Which of the following is the last process in the synthesis? a) VHDL RTL Description b) unoptimized Boolean device c) Optimized Boolean device d) Gate level Netlist 26. The __________ is an estimated delay used to model the delay through a typical wire used to connect cells together. a) loading delay b) wire delay c) slope delay d) intrinsic delay 27. The process of converting the un optimized Boolean description to a PLA format is known as_________. a) flattening b) Factoring c) structuring d) All the above 28. Control flow statements such as_______ are used to demonstrate how synthesis from a higher level description is accomplished. a) IF THEN ELSE b) ELSE IF c) SWITCH CASE d) LOOP 29. The example for sequential complex statements is________. a) 4-bit comparator b) 4-bit shifter c) both of them d) none of them 30. What is the extension of programming file created in Quartus II IDE to download in FPGA? a) .sof b) .cdf c) .vhd d) .exe *********************