Lecture 3: Complementary Metal Oxide Semiconductor

advertisement

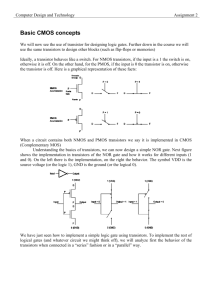

Digital VLSI design Lecture 3: Complementary Metal Oxide Semiconductor (CMOS) Complementary CMOS Complementary CMOS logic gates nMOS pull-down network pMOS pull-up network a.k.a. static CMOS pMOS pull-up network inputs output Pull-up OFF Pull-up ON Pull-down OFF Z (float) 1 Pull-down ON X (crowbar) 0 2 nMOS pull-down network Series and Parallel nMOS: 1 = ON pMOS: 0 = ON Series: both must be ON Parallel: either can be ON a a 0 g1 g2 (a) (b) a g1 g2 (c) a g1 g2 b 3 0 1 b b OFF OFF OFF ON a a a a 0 1 1 1 0 1 b b b b ON OFF OFF OFF a a a a 0 0 b 1 b 0 b 1 1 0 g2 a b a g1 a 0 0 b (d) a 0 1 1 0 1 1 b b b b OFF ON ON ON a a a a 0 0 0 1 1 0 1 1 b b b b ON ON ON OFF Conduction Complement Complementary CMOS gates always produce 0 or 1 Ex: NAND gate Series nMOS: Y=0 when both inputs are 1 Thus Y=1 when either input is 0 Requires parallel pMOS A Rule of Conduction Complements B Pull-up network is complement of pull-down Parallel -> series, series -> parallel 4 Y Compound Gates Compound gates can do any inverting function Ex: Y A B C D (AND-AND-OR-INVERT, AOI22) A C A C B D B D (a) A (b) B C D (c) C D A B (d) C D A B A B C D Y A C B D (f) (e) 5 Y Example: O3AI Y A B C D A B C D Y D A B C 6 Signal Strength Strength of signal How close it approximates ideal voltage source VDD and GND rails are strongest 1 and 0 nMOS pass strong 0 But degraded or weak 1 pMOS pass strong 1 But degraded or weak 0 Thus nMOS are best for pull-down network 7 Pass Transistors Transistors can be used as switches g=0 g s s d d g=1 s g=1 d s s 1 Input g=0 g Input g = 1 Output 0 strong 0 d s d g=0 0 g=1 d degraded 1 degraded 0 g=0 1 Output strong 1 8 Transmission Gates Pass transistors produce degraded outputs Transmission gates pass both 0 and 1 well Input g a b gb a b gb g = 0, gb = 1 a b g = 1, gb = 0 0 strong 0 g = 1, gb = 0 a b g = 1, gb = 0 strong 1 1 g g a g b gb Output a b gb 9 Tristates Tristate buffer produces Z when not enabled EN A Y 0 0 Z 0 1 Z 1 0 0 1 1 1 EN Y A EN Y A EN 10 Nonrestoring Tristate Transmission gate acts as tristate buffer Only two transistors But nonrestoring Noise on A is passed on to Y EN A Y EN 11 Tristate Inverter Tristate inverter produces restored output Violates conduction complement rule Because we want a Z output A A A EN Y Y Y EN = 0 Y = 'Z' EN = 1 Y=A EN 12 Multiplexers 2:1 multiplexer chooses between two inputs S S D1 D0 Y 0 X 0 0 0 X 1 1 1 0 X 0 1 1 X 1 D0 0 Y D1 13 1 Gate-Level Mux Design Y SD1 SD0 (too many transistors) How many transistors are needed? 20 D1 S D0 D1 S D0 Y 4 2 4 2 4 2 14 2 Y Transmission Gate Mux Nonrestoring mux uses two transmission gates Only 4 transistors S D0 Y S D1 S 15 Inverting Mux Inverting multiplexer Use compound AOI22 Or pair of tristate inverters Essentially the same thing Noninverting multiplexer adds an inverter D0 S S D1 D0 D1 S S Y S S S Y S D0 Y S D1 16 0 1 4:1 Multiplexer 4:1 mux chooses one of 4 inputs using two selects Two levels of 2:1 muxes Or four tristates S1S0 S1S0 S1S0 S1S0 D0 S0 D0 S1 0 D1 D1 1 0 Y Y D2 0 D3 1 1 D2 D3 17