Slew rate enhancement method for folded

advertisement

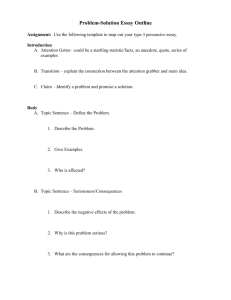

Slew rate enhancement method for folded-cascode amplifiers M. Rezaei, E. Zhian-Tabasy and S.J. Ashtiani A new circuit is proposed to enhance the slew rate (SR) of the folded-cascode amplifier (FCA). The proposed circuit is automatically activated during the slewing phase. Simulation results show a fourtimes improvement in the SR and close to 40% reduction in the settling time, compared to a conventional FCA. Introduction: In nanometre CMOS technologies, the folded-cascode amplifier (FCA) is attractive because of its advantages such as wide input common-mode range and relatively-large output swing [1]. However, as a class-A amplifier, the slew rate (SR) of the FCA is limited by the fixed current sources of the active loads. Thus, increasing the SR in a FCA requires increasing the power consumption. Several methods have been proposed for enhancing the SR in the FCA [1– 4] or improving the linearity [5, 6]. However, some of them cannot be used in low-voltage CMOS technologies [1, 2], or just improve negative or positive SR [3, 4]. In this Letter, an auxiliary circuit for the FCA is proposed, which considerably improves the positive and negative slew rate while it is OFF during the small-signal operation of the amplifier. VDD VCMFB M0 M9 Vtail VDD . Vth;n þ Veff ;n þ 2Veff ;p The current through Ma1 , Ip , mirrors with two different ratios of m and n into Ma3 and Ma5 , respectively. Increasing m improves slewing at Vo2(negative slewing), while increasing n improves slewing at Voþ (positive slewing). Since Ic ¼ It – Itail/2 and Ip ¼ Itail – It , positive (SR þ) and negative (SR 2) slew rates are given by: SRþ ¼ Ic þ nIp ¼ It Itail þ n ðItail It Þ ¼ ðn 0:5ÞItail þ ð1 nÞIt 2 ð1Þ SR ¼ ðIt Ic Þ þ mIp ¼ Itail þ m ðItail It Þ ¼ ðm þ 0:5ÞItail mIt 2 ð2Þ To have the equal positive and negative slew rates, (1) and (2) result in n ¼ m þ 1. VCMFB M10 Itail = 2Ib an auxiliary circuit composed of transistors Ma1 to Ma10 is added to the conventional FCA. With typical biasing, all the added transistors operate in the subthreshold region; thus, they have negligible effect on the small-signal operation of the OTA and do not degrade the noise performance of the circuit. During the slewing, Ma1 turns on and sinks current, and thus it does not let N2 voltage increase by more than its gate – source voltage. As a result, M0 remains in the saturation region and Itail does not decrease while the following condition is satisfied: C2 V i+ Vbc M 7 M1 Vi– M2 Ic = Ib Vin– Vo– V o+ Vbcl M5 N1 N2 M3 M4 Vout+ Vin+ CL CL CL C1 M8 Vbc Vout– C1 CL C2 Vbcl M6 Fig. 3 Capacitive gain-stage It 1.5 Vbd 1.0 Fig. 1 Conventional folded-cascode OTA Vout, V 0.5 VDD Ma9 Ma7 VCMFB M9 Vtail Vi+ Vbc M Ib4 M0 M10 Itail M1 VCMFB 1:1 Ma10 –0.5 Vi– M2 Ic 7 M8 Vbc Ib3 –1.0 Vo+ VoCL CL Ib2 Ma5 0 Ma8 Vbcl Ma3 M5 Ma1 N1 N2 M3 M4 Vbd M6 It Vbcl –1.5 25 Ib1 35 40 45 50 time, ns 55 60 65 70 75 Fig. 4 Output differential voltages in transient response of folded-cascode OTA and proposed OTA with slew rate enhancement method Ip Ma2 Ma4 1 :m 30 Ma6 :n Fig. 2 Folded-cascode OTA with proposed slew rate enhancement method Proposed slew rate enhancement method: In the conventional FCA shown in Fig. 1, when a large positive voltage is applied to the input, M1 is turned off and all the tail current, Itail , goes through M2. If the current through M8 , Ic , is less than Itail/2 , Itail is larger than the M3,4 current, It. Therefore, the voltage of node N2 increases until M0 and M2 enter the triode region and their currents decrease to It. Without considering the effect of common-mode feedback (CMFB), the negative SR is equal to (It – Ic)/C while the positive SR is smaller and equal to Ic/C. Thus the differential SR is equal to It/C. In addition, when the slewing ends, it takes more time for M0 and M2 to come back from the triode to the saturation region. To improve the limited SR and also to prevent transistors from going into the triode region during slewing, a new operational transconductance amplifier (OTA) is proposed. As shown in Fig. 2, in the new OTA, – – – FCA ——— proposed OTA Implementation and simulation results: To show the effectiveness of the proposed method, two OTAs are designed to have almost the same frequency characteristics, one with the conventional topology of FCA and the other with the proposed circuit. The OTAs are used in a simple capacitive gain-stage circuit shown in Fig. 3, with C1 and C2 equal to 2 pF and CL equal to 1 pF. Both OTAs are designed to have the same unity-gain bandwidth. Itail is equal to 300 mA in both designs. In the conventional FCA, Ic is set to 300 mA. In the new OTA, however, Ic is reduced three times to 100 mA without significant effect on the phase margin. The ratios m and n cannot be arbitrarily large owing to stability issues. Here, ratios 4 and 5 are used for m and n, respectively. Therefore, 800 and 1000 mA extra currents are pulled from and injected to positive or negative output nodes, respectively. This results in a symmetric positive and negative SR of about 550 V/ms. By decreasing the bias voltage of M5 , and M6 , Vbcl , the leakage current of Ma1 and Ma2 is reduced to 50 nA. The circuits are implemented in a 0.18 mm standard CMOS technology and ELECTRONICS LETTERS 9th October 2008 Vol. 44 No. 21 simulated by HSPICE. The transient responses of both designed OTAs are shown in Fig. 4. As can be seen, the proposed circuit has a higher slew rate. Fig. 5 shows the currents of the SR-enhancing transistors (Ib1 to Ib4). As can be seen, during slewing the output current is considerably increased, while the output currents are unchanged after the slewing. The performance of both circuits is summarised in Table 1 for a 1.4 V differential input voltage step. As listed in Table 1, for almost the same bandwidth, the proposed slew rate enhancement method has reduced the total settling time by 39% while consuming 31% less power compared to the FCA. In addition, the total harmonic distortion (THD) is simulated for both OTAs, in a sample and hold structure, similar to the circuit shown in Fig. 3, with ideal switches. As listed in Table 1, for a sampling rate of 75 MS/s, the proposed OTA has an improvement in excess of 27 dB. # The Institution of Engineering and Technology 2008 28 July 2008 Electronics Letters online no: 20082200 doi: 10.1049/el:20082200 M. Rezaei, E. Zhian-Tabasy and S.J. Ashtiani (School of Electrical and Computer Engineering, Faculty of Engineering, University of Tehran, Campus No. 2, North Karegar Avenue, Tehran, Iran) E-mail: ezhian@ieee.org 1.5 1.0 current, mA Conclusions: A modified folded-cascode OTA with improved positive and negative slew rate is presented. An auxiliary circuit is used to boost the transient currents during the slewing mode. Circuit-level simulations show that the proposed circuit settles 39% faster and consumes 31% less power compared to the conventional FCA, while both designs have almost the same bandwidth. References Ib1 Ib2 0.5 0 –0.5 Ib4 Ib3 –1.0 –1.5 30 35 40 45 50 55 time, ns 60 65 70 75 Fig. 5 Excessive drawn currents from output nodes in transient response of folded-cascode OTA and proposed OTA with slew rate enhancement method ——— Ib1 – – – – Ib2 – B – B Ib3 B B BB B Ib4 1 Razavi, B.: ‘Design of analog CMOS integrated circuits’ (McGraw-Hill, New York, USA, 2001) 2 Johns, D., and Martin, K.: ‘Analog integrated circuit design’ (Wiley, New York, USA, 1997) 3 Subramaniam, P.C., Manoj, C.R., and Karemulla, T.M.: ‘High slew-rate CMOS operational amplifier’, Electron. Lett., 2003, 39, (8), pp. 640–641 4 Nagaraj, K.: ‘Slew rate enhancement technique for CMOS output buffers’, Electron. Lett., 1989, 25, (19), pp. 1304–1305 5 Lewinski, A., and Silva-Martinez, J.: ‘A high-frequency transconductor using a robust nonlinearity cancellation’, IEEE Trans. Circuits Syst. II: Express Briefs, 2006, 53, (9), pp. 896– 900 6 Huang, W., and Sánchez-Sinencio, E.: ‘Robust highly linear highfrequency CMOS OTA with IM3 below 270 dB at 26 MHz’, IEEE Trans. Circuits Syst. I: Regular Papers, 2006, 53, (7), pp. 1433–1447 Table 1: Performance comparison of FCA and proposed OTA Parameter FCA Proposed OTA Total load capacitance (pF) 2 2 UGBW (MHz) 320 300 Power (mA) 1200 820 Gain (dB) 51 53 PM (deg) SR (V/ms) 0.1% settling time (ns) THD at fs ¼ 45MS/s (dB) 85 303 10.8 81 1280 6.6 67 74 THD at fs ¼ 75MS/s (dB) Input applied voltage (Vpp) Supply voltage (V) Technology 42 69 1.4 1.4 1.8 1.8 0.18 mm 1P6M CMOS ELECTRONICS LETTERS 9th October 2008 Vol. 44 No. 21