ECEN 248: Introduction to Digital System Design Department of

advertisement

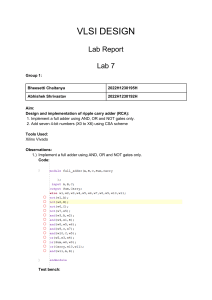

ECEN 248: Introduction to Digital System Design Department of Electrical Engineering Texas A&M University Assignment #4 Due Thursday, October 8, 2009 1. [25 points.] Check the online solution for HW2, Question 1 (c). Write a structural Verilog netlist for this design. Note that you should first create separate modules for each of the gates that you use in your answer. Do not use any built-in Verilog gates (see page 7 of the Verilog notes if you are in doubt about the meaning of built-in gates). Then instantiate the modules of these gates as appropriate, to realize the design of Queston 1 (c) of HW2. 2. [25 points.] Consider an adder which adds two numbers a and b. Let us refer to the LSB of a is a0 , and the LSB of b as b0 . The result is referred to as c. The adder is built using only AND, OR or INV gates. (a) Assume that a is an M bit number, and b is an N bit number. Both a and b are unsigned. What is the number of bits in c? (b) Suppose M is 3 and N is 5. Draw a ripple carry adder circuit which implements c. Do not use half-adders in your design. (c) How many gates does your adder of the previous part utilize? (d) If you were allowed to use half adders, what is the minimum number of gates that your adder needs? 1