Lecture 20 Review: MOSFET Amplifier Design MOSFET Models

advertisement

4/17/2008

Lecture 20

Review: MOSFET Amplifier Design

• A MOSFET amplifier circuit should be designed to

OUTLINE

• Review of MOSFET Amplifiers

• MOSFET Cascode Stage

• MOSFET Current Mirror

1. ensure that the MOSFET operates in the saturation region, 2. allow the desired level of DC current to flow, and

3. couple to a small‐signal input source and to an output “load”.

Æ Proper “DC biasing” is required!

(

(DC analysis using large‐signal MOSFET model)

l

l

l

d l)

• Reading: Chapter 9

• Key amplifier parameters: (AC analysis using small‐signal MOSFET model)

– Voltage gain Av ≡ vout/vin

– Input resistance Rin ≡ resistance seen between the input node and ground (with output terminal floating)

– Output resistance Rout ≡ resistance seen between the output node and ground (with input terminal grounded)

EE105 Spring 2008

Lecture 20, Slide 1

Prof. Wu, UC Berkeley

MOSFET Models

EE105 Spring 2008

Lecture 20, Slide 2

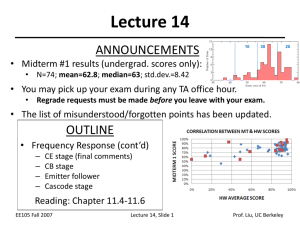

Comparison of Amplifier Topologies

• The large‐signal model is used to determine the DC operating point (VGS, VDS, ID) of the MOSFET.

Common Source

• Large Av < 0

Common Gate

• Large Av > 0

‐ degraded by RS

• Small Rin

‐ decreased by RS

– determined

determined by biasing by biasing

circuitry

• Rout ≅ RD

• The small‐signal model is used to determine how the output responds to an input signal.

• Rout ≅ RD

• ro decreases Av & Rout

• ro decreases Av & Rout

but impedance seen

looking into the drain

can be “boosted” by source degeneration

Lecture 20, Slide 3

Prof. Wu, UC Berkeley

EE105 Spring 2008

Common Source Stage

Source Follower

• 0 < Av ≤ 1

‐degraded by RS

• Large Rin

EE105 Spring 2008

Prof. Wu, UC Berkeley

but impedance seen

looking into the drain can be “boosted” by source degeneration

• Large Rin

– determined by biasing circuitry

• Small Rout ‐ decreased by RS

• ro decreases Av & Rout

Lecture 20, Slide 4

Prof. Wu, UC Berkeley

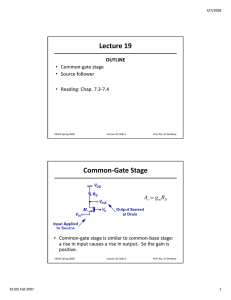

Common Gate Stage

λ =0

λ =0

Av =

R1 || R2

− RD

⋅

RG + R1 || R2 1 + R

S

gm

Rin = R1 || R2

Rout = R D

EE105 Spring 2008

EE105 Fall 2007

λ≠0

Rout ≅ RD (rO + g m rO RS )

Lecture 20, Slide 5

Prof. Wu, UC Berkeley

Av =

RS || (1/ gm )

⋅ gm RD

RS || (1/ gm ) + RG

Rin ≈

1

RS

gm

Rout = RD

EE105 Spring 2008

λ≠0

Rout ≅ RD (rO + g m rO RS )

Lecture 20, Slide 6

Prof. Wu, UC Berkeley

1

4/17/2008

Source Follower

CS Stage Example 1

• M1 is the amplifying device; M2 and M3 serve as the load.

Equivalent circuit for small-signal analysis,

showing resistances connected to the drain

λ≠0

λ =0

Av =

RS

1

+ RS

gm

Av =

Rin = RG

Rout =

rO || RS

1

+ rO || RS

gm

Rin = R G

1

|| RS

gm

Rout =

EE105 Spring 2008

1

|| ro || RS

gm

Lecture 20, Slide 7

Prof. Wu, UC Berkeley

⎛ 1

⎞

Av = − g m1 ⎜⎜

|| rO3 || rO 2 || rO1 ⎟⎟

g

⎝ m3

⎠

1

Rout =

|| rO3 || rO 2 || rO1

g m3

EE105 Spring 2008

Lecture 20, Slide 8

Prof. Wu, UC Berkeley

CS Stage Example 2

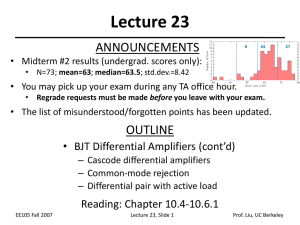

CS Stage vs. CG Stage

• M1 is the amplifying device; M3 serves as a source (degeneration) resistance; M2 serves as the load. • With the input signal applied at different locations, these circuits behave differently, although they are identical in other aspects.

Equivalent circuit for small-signal analysis

Common gate amplifier

Common source amplifier

λ1 ≠ 0

λ1 = 0

λ2 = 0

Av = −

rO2

1

1

+ || rO3

gm1 gm3

EE105 Spring 2008

Lecture 20, Slide 9

Av = −gm1{[(1+ gm2rO2 )RS + rO2 ] || rO1}

Prof. Wu, UC Berkeley

EE105 Spring 2008

Lecture 20, Slide 10

Av =

rO1

1

+ RS

gm2

Prof. Wu, UC Berkeley

Composite Stage Example 1

Composite Stage Example 2

• By replacing M1 and the current source with a Thevenin equivalent circuit, and recognizing the right side as a CG stage, the voltage gain can be easily obtained. • This example shows that by probing different nodes in a circuit, different output signals can be obtained.

• Vout1 is a result of M1 acting as a source follower, whereas Vout2

is a result of M1 acting as a CS stage with degeneration.

1

|| rO2

vout1

g m2

=

1

1

vin

+

|| rO2

gm1 gm2

λ1 = 0

EE105 Spring 2008

EE105 Fall 2007

λ1 = 0

λ2 = 0

Av =

Lecture 20, Slide 11

1

|| rO3 || rO4

vout 2

g m3

=−

1

1

vin

|| rO2

+

g m1 gm2

RD

1

1

+

g m 2 g m1

Prof. Wu, UC Berkeley

EE105 Spring 2008

Lecture 20, Slide 12

Prof. Wu, UC Berkeley

2

4/17/2008

NMOS Cascode Stage

PMOS Cascode Stage

Rout = (1 + g m1rO1 )rO 2 + rO1

Rout = (1 + g m1rO1 )rO 2 + rO1

Rout ≈ g m1rO1rO 2

Rout ≈ g m1rO1rO 2

• Unlike a BJT cascode, the output impedance is not limited by β.

EE105 Spring 2008

Lecture 20, Slide 13

Prof. Wu, UC Berkeley

Short‐Circuit Transconductance

EE105 Spring 2008

Lecture 20, Slide 14

Prof. Wu, UC Berkeley

Transconductance Example

• The short‐circuit transconductance is a measure of the strength of a circuit in converting an input voltage signal into an output current signal:

Gm ≡

• The voltage gain of a linear circuit is

iout

vin

vout = 0

Gm = g m1

Av = −Gm Rout

(Rout is the output resistance of the circuit)

EE105 Spring 2008

Lecture 20, Slide 15

Prof. Wu, UC Berkeley

MOS Cascode Amplifier

EE105 Spring 2008

Lecture 20, Slide 16

Prof. Wu, UC Berkeley

PMOS Cascode Current Source as Load

• A large load impedance can be achieved by using a PMOS cascode current source.

Av = −Gm Rout

RoN ≈ g m 2 rO 2 rO 1

Av ≈ − g m1rO1 g m 2 rO 2

Rout = RoN || RoP

Av ≈ − g m1 [(1 + g m 2 rO 2 )rO1 + rO 2 ]

EE105 Spring 2008

EE105 Fall 2007

Lecture 20, Slide 17

Prof. Wu, UC Berkeley

RoP ≈ g m 3 rO 3 rO 4

EE105 Spring 2008

Lecture 20, Slide 18

Prof. Wu, UC Berkeley

3

4/17/2008

MOS Current Mirror

MOS Current Mirror – NOT!

• The motivation behind a current mirror is to duplicate a (scaled version of the) “golden current” to other locations.

Current mirror concept

Generation of required VGS

1

⎛W ⎞

2

I REF = μnCox ⎜ ⎟ (VX − VTH )

2

⎝ L ⎠ REF

VX =

2 I REF

μ n Cox (W / L )1

EE105 Spring 2008

+ VTH 1

• This is not a current mirror, because the relationship between VX and IREF is not clearly defined.

Current Mirror Circuitry

I copy1 =

1

⎛W ⎞

μ nCox ⎜ ⎟ (VX − VTH )2

2

⎝ L ⎠1

I copy1 =

(W / L )1

(W / L )REF

Lecture 20, Slide 19

I REF

Prof. Wu, UC Berkeley

Example: Current Scaling • The only way to clearly define VX with IREF is to use a diode‐

connected MOS since it provides square‐law I‐V relationship. EE105 Spring 2008

Lecture 20, Slide 20

Prof. Wu, UC Berkeley

Impact of Channel‐Length Modulation

• MOS current mirrors can be used to scale IREF up or down λ≠0

– I1 = 0.2mA; I2 = 0.5mA

1

⎛W ⎞

μ nCox ⎜ ⎟ (VX − VTH )2 [1 + λ (VDS1 − VD ,sat )]

2

⎝ L ⎠1

1

⎛W ⎞

2

= μ n Cox ⎜ ⎟ (VX − VTH ) [1 + λ (VDS1 − VGS + VTH )]

2

⎝ L ⎠1

I copy1 =

λ = 0:

1

⎛W ⎞

2

I REF = μnCox ⎜ ⎟ (VX − VTH ) [1 + λ (VGS − VD,sat )]

2

⎝ L ⎠ REF

1

⎛W ⎞

2

= μnCox ⎜ ⎟ (VX − VTH ) [1 + λVTH ]

2

⎝ L ⎠ REF

I copy1 =

EE105 Spring 2008

Lecture 20, Slide 21

Prof. Wu, UC Berkeley

(W / L )1

(W / L )REF

EE105 Spring 2008

I REF

(W / L )1 I ⎛⎜1 + λ (VDS1 − VGS ) ⎞⎟

1 + λ (VDS 1 − VGS + VTH )

=

(W / L )REF REF ⎜⎝

1 + λVTH

1 + λVTH ⎟⎠

Lecture 20, Slide 22

Prof. Wu, UC Berkeley

CMOS Current Mirror

EE105 Spring 2008

EE105 Fall 2007

Lecture 20, Slide 23

Prof. Wu, UC Berkeley

4