The Sub-Micron MOS Transistor -

advertisement

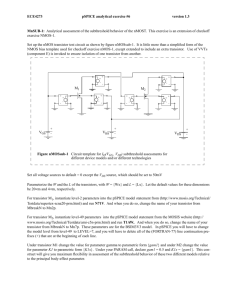

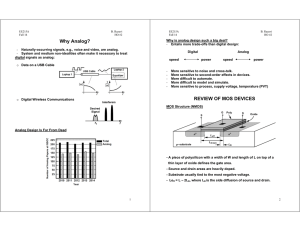

The Sub-Micron MOS Transistor q Subthreshold Conduction q Threshold Variations q Parasitic Resistances Subthreshold Conduction Current does not drop abruptly to 0 at VGS =VT. The device is partly conducting -> subthreshold conduction or weak-inversion conduction. Current decays in an exponential fashion for VGS< VT (similar to a bipolar transistor – in essence, in the absence of a conducting channel, the n+ (source)-p (bulk)-n+ (drain) terminals actually form a parasitic bipolar transistor. The current in this region is approximated by: -2 V DS 1 − e kT / q (1 + λVDS ) Linear -4 10 -6 Quadratic 10 ID (A) I D = IS e VGS nkT / q 10 -8 10 -10 Exponential -12 VT 10 10 0 0.5 1 1.5 VGS(V) 2 2.5 Sub-Threshold Conduction Typically, we prefer that the current drop as fast as possible once V GS < VT . The rate of decline of the current at VGS < VT is a quality measure of a device => well known as subthreshold slope factor (S). This factor can be quantified as kT S = n ln(10) q By how much does V GS have to be reduced for an order of magnitude reduction in drain current (mV/decade)? S=60mV/decade = sharpest possible roll-off (n=1). Roll-off is reduced as temp. increases. Typical values are in the 90mV/decade range. Immediate problems due to subthreshold leakage exist in dynamic circuits and memory, which reply on the storage of charge on a capacitor. -2 10 Linear -4 10 -6 Quadratic ID (A) 10 -8 10 -10 Exponential -12 VT 10 10 0 0.5 1 VGS (V) 1.5 2 2.5 Threshold Variations VT Long-channel threshold L Threshold as a function of the length (for low VDS) VT Low VDSthreshold VDS Drain-induced barrier lowering (for low L) Typically, the channel depletion region is solely due to the applied gate voltage, and that all depletion charge beneath the gate originates from the MOS field effects. This ignores the depletion regions of the source and reverse-biased drain junction, which become important with shrinking channel lengths. Since a part of the region below the gate is already depleted (by the source and drain fields), a smaller threshold voltage suffices to cause strong inversion. Thus, V T0 decreases with L for short-channel devices. A similar effect is obtained by raising the V DS, as this increases the width of the drain-junction depletion region. Consequently, V T decreases with increasing VDS. The effect is known as drain-induced barrier lowering (DIBL), causing V T to be a function of VDS. For high enough values of V D, the source and drain regions can even be shorted together, and normal device operation ceases to exist. The sharp increase in current that results from this effect is called punchthrough. It defines an upper bound of V DS that can be applied to a device, before causing permanent damage to the device. Hot Carriers Due to scaling of device dimensions, while the power supply and operating voltages have not scaled accordingly, has resulted in large electrical fields. This has caused an increase in the electrons’ velocity, which can leave the silicon and tunnel into the gate oxide upon reaching a sufficiently high level of energy. Electrons trapped in the oxide change the threshold voltage (increasing VT for NMOS devices). For an electron to become hot, an electrical field of at least 104 V/cm is necessary. This condition is easily met in submicron devices. The channel hot electrons effect is mainly caused by electrons flowing in the channel region, from source to drain. This effect is more pronounced at large VDS, as which the lateral electric field in the drain end of the channel accelerates the electrons. The electrons arriving at the Si-SiO2 interface with enough kinetic energy to surmount the surface potential barrier are injected into the oxide. Process Variations W T H=ILD S Ground plane Year Leff Tox Vdd Vt W H ρ 1997 32 8 10 10 25 25 22 1999 33 8 10 10 26 33 24 2002 35 10 10 10 28 30 27 2005 40 12 10 12 30 34 32 2006 47 16 10 14 33 36 33 % variation from mean value Process Variations Example: Minimum sized NMOS device in 0.25µm CMOS technology. VGS=VDS=2.5V => ID= 220µA. Using fast & slow models, modify the length and width by ±10%, threshold ±60mV, and oxide thickness ±5%. Thus for fast: ID = 265µA: +20% slow: ID = 182µA: -17% Spice Model for the MOS Transistor q Several MOS Models have been developed q Model complexity is a trade-off between accuracy and simulator run time In SPICE, model complexity is set by LEVEL parameter Level 1: spice model is based on long channel MOS I-V equation (no longer used) Level 2: geometry, physics based. Handles short channel effects (e.g., velocity saturation) – however too complex Level 3: semi-empirical model (mix of analytical and empirical expressions) Level 4: empirical model based on extracted values from experimental data (widely used) q q q q q q Several other models are available: virtually every semiconductor fab has a model development group Technology Scaling Ever since ICs were invented, dimensions are scaled to: q Integrate more devices in the same die area q Allow higher operational speed Scaling has profound impact on many aspects of ICs Constant Voltage Scaling q All device dimensions are scaled by a factor S. This method of scaling was followed till 0.8 micron. For lower geometries, higher electric field resulted in poor device reliability. q Therefore, for advanced technologies today “Constant Field Scaling” is followed: Constant Field Scaling