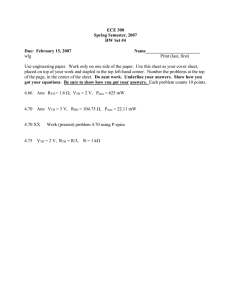

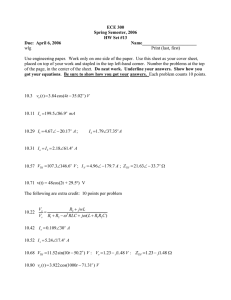

Lecture 17

advertisement

4/1/2008

Lecture 17

Body Effect Example

OUTLINE

• NMOSFET in ON state (cont’d)

– Body effect

– Channel‐length modulation

– Velocity saturation

y

VTH = VTH 0 + γ

• NMOSFET in OFF state

• MOSFET models

• PMOSFET

where γ =

Lecture 17, Slide 1

2qN Aε Si

Cox

)

Example:

Typical values

γ ~ 0.5

ϕ B = 0.48V for N A = 1018 cm−3

produce a VTH shift of 0.2V

Prof. Wu, UC Berkeley

EE105 Spring 2008

• The pinch‐off point moves toward the source as VDS increases.

Æ The length of the inversion‐layer channel becomes shorter with increasing VDS.

Æ ID increases (slightly) with increasing VDS in the saturation region of operation.

Lecture 17, Slide 2

Prof. Wu, UC Berkeley

λ and L

Channel‐Length Modulation

• The effect of channel‐length modulation is less for a long‐

channel MOSFET than for a short‐channel MOSFET.

λ∝

I Dsat ∝

2ϕB + VSB − 2ϕ B

(substrate doping)

A substrate bias of VSB = 1V

• Reading: Finish Chap. 6

EE105 Spring 2008

(

1

⇒ short channel MOSFET has larger λ

L

1

1 ⎛ ΔL ⎞

≅ ⎜1 +

⎟

L − ΔL L ⎝

L ⎠

ΔL ∝ (VDS − VDSsat )

1

W

2

μnCox (VGS − VTH ) ⎡⎣1 + λ (VDS − VD , sat ) ⎤⎦

2

L

λ: channel length modulation coefficient

I D , sat =

* Note: in Razavi: I D ,sat =

EE105 Spring 2008

EE105 Fall 2007

1

W

2

μn Cox (VGS − VTH ) [1 + λVDS ]

2

L

Lecture 17, Slide 3

Prof. Wu, UC Berkeley

EE105 Spring 2008

Lecture 17, Slide 4

Prof. Wu, UC Berkeley

1

4/1/2008

Velocity Saturation

Impact of Velocity Saturation

• In state‐of‐the‐art MOSFETs, the channel is very short (<0.1μm); hence the lateral electric field is very high and carrier drift velocities can reach their saturation levels.

– The electric field magnitude at which the carrier velocity saturates is Esat.

Saturation

v

Velocity: vsat

E

Drift velocity: v = μ E

Slope = μ

EE105 Spring 2008

• Recall that I D = WQinv ( y)v( y)

• If VDS > Esat×L, the carrier velocity will saturate and hence the drain current will saturate:

⎧8 ×106 cm/s for electrons in Si

vsat = ⎨

6

⎩ 6 ×10 cm/s for holes in Si

⎧⎪ NMOS: μn ≈ 250 cm 2 /V-s ⇒ Esat ≈ 30, 000 V/cm

⎨

2

⎪⎩ PMOS: μ n ≈ 80 cm /V-s ⇒ Esat ≈ 80, 000 V/cm

For L = 0.1 μ m

I D,sat = WQinvvsat = WCox (VGS − VTH )vsat

• ID,sat is proportional to VGS–VTH rather than (VGS – VTH)2

• ID,sat is not dependent on L

• ID,sat is dependent on W

⎧⎪VD , sat = 0.3 V for NMOS

⎨

⎪⎩VD , sat = 0.8 V for PMOS

Lecture 17, Slide 5

Prof. Wu, UC Berkeley

Short‐Channel MOSFET ID‐VDS

EE105 Spring 2008

Lecture 17, Slide 6

Prof. Wu, UC Berkeley

Drain Induced Barrier Lowering (DIBL)

• In a short‐channel MOSFET, the source & drain regions each “support” a significant fraction of the total channel depletion charge Qdep×W×L

Æ VTH is lower than for a long‐channel MOSFET

DIBL

Injection

Barrier

Source

P. Bai et al. (Intel Corp.),

Int’l Electron Devices Meeting, 2004.

ShortChannel

LongChannel

-qVDS

Drain

• ID,sat is proportional to VGS‐VTH rather than (VGS‐VTH)2

• VD,sat is smaller than VGS‐VTH

• Channel‐length modulation is apparent (?)

EE105 Spring 2008

EE105 Fall 2007

Lecture 17, Slide 7

Prof. Wu, UC Berkeley

Drain

• As the drain voltage increases, the reverse bias on the body‐drain PN junction increases, and hence the drain depletion region widens.

ÆVTH decreases with increasing drain bias.

(The barrier to carrier diffusion from the source into the channel is reduced.)

Æ ID increases with increasing drain bias.

EE105 Spring 2008

Lecture 17, Slide 8

Prof. Wu, UC Berkeley

2

4/1/2008

NMOSFET in OFF State

Sub‐Threshold Leakage Current

• We had previously assumed that there is no channel current when VGS < VTH. This is incorrect!

• As VGS is reduced below VTH (towards 0 V), the potential barrier to carrier diffusion from the source into the channel is increased. ID becomes limited by carrier diffusion into the channel, rather than by carrier drift through the channel

than by carrier drift through the channel.

(This is similar to the case of a PN junction diode!)

ÆID varies exponentially with the potential barrier height at the source, which varies directly with the channel potential.

• Recall that, in the depletion (sub‐threshold) region of operation, the channel potential is capacitively coupled to the gate potential. A change in gate voltage (ΔVGS) results in a change in channel voltage (ΔVCS):

⎛ Cox

ΔVCS = ΔVGS × ⎜

⎜C +C

d

dep

⎝ ox

⎞

Cdep

>1

⎟⎟ ≡ ΔVGS / m ; m = 1 +

Cox

⎠

• Therefore, the sub‐threshold current (ID,subth) decreases exponentially with linearly decreasing VGS/m

ID

log (ID)

Sub-threshold swing:

−1

VGS

VTH

EE105 Spring 2008

Lecture 17, Slide 9

Prof. Wu, UC Berkeley

Short‐Channel MOSFET ID‐VGS

VGS

VTH

EE105 Spring 2008

⎛ d (log10 I DS ) ⎞

S ≡⎜

⎟

dVGS

⎝

⎠

S = mVT ln(10) > 60mV/dec

Lecture 17, Slide 10

Prof. Wu, UC Berkeley

VTH Design Trade‐Off

• Low VTH is desirable for high ON‐state current:

1 < η < 2

ID,sat ∝ (VDD ‐ VTH)η

• But high VTH is needed for low OFF‐state current:

log ID

P. Bai et al. (Intel Corp.),

Int’l Electron Devices Meeting, 2004.

Low VTH

ÆVTH cannot be

reduced aggressively.

High VTH

IOFF,low VTH

IOFF,high VTH

0

EE105 Spring 2008

EE105 Fall 2007

Lecture 17, Slide 11

Prof. Wu, UC Berkeley

EE105 Spring 2008

VGS

Lecture 17, Slide 12

Prof. Wu, UC Berkeley

3

4/1/2008

MOSFET Large‐Signal Models (VGS > VTH)

• Depending on the value of VDS, the MOSFET can be represented with different large‐signal models. VDS << 2(VGS-VTH)

Triode Region

Saturation Region

VDS < VD,sat

VDS > VD,sat

MOSFET Transconductance, gm

• Transconductance (gm) is a measure of how much the drain current changes when the gate voltage changes.

gm ≡

∂I D

∂VGS

For amplifier applications, the MOSFET is usually operating in amplifier applications, the MOSFET is usually operating in

• For

the saturation region.

– For a long‐channel MOSFET:

g m = μn Cox

RON =

1

μ n Cox

W

(VGS − VTH )

L

ID,tri = μnCox

W⎡

V ⎤

(VGS −VTH ) − DS ⎥VDS

2⎦

L ⎢⎣

1

W

2

ID,sat = μnCox (VGS −VTH) [1+λ(VDS −VD,sat)]

2

L

or

ID,sat = vsatWCox(VGS −VTH)[1+λ(VDS −VD,sat)]

EE105 Spring 2008

Lecture 17, Slide 13

Prof. Wu, UC Berkeley

{

}

W

2I D

(VGS − VTH ) 1 + λ (VDS − VD, sat ) =

L

VGS − VTH

– For a short‐channel MOSFET:

{

}

g m = vsatWCox 1 + λ (VDS − VD , sat ) =

EE105 Spring 2008

Lecture 17, Slide 14

ID

VGS − VTH

Prof. Wu, UC Berkeley

MOSFET Small‐Signal Model Derivation of Small‐Signal Model (Saturation Region of Operation)

(Long‐Channel MOSFET, Saturation Region)

• The effect of channel‐length modulation or DIBL (which cause ID to increase linearly with VDS) is modeled by the transistor output resistance, ro.

1

W

2

I D = μnCox (VGS − VTH ) ⎡⎣1 + λ (VDS − VD,sat ) ⎤⎦

2

L

1

∂I

∂I

∂I

id = D vgs + D vbs + D vds ≡ gmvgs + gmb vbs + vds

ro

∂VGS

∂VBS

∂VDS

gmvgs

gmbvbs

id

vgs

ro ≡

EE105 Spring 2008

EE105 Fall 2007

∂V DS

1

≈

∂I D

λI D

Lecture 17, Slide 15

Prof. Wu, UC Berkeley

EE105 Spring 2008

Lecture 17, Slide 16

Prof. Wu, UC Berkeley

4

4/1/2008

PMOS Transistor

PMOS I‐V Equations

• A p‐channel MOSFET behaves similarly to an n‐channel MOSFET, except the polarities for ID and VGS are reversed.

Schematic cross-section

Circuit symbol

1

W

μ p Cox ⎡⎣ 2 (VSG − VTH )VDS − VDS2 ⎤⎦

2

L

1

W

2

= μ p Cox ⎣⎡ 2 ( VGS − VTH ) VDS − VDS

⎦⎤

2

L

Long Channel:

I D ,tri =

DS ↔ SD GS ↔ SG

1

W

2

μ p Cox (VSG − VTH ) ⎡⎣1 + λ (VSD − VSD, sat ) ⎦⎤

2

L

2

1

W

= μ p Cox ( VGS − VTH ) ⎡1 + λ VDS − VD , sat ⎤

⎣

⎦

2

L

Short Channel:

I D , sat =

(

• The small‐signal model for a PMOSFET is the same as that for an NMOSFET.

– The values of gm and ro will be different for a PMOSFET vs. an NMOSFET, since mobility & saturation velocity are different for holes vs. electrons. EE105 Spring 2008

Lecture 17, Slide 17

Prof. Wu, UC Berkeley

CMOS Technology

I D , sat = vsatWCox (VSG − VTH ) ⎣⎡1 + λ (VSD − VSD , sat ) ⎦⎤

(

)

)

= vsatWCox ( VSG − VTH ) ⎡1 + λ VDS − VD , sat ⎤

⎣

⎦

Note: VGS < 0,VDS < 0,VD , sat < 0,VTH < 0 in PMOS

EE105 Spring 2008

Lecture 17, Slide 18

Prof. Wu, UC Berkeley

Comparison of BJT and MOSFET

• It possible to form deep n‐type regions (“well”) within a p‐type substrate to allow PMOSFETs and NMOSFETs to be co‐fabricated on a single substrate. • This is referred to as CMOS (“Complementary MOS”) technology.

• The BJT can achieve much higher gm than a MOSFET, for a given bias current, due to its exponential I‐V characteristic.

(Long-Channel)

(Short-Channel)

MOSFET

Schematic cross-section of CMOS devices

Linear

VGS > VDsat ; VDsat = Esat L

VGS < VDsat

EE105 Spring 2008

EE105 Fall 2007

Lecture 17, Slide 19

Prof. Wu, UC Berkeley

EE105 Spring 2008

Lecture 17, Slide 20

Prof. Wu, UC Berkeley

5