Bipolar Junction Transistor (BJT)

advertisement

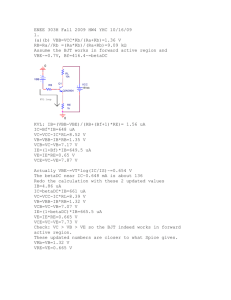

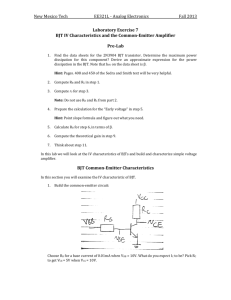

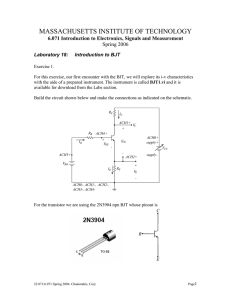

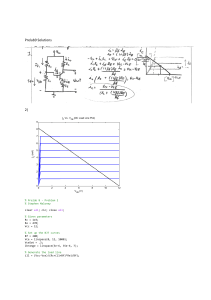

Bipolar Junction Transistor (BJT) Lecture notes: Sec. 3 Sedra & Smith (6th Ed): Sec. 6.1-6.4* Sedra & Smith (5th Ed): Sec. 5.1-5.4* * Includes details of BJT device F. Najmabadi, ECE65, Winter 2012 operation which is not covered in this course A BJT consists of three regions NPN transistor Simplified physical structure An implementation on an IC Device construction is NOT symmetric Device is constructed such that BJT does NOT act as two diodes back to back (when voltages are applied to all three terminals). F. Najmabadi, ECE65, Winter 2012 o “Thin” base region (between E & C) o Heavily doped emitter o Large area collector BJT iv characteristics includes four parameters NPN transistor Six circuit variables: (3 i and 3 v) Two can be written in terms of the other four: KCL : iE = iC + iB KVL : vBC = vBE − vCE Circuit symbol and Convention for current directions (Note: vCE = vC – vE) BJT iv characteristics is the relationship among (iB , iC , vBE , and vCE ) It is typically derived as iB = f (vBE ) iC = g (iB , vCE ) F. Najmabadi, ECE65, Winter 2012 BJT operation in the “active” mode BE junction is forward biased (vBE = VD0) As Emitter is heavily doped, a large number of electrons diffuse into the base (only a small fraction combine with holes) The number of these electrons scales as e vBE / VT If the base is “thin” these electrons get near the depletion region of BC junction and are swept into the collector if vCB ≥ 0 (vBC ≤ 0 : BC junction is reverse biased!) iC = I S e vBE / VT Active mode: iB = iC β = IS β iC = I S e vBE / VT vCE ≥ VD 0 F. Najmabadi, ECE65, Winter 2012 e v BE / VT In this picture, ic is independent of vBC (and vCE ) as long as vBC = vBE − vCE = VD 0 − vCE ≤ 0 vCE ≥ VD 0 Base current is also proportional to e vBE / VT and therefore, iC : iB = iC/β BJT operation in saturation mode BE junction is forward biased (vBE = VD0) Similar to the active mode, a large number of electrons diffuse into the base. For vBC ≥ 0 BC junction is forward biased and a diffusion current will set up, reducing iC . 1. Soft saturation: vCE ≥ 0.3 V (Si)* vBC ≤ 0.4 V (Si), diffusion current is small and iC is very close to its active-mode level. “Deep” Saturation mode: iB = IS e vBE / VT β iC < β iB vCE ≈ Vsat F. Najmabadi, ECE65, Winter 2012 2. Deep saturation region: 0.1 < vCE < 0.3 V (Si) or vCE ≈ 0.2 V = Vsat (Si), iC is smaller than its active-mode level (iC < β iB). o Called saturation as iC is set by outside circuit & does not respond to changes in iB. 3. Near cut-off: vCE ≤ 0.1 V (Si) Both iC & iB are close to zero. * Sedra & Smith includes this in the active region, i.e., BJT is in active mode as long as vCE ≥ 0.3 V. BJT iv characteristics includes four parameters NPN transistor Circuit symbol and Convention for current directions (Note: vCE = vC – vE) Simplified physical structure BJT iv characteristics is the relationship among (iB , iC , vBE , and vCE ) It is typically derived as iB = f (vBE ) iC = g (iB , vCE ) F. Najmabadi, ECE65, Winter 2012 BJT iv characteristics: iB = f(vBE) & iC = g(iB , vCE) Saturation: BE is forward biased, BC is forward biased 1. Soft saturation: 0.3 ≤ vCE ≤ 0.7 V, iC ≈ β iB 2. Deep saturation: 0.1 ≤ vCE ≤ 0.3 V, iC < β iB 3. Near cut-off: vCE ≤ 0.1 V, iC ≈ 0 iB Cut-off : BE is reverse biased F. Najmabadi, ECE65, Winter 2012 iB = 0, iC = 0 Active: BE is forward biased BC is reverse biased iC = β iB Early Effect modifies iv characteristics in the active mode iC is NOT constant in the active region. Early Effect: Lines of iC vs vCE for different iB (or vBE ) coincide at vCE = − VA v iC = I S e vBE / VT 1 + CE VA F. Najmabadi, ECE65, Winter 2012 NPN BJT iv equations “Linear” model Cut-off : BE is reverse biased Active: BE is forward biased BC is reverse biased (Deep) Saturation: BE is forward biased BC is reverse biased iB = 0, iB = iC β = iC = I S e iB = IS β iB = 0, iC = 0 IS β v BE / VT vBE < VD 0 e vBE / VT vCE 1 + VA e vBE / VT vCE ≈ Vsat , iC < β iB vBE = VD 0 , iB ≥ 0 iC = β iB , vCE ≥ VD 0 vBE = VD 0 , iB ≥ 0 vCE = Vsat , iC < β iB For Si, VD 0 = 0.7 V, Vsat = 0.2 V F. Najmabadi, ECE65, Winter 2012 iC = 0 PNP transistor is the analog to NPN BJT PNP transistor “Linear” model Cut-off : EB is reverse biased Active: EB is forward biased CB is reverse biased (Deep) Saturation: Compared to a NPN: 1) Current directions are reversed 2) Voltage subscripts “switched” F. Najmabadi, ECE65, Winter 2012 EB is forward biased CB is reverse biased iB = 0, iC = 0 vEB < VD 0 vEB = VD 0 , iB ≥ 0 iC = β iB , vEC ≥ VD 0 vEB = VD 0 , iB ≥ 0 vEC = Vsat , iC < β iB Notations Resistors: Use “subscript” of BJT terminal: RC , RB , RE . F. Najmabadi, ECE65, Winter 2012 DC voltages: Use “Double subscript” of BJT terminal: VCC , VBB , VEE . Voltage sources are identified by node voltage! Transistor operates like a “valve:” iC & vCE are controlled by iB Controlled part: iC & vCE are set by transistor state (& outside circuit) Controller part: Circuit connected to BE sets iB Cut-off (iB = 0): Valve Closed Active (iB > 0): Valve partially open iC = β iB Saturation (iB > 0): Valve open F. Najmabadi, ECE65, Winter 2012 iC = 0 iC < β iB iC limited by circuit connected to CE terminals, increasing iB does not increase iC Recipe for solving BJT circuits (State of BJT is unknown before solving the circuit) 1. Write down BE-KVL and CE-KVL: 2. Assume BJT is OFF, Use BE-KVL to check: a. b. 3. BJT OFF: Set iC = 0, use CE-KVL to find vCE (Done!) BJT ON: Compute iB Assume BJT in active. Set iC = β iB . Use CE-KVL to find vCE . If vCE ≥ VD0 , Assumption Correct, otherwise in saturation: 4. BJT in Saturation. Set vCE = Vsat . Use CE-KVL to find iC . (Double-check iC < β iB ) NOTE: o For circuits with RE , both BE-KVL & CE-KVL have to be solved simultaneously. F. Najmabadi, ECE65, Winter 2012 Example 1: Compute transistor parameters (Si BJT with β = 100). BE - KVL : 4 = 40 × 103 iB + vBE CE - KVL : 12 = 103 iC + vCE Assume Cut - off : iB = 0 and vBE < VD 0 = 0.7 V BE - KVL : 4 = 40 × 103 × 0 + vBE → vBE = 4 V vBE = 4 V > VD 0 = 0.7 V → Assumption incorrect BE ON : vBE = VD 0 = 0.7 V and iB ≥ 0 BE - KVL : 4 = 40 × 103 × iB + 0.7 → iB = 8.25 µ A > 0 Assume Active : iC = β iB and vCE ≥ VD 0 = 0.7 V iC = β iB = 100 × 8.25 × 10 −6 = 8.25 mA CE - KVL : 12 = 103 × 8.25 × 10 −3 + vCE → vCE = 3.75 V vCE = 3.75 V > VD 0 = 0.7 V → Assumption correct F. Najmabadi, ECE65, Winter 2012 BJT Transfer Function (1) BE - KVL : vi = RB iB + vBE CE - KVL : VCC = RC iC + vCE Cut - off : iB = 0 and vBE < VD 0 BE - KVL : vi = RB × 0 + vBE → vBE = vi iC = 0 CE - KVL : VCC = RC × 0 + vCE → vCE = VCC For vi < VD 0 → BJT in Cutoff iB = 0, iC = 0, vCE = VCC BE ON : vBE = VD 0 and iB ≥ 0 BE - KVL : vi = RB × iB + VD 0 → iB = F. Najmabadi, ECE65, Winter 2012 iB ≥ 0 → vi ≥ VD 0 vi − VD 0 RB BJT Transfer Function (2) BE ON : vBE = VD 0 and iB = vi − VD 0 RB CE - KVL : VCC = RC iC + vCE Active : iC = β × ic = β iB and vCE ≥ VD 0 vi − VD 0 RB CE - KVL : VCC = RC iC + vCE → vCE = VCC - RC iC vCE ≥ VD 0 → vi ≤ VD 0 + VCC − VD 0 βRC / RB For VD 0 ≤ vi ≤ VD 0 + F. Najmabadi, ECE65, Winter 2012 VCC − VD 0 → BJT in active βRC / RB BJT Transfer Function (3) vi − VD 0 RB BE ON : vBE = VD 0 and iB = CE - KVL : VCC = RC iC + vCE Saturaation : vCE = Vsat and ic < β iB CE - KVL : VCC = RC iC + Vsat → iC = ic < β iB → vi > VIH = VD 0 + For VD 0 + VCC - Vsat RC VCC − Vsat βRC / RB VCC − VD 0 < vi → BJT in saturation βRC / RB F. Najmabadi, ECE65, Winter 2012 BJT Transfer Function (4) vi < VD 0 VD 0 ≤ vi ≤ VD 0 + VD 0 + → BJT in Cutoff VCC − VD 0 βRC / RB VCC − Vsat < vi βRC / RB F. Najmabadi, ECE65, Winter 2012 → BJT in active → BJT in deep saturation BJT transfer function on the load line Saturation : VIH < vi iB increases but iC unchanged Load Line (CE - KVL) vCE = VCC − RC iC Active : VD 0 ≤ vi ≤ VIH iB & iC increase together F. Najmabadi, ECE65, Winter 2012 Cut − off : vi < VD 0 BJT as a switch Load is placed in collector circuit Use: Logic gate can turn loads ON (BJT in saturation) or OFF (BJT in cut-off) ic is uniquely set by CE circuit (as vce = Vsat) RB is chosen such that BJT is in deep saturation with a wide margin (e.g., iB = 0.2 ic /β) F. Najmabadi, ECE65, Winter 2012 *Lab 4 circuit Solved in Lecture notes (problems 12 & 13) BJT as a Digital Gate Resistor-Transistor logic (RTL) RTL NOT gate (VL = Vsat , VH = VCC) RTL NOR gate* RTL NAND gate* Other variants: Diode-transistor logic (DTL) and transistor-transistor logic (TTL) BJT logic gates are not used anymore except for high-speed emitter-coupled logic circuits o Low speed (switching to saturation is quite slow). o Large space and power requirements on ICs F. Najmabadi, ECE65, Winter 2012 *Solved in Lecture notes (problems 14 & 15) BJT β varies substantially Our BJT model includes three parameters: VD0 , Vsat and β o VD0 and Vsat depend on base semiconductor: o For Si, VD0 = 0.7 V, Vsat = 0.2 V Transistor β depends on many factors: o Strongly depends on temperature (9% increase per oC) o Depends on iC (not constant as assumed in the model) o β of similarly manufactured BJT can vary (manufacturer spec sheet typically gives a range as well as an average value for β ) o We will use the average β in calculations (PSpice also uses average β but includes temperature and iC dependence). o βmin is an important parameter. For example, to ensure operation in deep saturation for all similar model BJTs, we need to set iC /iB < βmin F. Najmabadi, ECE65, Winter 2012