Chapter 5 Designing Combinational Systems

advertisement

Chapter 5

Designing

Combinational

Systems

Tell me what you

•Have in

•Have out

•And want done in between

Then I can build a program

to do anything.

Capt. Ed Fischel, USAF

When an input to gate changes

There is a small delay, ∆t

Consider three inputs to Nand gates

1. Input C changes,

Then Out F changes a little later ∆t

2. In A changes,

Connection X changes a little later ∆t

Then Out F changes 2∆t later

3. In C changes, no effect

4. In B changes,

Connection X changes ∆t

5.In B changes,

Causes X to change ∆t

At same time as B, C changes

Which changes out F ∆t

Then X changes out F 2 ∆t

Called a glitch or hazard

Each gate causes a delay ∆

Each sequential causes another ∆

An adder has 6 shifts ∆

A 4 bit has 4 * 6 = 24 ∆

Can be real impact

N-bit adder = n 1-bit adders

Called a carry-ripple adder

For adder, can build truth table

For subtractor can build truth table

Generally if need subtractor, will want both.

Use trick learned in Ch. 1

Complement each bit of subtrahend,

Then add 1

Use control line a’/s

When = 1 do subtraction

Note

1 (+) x = x’

0 (+) x = x

Use XOR for each bit

Compare two numbers

XOR

w/ inputs unequal XOR=1

w/ inputs equal

XOR=0

Inputs

a’b= , ab’=

Since this is binary,

That represents all possible

Combinations.

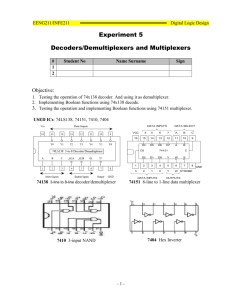

DECODER

Select one of several outputs from coded input

Convert binary input to individual outputs

Each out corresponds to a number

Active hi

Output =1 when condition is active

Active lo

Output =0when condition is active

Enable is a control line

It is another input to the AND gate

Generally shown at bottom

EN’ is active low

When en’ = 0, the decoder works

When en’ = 1, the decoder is off

Commercial

Note order of inputs – CBA where C is hi order bit

Previous models – ABC where A is high order bit

Range 0-7

Multiple select lines

En1 = 1, En2’ = 0, En3’ =0

Otherwise all outputs are inactive =1

3 select lines allow selection of up to 8 devices

Suppose want to select 1 of 32 devices

Use four decoders

Need 2 control lines to select

Which of 4 decoders

Use ab

Need 3 data lines for CBA inputs

Use cde

String would be abcde

1st

2nd

3rd

4th

decoder select

decoder select

decoder select

decoder select

a=0

a=0

a=1

a=1

b=0

b=1

b=0

b=1

4th decoder will need inverter

There is only one active hi enable

Decoder is easy way to implement a logic function

Consider 2 functions

F = Σ(0,2,3,7)

G= Σ(1,4,6,7)

Range 0-7, need 3 inputs, 2↑3 = 8

Using active hi, connect out thru OR

Using active lo, connect out thru NAND

Active lo,

invert out of decoder & In of OR

Invert-OR is a NAND

EX 5.4

Implement 3 different functions

Use 1 of 4 device as select

Use four 1 of 4 decoders

Input string abcd

Notice value of output

at each decoder

Since it is active lo,

NAND outputs

NAND = invert-OR

Select goes to

decoders

and to output NAND

5.3 Encoders

Inverse of decoder

Input line value is weighted

Only one line active

Has a binary value

A0

A1

A2

A3

Z0

Z1

1

0

0

0

0

0

0

1

0

0

0

1

0

0

1

0

1

0

0

0

0

1

1

1

If more than one input can be active, must establish priority

In table no. 7 is highest priority. Ignore any input that is less.

NR is no request. That is necessary to differentiate for

0 input and no input.

5.4 Multiplexer

A switch that passes one of inputs to the ouput, based on select lines

Four inputs, w, x, y, z

Can build 4-way from two 2-way

Two select S1, S0

Output = w, if S0 = 0

Output = x, if S1 = 1

Ex 5.5

A 3 variable function can be build directly from 8-way mux

Look at truth table

Use inputs as select lines, place function value on mux in

Could do same thing with a 4:1 mux

Rearrange truth table.

To now have assumed all values are 0 or 1

Tri-state has a hi=z state, which appears as no device

If device is disabled, then function has no connection

Bus – set of lines that carry data

May be bi-directional

Built using tri-state mux

If use SOP, requires 2-wires

5.6 Now to large implementation

Programmable Logic Device

Gate arrays

ROM

PLA

PAL

This is very simple version

3-in, 3-out

Many possible connections

Implement SOP expressions

Only requires uncomplemented

input

Complement built-in

5.6 PLD

F=a’b’ + abc

G=a’b’c’ + ab + bc

H = a’b’ + c

Solid line shows implementation

Dot show connection

This is too messy

Generally do not show

dashed lines

Use software to set up

Program the device in a burner.

PLA – specifies all connections

for AND and OR, most general

ROM – AND array fixed

specify OR

just a decoder

PAL – determine AND gate inputs

5.6.1 ROM design

4-in, 3-out

Only need minterm value

W(A, B, C, D) = ∑m(3, 7, 8, 9, 11, 15)

X(A, B, C, D) = ∑m(3, 4, 5, 7, 10, 14, 15)

Y(A, B, C, D) = ∑m(1, 5, 7, 11, 15)

Note matrix looks like truth table

One AND gate for each minterm

Burn connection for the OR out

Called a memory device

Just another combinational logic

5.6.2 PLA design

Need to find SOP expressions

Use k-map, QM

Same function, but reduce to SOP

W = AB´C´ + A´CD + ACD

X = A´BC´ + ACD´ + A´CD + BCD

Y = A´C´D´ + ACD + BCD

Limitation-# of AND

Illustration shows

2 possible solutions

for wxy

W(A, B, C, D) = ∑m(3, 7, 8, 9, 11, 15)

X(A, B, C, D) = ∑m(3, 4, 5, 7, 10, 14, 15)

Y(A, B, C, D) = ∑m(1, 5, 7, 11, 15)

5.6.3 Programmable Array Logic

Each out from an OR

that has own group of ANDs

No sharing of terms

Often have some

feedback from

Out back to input

Often tri-state

Programmable Array Logic

Same example

W = AB´C´ + CD

Y = A´BC´ + A´CD + ACD´ + {BCD or ABC}

Z = A´C´D´ + ACD + {A´BD or BCD}

Use software to set-up

One version is VeriLog

Then burn the chip in a programmer

5.8.2 7-Seg

Complex, large system

4-in, 7-out

6,7,9 have alternative design, DC

4-in gives 16 possible out

Actually only 10 numbers 0-9

Remaining options, DC

7-seg

Create K-map for each output

Determine output equation

From list of equations

Create table of PI

Mark X if the minterm is used

7-Seg

Another implementation

Use maximum sharing

Same process

Use k-Map or QM

7-Seg

Maximum sharing

Granted

both techniques

very involved

Tedious

a = X´Y´Z´ + WX´Y´ + W´XY´Z + W´YZ + W´X´Y´

b = W´YZ + W´X´Y + W´Y´Z´ + X´Y´

c = W´YZ + X´Y´ + W´X

d = X´Y´Z + W´XY´Z + W´X´Y + W´YZ´

e = X´Y´Z´ + W´YZ´

f = WX´Y´ + W´Y´Z´ + W´X

g = WX´Y´ + W´X´Y + W´YZ´ + W´XY´

7-Seg

Easy way out

PLA here

Need SOP

7-Seg

Easiest way

ROM

Need minterms only

Note matrix

It is truth table

Chapter

Software

Programs provided by vendors of PLD

Specific to device

Error coding

Data transmitted or stored can create errors

Hamming add a single bit to detect error

Parity Bit is 1 0r 0 so that total number of 1’s is even.

One error will cause a change and the parity will not match.

Exor the bits to check. If result is 0, then assume correct.

ROM Other uses

Since a ROM will have an output based on the status of the address lines, it can be used to

represent a conventional logic network. There are ‘n’ outputs and each output can have 2m

maxterms.

The ROM has fixed values, which makes it well suited for projects that require a table lookup.

This is particularly appropriate for mathematics problems that are repeated frequently.

Consider an example.

Given: y = 2 x2 – 1

Allowable range: 0 x 3

What is the address (input) variable?

x

What is the data (output) variable?

y

How many addresses are there?

4 (0, 1, 2, 3)

m

How many address lines are required? m = 2 2 = 4

What is the largest value output?

17

n

How many output lines are required?

n = 5 2 = 32

Create a table of values to implement the function. Negative values are represented by setting

the most significant bit (MSB) to 1. Decimal numbers can also be represented by setting another

bit.

By connecting switches to the address lines and LED’s to the output lines, the special purpose

calculator is realized.

Input

Address lines

0

1

2

3

00

01

10

11

Memory

-1

1

7

17

Output

lines

100001

00001

00111

10001

Chapter 5

Designing Combinational circuits

AND, OR , NOT

Decoder

Encoder

Multiplexer

PLDPLA

PAL

ROM

Good stuff for building most circuits.

Next Chapter look at Sequential

Means has feedback & memory