Solar Cell Fundamentals Lab Lecture 5C Phosphorus doping with spin on revised 9-15-2014

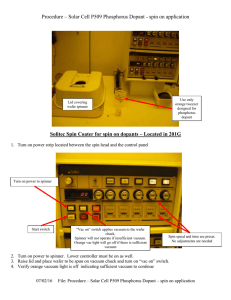

advertisement

I have seen this happen ! You have exceeded your storage allocation Creating a n-p junction on a p-type silicon wafer A n-p junction is a diode and a solar cell It can also be the start of a n-p-n bipolar transistor or a FET transistor Starting with a n-type wafer would create a p-n junction When creating a doped junction in silicon There are two situations • Using a limited source • Using a infinite source Each situation has a different mathematical calculation to determine diffusion depth With an infinite source, the dopant is constantly supplied Example – phosphorus gas continually supplied P P P P P P P P P P P P P P P P P P P P P P P P P P P P P Clean silicon wafer P-type With an limited source, the dopant has a fixed amount available Example – spin on phosphorus film P P P P P P P P P P Clean silicon wafer P-type P P For the solar cell being fabricated for this lab The following will apply Start with a clean p-type silicon wafer Clean silicon wafer P-type A SiO2 layer is deposited via PECVD on the backside to prevent backside doping Clean silicon wafer P-type Backside SiO2 Using a liquid n-type phosphorus spin on dopant, a layer of phosphorus is left on the surface Spin on phosphorus (n) dopant Clean silicon wafer P - type Backside SiO2 To avoid contamination, a separate spinner is used for the spin on dopants Spin at 3 KRPM for 20 seconds. Spin is preset for correct conditions Wafer held with vacuum. Vacuum switch is located on control panel This spinner is located in the yellow room closest to the garment change out room Liquid dopants are located in the dry box. Use P509 and always check the expiration date Use P509 – expiration date 1-30-2012 High temperature tube furnace for 9500C diffusion Furnace #6 is for phosphorus doping only. Do not cross contaminate apparatus and tweezers. Verify correct temperature before using 0 950 C After diffusion @ a n-region is created in the silicon. Time and temperature determine the depth of the n doped region n doped silicon -------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------- P doped silicon Backside SiO2 An HF etch removes any residual phosphorus on the surface and the backside SiO2 n doped ------------------------------------------------------------------------------------------------------------------------------------------------- P-doped A n/p junction has been formed n doped ------------------------------------------------------------------------------------------------------------------------------------------------- P-doped Solid phosphorus sources are available Liquid POCl3 with a nitrogen carrier gas is also used as a phosphorus dopant. POCl3 will form HCl on exposure to moist air or water ! Nitrogen carrier gas in To high temperature furnace tube Constant temperature cooler (200C) A photo-mask will need to be created using AutoCAD Due to the current limitations on the tester in the clean room, cell size is limited to a maximum of 10 cm2 Current solar light simulator in Cameron clean room with Keithley 4200 I/V tester @ 1 amp max Example of a photo-mask transparency AutoCAD dimension drawing must be submitted for approval • Dimension Drawing is due in 2 weeks • Any pattern for top side conductor is acceptable. Multiple top side conductor patterns preferred • Cell size can vary from 2 cm2 to 10cm2 • Patterns must be in-line to cut with the dicing saw A new solar cell tester will be available in EPIC with higher current capability (10 amp) The new tester will provide the capability to test standard size industrial cells 125mm x 125mm cell