Title: A Numerical Study of the Thermal

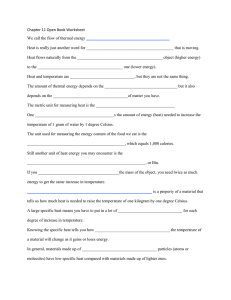

advertisement