ppt - University of California, Santa Barbara

advertisement

Short Course, 2009 Conference on InP and Related Materials, Newport Beach, CA, May 10-14

Scaling of

High Frequency III-V Transistors

Mark Rodwell

University of California, Santa Barbara

rodwell@ece.ucsb.edu 805-893-3244, 805-893-5705 fax

THz Transistors

Transistor bandwidths are increasing rapidly.

Si MOSFETs will soon reach 500+ GHz cutoff frequencies.

It is now clear III-V bipolar transistors can reach ~2-3 THz

cutoff frequencies.

III-V FETs have comparable potential, but the prospects and

analysis are less clear.

The limits to transistor bandwidth are:

contact resistivities

gate dielectric capacitance densities.

device and IC power density & thermal resistance.

challenges in reliably fabricating small devices.

Why

THz Transistors ?

Why Build THz Transistors ?

500 GHz digital logic

→ fiber optics

THz amplifiers→ THz radios

→ imaging, sensing,

communications

precision analog design

at microwave frequencies

→ high-performance receivers

Higher-Resolution

Microwave ADCs, DACs,

DDSs

Performance

Figures of Merit

Transistor figures of Merit / Cutoff Frequencies

gains, dB

H21=short-circuit current gain

MAG = maximum available

power gain:

impedance-matched

fmax

power-gain

cutoff frequency

ft

current-gain

cutoff frequency

U= unilateral power gain:

feedback nulled,

impedance-matched

What Determines Gate Delay ?

Gate Delay Det ermined by :

Depleti on capacitanc e charging

through the logic swing

VLOGIC

Ccb Cbe,depletion

I

C

Depleti on capacitanc e charging

through the base resistance

Rbb Ccbi Cbe,depletion

Supplying base collector

stored charge

through the base resistance

IC

Rbb t b t c

V

LOGIC

The logic swing must be at least

kT

VLOGIC 4

Rex I c

q

(t b t c ) typicall y 10 - 25% of total delay;

Delay not well correlated with ft

VLOGIC

I C Ccb Cbe,depl is 55% - 80% of total.

High I C / Ccb is a key HBT design objective.

J max, Kirk 2εvelectron(Vce , operating Vce ,full depletion ) / Tc2

Acollector TC

A

2

v

emitter electron

Rex must be very low for low Vlogic at high J

Ccb VLOGIC VLOGIC

IC

2VCE ,min

HBT Design For Digital & Mixed-Signal Performance

from charge-control analysis:

Tgate ( VL / I C )( C je 6Ccbx 6Ccbi ) t f

( kT / qI C )( 0.5C je Ccbx Ccbi 0.5t f I C / VL )

Rex ( 0.5Ccbx 0.5Ccbi 0.5t f I C / VL )

Rbb( 0.5C je Ccbi 0.5t f I C / VL ).

analog ICs have similar bandwidth constraints...

High-Frequency

Electron Device

Design

Simple Device Physics: Resistance

bulk resistance

R

bulk T

A

contact resistance

-perpendicular

R

contact

A

contact resistance

- parallel

R

contact

A

W'

sheet

3L

Good approximation for contact

widths less than 2 transfer lengths.

Simple Device Physics: Depletion Layers

capacitance

A

C

T

transit time

T

t

2v

space-charge

limited current

I max 2v

2 Vapplied Vdepletion 2

A

T

V

C

t

I C

where

T

I max Vapplied Vdepletion 2

Simple Device Physics: Thermal Resistance

Exact

Carslaw & Jaeger 1959

Long, Narrow Stripe

HBT Emitter, FET Gate

1

1

L

Rth

ln

Kth L W Kth L

cylindrica l heat flow

near junction

spherical heat flow

far from junction

Square ( L by L )

IC on heat sink

1

L

Rth

sinh 1

K th L

W

1

W

sinh 1

K thW

L

Rth

1

1

4 K th L K th L

planar heat flow spherical heat flow

near surface

far from surface

Simple Device Physics: Fringing Capacitance

C

W

1 .5

L

T

parallel - plate

fringing

wiring capacitance

C/L

VLSI power-delay limits

slowly - varying function

C

of

W

/

G

and

W

/

G

L

1

2

(1 to 3)

FET parasitic capacitances

C parasitic / L ~

FET scaling constraints

Electron Plasma Resonance: Not a Dominant Limit

T 1

Lkinetic

A q 2nm*

T

1

Rbulk

A q 2nm*t m

dielectric relaxation frequency scattering frequency

1 Rbulk

1 / 2

f dielecic

f dielecic

2 Lkinetic

Cdisplacement Rbulk

1

1

2tm

2

n - InGaAs

3.5 10 / cm

19

p - InGaAs

7 10 / cm

19

3

Cdisplacement

A

T

plasma frequency

1 / 2

f plasma

LkineticCdisplacement

800 THz

7 THz

74 THz

80 THz

12 THz

31 THz

3

Electron Plasma Resonance: Not a Dominant Limit

T 1

Lkinetic

A q 2nm*

T

1

Rbulk

A q 2nm*t m

dielectric relaxation frequency scattering frequency

1 Rbulk

1 / 2

f dielecic

f dielecic

2 Lkinetic

Cdisplacement Rbulk

1

1

2tm

2

n - InGaAs

3.5 10 / cm

19

p - InGaAs

7 10 / cm

19

3

Cdisplacement

A

T

plasma frequency

1 / 2

f plasma

LkineticCdisplacement

800 THz

7 THz

74 THz

80 THz

12 THz

31 THz

3

Electron Plasma Resonance: Not a Dominant Limit

T 1

Lkinetic

A q 2nm*

T

1

Rbulk

A q 2nm*t m

dielectric relaxation frequency scattering frequency

1 Rbulk

1 / 2

f dielecic

f dielecic

2 Lkinetic

Cdisplacement Rbulk

1

1

2tm

2

n - InGaAs

3.5 10 / cm

19

p - InGaAs

7 10 / cm

19

3

Cdisplacement

A

T

plasma frequency

1 / 2

f plasma

LkineticCdisplacement

800 THz

7 THz

74 THz

80 THz

12 THz

31 THz

3

Electron Plasma Resonance: Not a Dominant Limit

T 1

Lkinetic

A q 2nm*

T

1

Rbulk

A q 2nm*t m

dielectric relaxation frequency scattering frequency

1 Rbulk

1 / 2

f dielecic

f dielecic

2 Lkinetic

Cdisplacement Rbulk

1

1

2tm

2

n - InGaAs

3.5 10 / cm

19

p - InGaAs

7 10 / cm

19

3

Cdisplacement

A

T

plasma frequency

1 / 2

f plasma

LkineticCdisplacement

800 THz

7 THz

74 THz

80 THz

12 THz

31 THz

3

Frequency Limits

and Scaling Laws

of (most)

Electron Devices

t thickness

C area / thickness

Rtop contact / area

Rbottom

contact

area

PIN photodiode

Rtop

Rbottom

sheet width

4

length

I max, space-charge-limit area / thickness

2

power

length

T

log

length

width

To double bandwidth,

reduce thicknesses 2:1

Improve contacts 4:1

reduce width 4:1, keep constant length

increase current density 4:1

Bipolar Transistor Scaling Laws

We

Tb

Changes required to double transistor bandwidth:

parameter

collector depletion layer thickness

base thickness

emitter junction width

collector junction width

emitter contact resistance

current density

base contact resistivity

emitter

Wbc

Tc

length LE

change

decrease 2:1

decrease

1.414:1

decrease 4:1

decrease 4:1

decrease 4:1

increase 4:1

decrease 4:1

Linewidths scale as the inverse square of bandwidth because thermal constraints dominate.

FET Scaling Laws

LG

gate width WG

Changes required to double transistor bandwidth:

parameter

gate length

gate dielectric capacitance density

gate dielectric equivalent thickness

channel electron density

source & drain contact resistance

current density (mA/mm)

change

decrease 2:1

increase 2:1

decrease 2:1

increase 2:1

decrease 4:1

increase 2:1

Linewidths scale as the inverse of bandwidth because fringing capacitance does not scale.

THz & nm Transistors: it's all about the interfaces

Metal-semiconductor interfaces (Ohmic contacts):

very low resistivity

Dielectric-semiconductor interfaces (Gate dielectrics):

very high capacitance density

Transistor & IC thermal resistivity.

Bipolar

Transistors

Indium Phosphide Heterojunction Bipolar Transistors

Z. Griffith

E. Lind

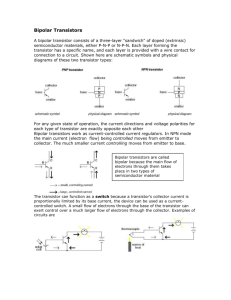

Bipolar Transistor Operation

Vbe

Vce

Ic

Because emitter energy distributi on is thermal (exponenti al)

I c exp( qVbe / kT )

Almost all electrons reaching base pass through it

I c varies little with collector voltage

Transistor Hybrid-Pi equivalent circuit model

Rbe / gm

gm qI E / nkT

Cbe C je g m (t b t c )

Cutoff frequencies in HBTs

kT

1

kT

t base t collector C je

Cbc

Rex Rcoll

2ft

qI E

qI E

t base Tb2 2 Dn

f max

ft

8RbbCcbi

t collector Tc 2veff

Epitaxial Layer

Structure

Epitaxy: InP Emitter, InGaAs Base, InP Collector, Both Junctions Graded

M. Dahlstrom

Z. Griffith UCSB

Key Features:

M. Urteaga

TSC

N++ InGaAs emitter contact layer

emitter

InP emitter

graded

base

InGaAs/InAlAs superlattice e/b grade

collector

subcollector

emitter

cap

InGaAs graded base

bandgap or doping grade

BC setback layer

Layer

Material

Doping

Thickness (nm)

Emitter cap

In0.53Ga0.47As

8 1019 cm-3: Si

25

N emitter

InP

8 10 cm : Si

50

N- emitter

InP

1 1018 cm-3: Si

20

In0.53Ga0.47As / In0.52Al0.48As,

1.6 nm period

In0.53Ga0.47As / In0.52Al0.48As,

1.5 nm period

N: 1 1017 cm-3: Si

24

P: 8 1017 cm-3: C

1

Base

In0.53Ga0.47As

P: 7-4 1019 cm-3: C

24.5

Setback

In0.53Ga0.47As

N: 9 1016 cm-3: Si

4.5

Base-collector

grade

In0.53Ga0.47As / In0.52Al0.48As,

1.6 nm period

N: 9 1016 cm-3: Si

15

Pulse doping

InP

6 1018 cm-3: Si

3

Collector

InP

N: 2 1016 cm-3: Si

82

etch-stop

In0.53Ga0.47As

19

N: 8 10 cm : Si

5

Subcollector

InP

N: 8 1019 cm-3: Si

~200

+

InGaAs/InAlAs superlattice b/c grade

Emitter-base grade

InP collector

InGaAs etch-stop layer

thin for heat conduction

InP subcollector

Emitter-base grade

19

-3

-3

M. Dahlstrom

Z. Griffith

E. Lind

Epitaxy with Abrupt BE Junction

Similar design

emitter

Abrupt E/B junction (no e/b grade)

graded

base

Advantages:

ease of stopping emitter etch on base

→ good base contacts

Disadvantages:

Increased Vbe .

Cannot make e/b ledge.

collector

subcollector

emitter

cap

Layer

Material

Doping

Thickness (nm)

Emitter cap

In0.53Ga0.47As

8 1019 cm-3: Si

25

InP

8 10 cm : Si

50

N emitter

InP

1 10 cm : Si

20

N- emitter

InP

N: 1 1017 cm-3: Si

24

Emitter-base grade

In0.53Ga0.47As / In0.52Al0.48As,

1.5 nm period

P: 8 1017 cm : C

1

Base

In0.53Ga0.47As

P: 7-4 1019 cm-3: C

24.5

Setback

In0.53Ga0.47As

N: 9 10 cm : Si

4.5

Base-collector

grade

In0.53Ga0.47As / In0.52Al0.48As,

1.6 nm period

N: 9 1016 cm-3: Si

15

Pulse doping

InP

6 1018 cm : Si

3

Collector

InP

N: 2 1016 cm-3: Si

82

In0.53Ga0.47As

19

-3

N: 8 10 cm : Si

5

InP

19

-3

~200

+

N emitter

-

etch-stop

Subcollector

19

18

-3

-3

-3

-3

16

-3

N: 8 10 cm : Si

Alternative Grades for Thinner Epitaxy

Common Grade in Literature

InGaAs/InAlAs

18 nm thick, 1.5 nm period

Sub-monolayer Grade

0.15 nm InAlAs,

(0.15 to 0.165 nm InGaAs)

10.8 nm thick

Strained InxGa1-xAs Grade

InGaAs/GaAs 6 nm

E . Lind

Z. Griffith

Other Methods of Grading the Junctions

InGaAs/InGaAsP/InP grade

InP/GaAsSb/InP DHBT

IEDM 2001

-suitable for MOCVD growth

- does not need B/C grading

- excellent results

- E/B band alignment through

GaAsSb alloy ratio (strain)

or InAlAs emitter

Transport Analysis

Approximate Carrier Transit Times

We

Tb

Base Transit Time

t b Tb2 2 Dn Tb vexit

Collector Transit Time

t c Tc 2v sat

emitter

Wbc

Tc

length LE

Base Transit Time with Graded Base

Dino Mensa

Assumes :

DN 40 cm 2 / V sec

vexit 3 107 cm/s

Drift - diffusion model correct if

τ b t m Dn m* / kT 35 fs

t b Wb Lg / Dn L / Dn Lg / vsat 1 e

2

g

where Lg is the grading length :

Lg Wb kT / E g

Wb / Lg

Base Transit Time: Grading Approaches

Compositional grading:

strained graded InGaAs base

52 meV potential drop :

In 0.455Ga 0.545As In 0.53Ga 0.47As (strained)

Doping grading

unstrained In0.53Ga0.47As base

Carbon doping varied from :

~ 8 1019 /cm 3 to ~ 5 1019 /cm 3

Dino Mensa

Miguel Urteaga

Mattias Dahlström

T. Ishibashi

Collector Transit Time

From elementary electrosta tics (refer to sketch)

tc

(1 x / Tc )

Tc

dx

0 v( x)

2veff

TC

t c is more sensitive to velocity near base.

Fortuitous , as initial velocity is high,

then decreases due to - L scattering .

From best fit to RF data, or from Kirk current density vs . collector voltage :

InP : 3.5 107 cm/s for ~ 70 - 200 nm layers

Space-Charge Limited Current Density → Ccb charging time

Collector Depletion Layer Collapse

Vcb,min (qN d )(Tc2 / 2 )

Collector Field Collapse (Kirk Effect)

Vcb ( J / vsat qN d )(Tc2 / 2 )

J max 2veff (Vcb Vcb,min 2 ) / Tc2

Note that Vbe , hence (Vcb ) Vce

Ccb VLOGIC / I C Acollector Tc VLOGIC

VLOGIC Acollector TC

IC

VCE VCE,min Aemitter 2veff

Collector capacitance charging time scales linearly with collector thickness if J = Jmax

Space-Charge-Limited Current (Kirk effect) in DHBTs

500

0.6 V

cb

0.0 V

2vsat (Vce Vce ,min ) / Tc2

cb

-0.2 V

300

cb

f , -0.3 V

t

200

J max 2vsat (Vcb Vcb ,min 2 ) / Tc2

0.2 V

cb

t

Kirk - effect thr eshold increases

with increased Vce

400

f (GHz)

Decrease in ft and f max at high J

100

0

2

cb

4

6

8

2

J (mA/um )

10

12

e

I

b step

= 180 uA

40

35

12

30

10

25

Peak f , f

8

t

max

20

6

15

4

10

2

5

0

0

0

0.5

1

1.5

V

ce

(V)

2

2.5

c

where the effective collector

current flux area is

Aeffective LE WE 2TC

cb

I (mA)

dVce

T

Rspacecharge

dI c

2vsat Aeffective

V =0V

2

2

c

2

14

Je (mA/mm )

Increase in Vce , sat with increased J

A = 0.6 x 4.3 mm

jbe

16

T. Ishibashi

Current-induced Collector Velocity Overshoot

2.5

1.5

ec

tau , ps

2

J=0

300 Å InGaAs base

1

2000 Å InP collector

0.5

280 GHz peak ft

0

0

0.5

1

1.5

2

2.5

2

inverse current density, 1/J,mm /mA

3

3.5

Increased current reduces - L scattering ,

increases v ( x ) in early part of collector

reduced collector transit ti me

(1 x / Tc )

dx is not exactly proportion al to I c

v( x)

0

TC

Qbase I c

J= 8 mA/um2

correct definition of collector transit ti me is

Q

Q

t c base not t c base

I c

Ic

Nakajima, H. "A generalized expression for collector transit time of HBTs

taking account of electron velocity modulation," Japanese Journal of

Applied Physics, vo. 36, Feb. 1997, pp. 667-668

CAUTION : observed nonlinear t ec variation is also in part due to modulation in emitter ideality factor with bias current (1/g m often does not vary as Rex nkT / qI E ), and due to variation of C je with bias.

Transit time Modulation Causes Ccb Modulation

Qbase constant Qbase

holes

Tc

electrons

Ccb

Qbaseholes

Vcb

0 qn( x ) A1 x / Tc dx VbcA / Tc f ( I c ,Vcb )

tf

t

Qbaseholes

C

cb f

I c

I c

Vcb

I b , ΔQba se

ho les

Camnitz and Moll, Betser & Ritter, D. Root

500

Collector Velocity Modulation :

t f Vcb 0 Ccb I c 0

400

-2

300

400

Increase in τ c with Vcb reduced Ccb

- strong effect in InGaAs SHBTs

- weak effect in InP DHBTs

1

cb

0

2

4

6

8

2

J (mA/um )

10

e

12

0

-1

-2

-0.2 V

0

7

100

200

nm

300

400

6

e

200

nm

5

cb

100

t

8

C /A (fF/mm2)

0

2

cb

f , -0.3 V

100

-1

cb

-0.2 V

300

200

0

0.2 V

cb

t

L

0.0 V

eV

eV

1

cb

f (GHz)

2

Kirk Effect :

t f Vcb 0 Ccb I c 0

0.6 V

4

0.0 V

Increase in Ccb is due to both

0.2 V

- base pushout into collector

3

V = 0.6 V

cb

2

0

2.5

5

7.5

J (mA/mm2)

e

10

12.5

- and modulation of τ b by Vcb

Emitter-Base Junction Effects

Voltage drops in

depletion region

Electron degeneracy

contributes 1 - μm2

equivalent series resistance

J(mA/um^2)

Space-charge storage

10

2

10

1

10

0

10

-1

10

-2

10

-3

Rodwell

Lundstrom.

Fermi-Dirac

Boltzmann

-0.3

E fn ( x )

x

J

qmn n( x )

need thin layer &

high electron

density

-0.2

-0.1

V -

0

0.1

0.2

be

Highly degenerate limit

J

need thin layer to avoid

substantial charge storage

delays

Equivalent series

resistance approximation

qm * ( E f Ec ) 2

2 2 3

mA E f Ec

130

2

mm 0.1 eV

for InP emitter ( m*/m0 0.08).

2

RC parasitics

Simple Device Physics: Resistance

bulk resistance

R

bulk T

A

contact resistance

-perpendicular

R

contact

A

contact resistance

- parallel

R

contact

A

W'

sheet

3L

Good approximation for contact

widths less than 2 transfer lengths.

HBT RC Parasitics

base contact width

< 2 transfer lengths

→ simple analysis

Limiting case of

Pulfrey / Vaidyanathan

fmax model.

HBT RC Parasitics

Rex contact,emitter / Aemitter

emitter

length LE

Rspread sWe / 12 LE

Rgap sWgap / 4 LE

Rspread,contact sWbc / 6 LE

Rcontact contact,baseWbc / Abase_ contacts

Ccb ,e Aemitter / Tc

Ccb , gap Agap / Tc

Ccb ,contact Abase_ contacts / Tc

Base-Collector Time Constant & Fmax.

f max

ft

where

8RbbCcbi

t cb RbbCcbi Ccb ,contactRcontact

Ccb , gap ( Rcontact Rspread,contact Rgap / 2)

Ccb ,e ( Rcontact Rspread,contact Rgap Rspread )

Relationship to Equivalent Circuit Model

Ccbx Ccbi Ccb ,e Ccb , gap Ccb ,contact

Rbb Rspread Rgap Rcontact,spread Rcontact

RbbCcbi Ccb,contactRcontact Ccb,gap ( Rcontact Rspread,contact Rgap / 2)

Ccb,e ( Rcontact Rspread,contact Rgap Rspread )

Device Design

Device Scaling

Simple Device Physics: Thermal Resistance

Exact

Carslaw & Jaeger 1959

Long, Narrow Stripe

HBT Emitter, FET Gate

1

1

L

Rth

ln

Kth L W Kth L

cylindrica l heat flow

near junction

spherical heat flow

far from junction

Square ( L by L )

IC on heat sink

1

L

Rth

sinh 1

K th L

W

1

W

sinh 1

K thW

L

Rth

1

1

4 K th L K th L

planar heat flow spherical heat flow

near surface

far from surface

Bipolar Transistor Design

We

Tb

t b T 2 Dn

2

b

Wbc

Tc

t c Tc 2v sat

Ccb Ac /Tc

I c ,max vsat Ae (Vce,operating Vce,punch-through) / T

2

c

P

T

LE

Le

1 ln

We

Rex contact /Ae

We Wbc contact

Rbb sheet

12 Le 6 Le Acontacts

emitter

length LE

Bipolar Transistor Design: Scaling

We

Tb

t b T 2 Dn

2

b

Wbc

Tc

t c Tc 2v sat

Ccb Ac /Tc

I c ,max vsat Ae (Vce,operating Vce,punch-through) / T

2

c

P

T

LE

Le

1 ln

We

Rex contact /Ae

We Wbc contact

Rbb sheet

12 Le 6 Le Acontacts

emitter

length LE

Bipolar Transistor Scaling Laws

We

Tb

Changes required to double transistor bandwidth:

parameter

collector depletion layer thickness

base thickness

emitter junction width

collector junction width

emitter contact resistance

current density

base contact resistivity

emitter

Wbc

Tc

length LE

change

decrease 2:1

decrease

1.414:1

decrease 4:1

decrease 4:1

decrease 4:1

increase 4:1

decrease 4:1

Linewidths scale as the inverse square of bandwidth because thermal constraints dominate.

Thermal Resistance Scaling : Transistor, Substrate, Package

spherical flow

for r Le

cylindrica l heat flow

near junction

Tsubstrate

planar flow

for r DHBT / 2

L

P 1 1

P Tsub D / 2

ln e

K InP LE We K InP LE D K InP

D2

P

increases

logarithmi cally

insignific ant

variation

increases quadratica lly

if Tsub is constant

1 1 Pchip

Tpackage

4 KCuWchip

junction temperature rise, Kelvin

140 Tsub 40 mm (150 GHz / f clock )

120

Wiring lenghts

total

2000 - HBT CML IC

scale as

100

80

1/bandwidt h.

Power density,

substrate: cylindrical+spherical regions

60

package

40

0

100

scales as

substrate: planar region

20

(bandwidth ) 2 .

200

300

400

500

600

master-slave D-Flip-Flop clock frequency, GHz

700

Thermal Resistance Scaling : Transistor, Substrate, Package

spherical flow

for r Le

cylindrica l heat flow

near junction

Tsubstrate

planar flow

for r DHBT / 2

L

P 1 1

P Tsub D / 2

ln e

K InP LE We K InP LE D K InP

D2

P

increases

logarithmi cally

insignific ant

variation

increases quadratica lly

if Tsub is constant

1 1 Pchip

Tpackage

4 KCuWchip

junction temperature rise, Kelvin

140 Tsub 40 mm (150 GHz / f clock )

120

Wiring lenghts

2000 - HBT CML IC

Probable

best solution:

scale as

1/bandwidt h.

Thermal Vias ~500 nm below InP subcollector

Power density,

...over full active IC area.

scales as

total

100

80

substrate: cylindrical+spherical regions

60

package

40

substrate: planar region

20

0

100

(bandwidth ) 2 .

200

300

400

500

600

master-slave D-Flip-Flop clock frequency, GHz

700

InP Bipolar Transistor Scaling Roadmap

industry university university appears

→industry 2007-8

feasible

maybe

emitter 512

16

256

8

128

4

64

2

32 nm width

1 mm2 access

base

300

20

175

10

120

5

60

2.5

30 nm contact width,

1.25 mm2 contact

collector 150

4.5

4.9

106

9

4

75

18

3.3

53

36

2.75

37.5 nm thick,

72 mA/mm2 current density

2-2.5 V, breakdown

520

850

430

240

730

1300

660

330

1000

2000

1000

480

1400 GHz

2800 GHz

1400 GHz

660 GHz

ft

fmax

power amplifiers

digital 2:1 divider

370

490

245

150

We

Tb

Wbc

Tc

Can we make a 1 THz SiGe Bipolar Transistor ?

InP

emitter 64

2

SiGe

18

1.2

nm width

mm2 access

56

1.4

nm contact width,

mm2 contact

collector 53

36

2.75

15

125

???

nm thick

mA/mm2

V, breakdown

ft

fmax

1000

2000

GHz

GHz

Simple physics clearly drives scaling

transit times, Ccb/Ic

→ thinner layers, higher current density

high power density → narrow junctions

base

small junctions→ low resistance contacts

Key challenge: Breakdown

15 nm collector → very low breakdown

(also need better Ohmic contacts)

64

2.5

1000

2000

PAs

1000 1000

GHz

digital 480

480

GHz

(2:1 static divider metric)

Assumes collector junction 3:1 wider than emitter.

Assumes SiGe contacts 2:1 wider than junctions

HBT Design For Digital & Mixed-Signal Performance

from charge-control analysis:

Tgate ( VL / I C )( C je 6Ccbx 6Ccbi ) t f

( kT / qI C )( 0.5C je Ccbx Ccbi 0.5t f I C / VL )

Rex ( 0.5Ccbx 0.5Ccbi 0.5t f I C / VL )

Rbb( 0.5C je Ccbi 0.5t f I C / VL ).

InP HBT: Status

InP DHBTs: September 2008

400 500

GHz GHz

1000

600

GHz

900

GHz

800

GHz

700

GHz

Teledyne DBHT ( ft f max ) / 2

125 nm

UIUC DHBT

800

NTT DBHT

max

(GHz)

250 nm

f

popular metrics :

ft or f max alone

ft f max

ft f max

(1 ft 1 f max ) 1

ETHZ DHBT

600

UIUC SHBT

250 nm

UCSB DHBT

400

NGST DHBT

600nm

HRL DHBT

IBM SiGe

200

350 nm

Vitesse DHBT

0

200

mW/ mm

low noise amplifiers :

Fmin , associated gain,

digital :

f clock , hence

(Ccb V / I c ),

Updated Sept. 2008

0

much better metrics :

power amplifiers :

PAE, associated gain,

400

600

ft (GHz)

800

1000

( Rex I c / V ),

( Rbb I c / V ),

(τb τc )

512 nm InP DHBT

500 nm mesa HBT

150 GHz M/S latches

175 GHz amplifiers

Laboratory

Technology

UCSB / Teledyne / GCS

UCSB

500 nm sidewall HBT

DDS IC: 4500 HBTs

20-40 GHz op-amps

Teledyne

Teledyne / BAE

Teledyne / UCSB

Production

( Teledyne )

Z. Griffith

M. Urteaga

P. Rowell

D. Pierson

B. Brar

V. Paidi

ft = 405 GHz

fmax = 392 GHz

Vbr, ceo = 4 V

20 GHz clock

53-56 dBm OIP3 @ 2 GHz

with 1 W dissipation

40

H

mA/mm2

10

30

dB

256 nm Generation

InP DHBT

150 nm thick collector

U

21

20

fmax = 780 GHz

10

t

10

10

10

11

2

3

4

5

12

11

10

20

21

2

mA/mm

dB

10

max

1

V

U

f

0

12

10

ce

10

10

10

9

10

H

20

4

0

Hz

70 nm thick collector

30

6

2

f = 424 GHz

0

9

10

8

= 560 GHz

15

10

5

f = 560 GHz

t

324 GHz

Amplifier

0

0

9

10

10

10

11

10

0

12

10

1

2

V

Hz

3

4

ce

60 nm thick collector

40

30

H

30

2

U

mA/mm

dB

200 GHz

master-slave

latch design

21

20

10 fmax = 218 GHz

20

10

f = 660 GHz

Z. Griffith, E. Lind

J. Hacker, M. Jones

t

0

9

10

10

10

11

10

Hz

10

12

0

0

1

2

V

ce

3

324 GHz Medium Power Amplifiers in 256 nm HBT

ICs designed by Jon Hacker / Teledyne

Teledyne 256 nm process flow-

Hacker et al, 2008 IEEE MTT-S

Gain (dB), Power (dBm), PAE (%)

20

10

40

Output Power (dBm)

Gain (dB)

Drain Current (mA)

PAE (%)

30

0

20

-10

10

-20

-20

0

-15

-10

-5

Input Power (dBm)

0

5

Current, mA

~2 mW saturated output power

128 / 64 / 32 nm

HBT Technologies

Conventional ex-situ contacts are a mess

THz transistor bandwidths: very low-resistivity contacts are required

textbook contact

with surface oxide

with metal penetration

Interface barrier → resistance

Further intermixing during high-current operation → degradation

Improvements in Ohmic Contacts

128 nm generation requires ~ 4 - μm2 emitter & base resistivities

A.. Crook

V. Jain

A. Barakshar

M. Wistey

U. Singisetti

S. Bank

64 nm generation requires ~ 2 - μm2

Contacts to N-InGaAs*:

Mo

MBE in-situ

2.2 (+/- 0.5) - μm2

TiW

ex-situ / NH4 pre-clean

~2.2 - μm2

variable between process runs

Contacts to P-InGaAs:

Mo

MBE in-situ

below 2.5 - μm2

Pd/Ti...

ex-situ

~4 - μm2

...far better contacts coming...

*measured emitter resistance remains higher than that of contacts.

Mo Emitter Contacts: Robust Integration into Process Flow

Proposed Process Integration:

M. Wistey

A. Barakshar

U. Singisettti

V. Jain

Process Must Change Greatly for 128 / 64 / 32 nm Nodes

control undercut

→ thinner emitter

thinner emitter

→ thinner base metal

Undercutting of emitter ends

{101}A planes: fast

{111}A planes: slow

thinner base metal

→ excess base metal resistance

E. Lind

128 nm Emitter Process: Dry Etched Metal & Semiconductor

a

b

Litho

Cr

pattern

metal

c

SF6/Ar ICP

SiNsidewall

x sidewall

d

e

dry/N

etch

Cl

2 2 ICP

Wetetch

Etch

wet

HCl:H3PO4

BHF

SiO2

TiW

Ti

InGaAs n++

InP n

InP n

InP n

InGaAs p++ Base

InGaAs p++ Base

InGaAs p++ Base

InGaAs p++ Base

20

H

21

10

max

mA/mm

f

2

U

20

dB

10

10

10

9

10

30

InGaAs p++ Base

12

InP n

11

InGaAs n++

10

InGaAs n++

= 560 GHz

15

10

5

f = 560 GHz

t

0

9

10

0

10

10

11

10

Hz

results @ c.a. 200 nm emitter metal width

12

10

0

1

2

V

ce

3

4

Planarization E/B Processes for 64 & 32 nm

Planarization boundary

E; Lobisser

V. Jain

G. Burek

III-V FET Scaling

Simple FET Scaling

Goal double transistor bandwidth when used in any circuit

→ reduce 2:1 all capacitances and all transport delays

→ keep constant all resistances, voltages, currents

All lengths, widths,

thicknesses reduced 2:1

S/D contact resistivity reduced 4:1

C gd / Wg ~

g m / Wg ~ v / Tox

Cgs / Wg ~ Lg / Tox

C gs, f / Wg ~

Csb / Wg ~ Lc / Tsub

If Tox cannot scale with gate length,

Cparasitic / Cgs increases,

gm / Wg does not increase

hence Cparasitic /gm does not scale

FET scaling: Output Conductance & DIBL

( Cgs expression neglects D.O.S. effects)

C gs ~ Wg Lg / Tox

Id Q /t

where

Cd ch ~ Wg

Q CgsVgs Cd chVds

transconductance

output conductance

→ Keep Lg / Tox constant as we scale Lg

FET Scaling Laws

LG

gate width WG

Changes required to double transistor bandwidth:

parameter

gate length

gate dielectric capacitance density

gate dielectric equivalent thickness

channel electron density

source & drain contact resistance

current density (mA/mm)

change

decrease 2:1

increase 2:1

decrease 2:1

increase 2:1

decrease 4:1

increase 2:1

III-V MOSFETs for VLSI

What is it ?

MOSFET with an InGaAs channel

Why do it ?

low electron effective mass→ higher electron velocity

more current, less charge at a given insulator thickness & gate length

very low access resistance

What are the problems ?

low electron effective mass→ constraints on scaling !

must grow high-K on InGaAs, must grow InGaAs on Si

Our focus today is III-V FET scaling generally

Low Effective Mass Impairs Vertical Scaling

Shallow electron distribution needed

for high gm / Gds ratio.

2

* 2

Energy of Lth well state L / m Twell .

For thin wells,

only 1st state can be populated.

For very thin wells,

1st state approaches L-valley.

Only one vertical state in well.

Minimum ~ 5 nm well thickness.

→ constrains gate length scaling.

Density-Of-States Capacitance

E f Ewell ns /( nm* / 2 )

( bidirectio nal motion)

V f Vwell s / cdos

where cdos q 2nm* / 2

and n is the # of band minima

Two implications:

- With Ns >1013/cm2, electrons populate satellite valleys

Fischetti et al, IEDM2007

- Transconductance limited by finite state density

Solomon & Laux , IEDM2001

Drive Current in the Ballistic & Degenerate Limits

mA Vgs Vth

J K 84

mm 1 V

0.25

3/ 2

1/ 2

, where K

0.7 nm, n=6

K

1 (c

*

dos,o / cox ) n ( m / mo )

3/ 2

0.4 nm, n=6

Error bars on Si data

points correct for

(Ef-Ec)>> kT

approximation

0.2

0.15

n m* mo

n = # band minima

cdos,o = density of

states capacitance for

m*=mo & n=1

0.8 nm, n=1

0.1

1.0 nm, n=1

0.05

EOT includes wavefunction depth (0.5 nm for 3.5 nm InGaAs well)

0

0.01

0.1

m*/m

1

o

HEMT Scaling Challenge: Low Gate Barrier

Gate barrier is low: ~0.6 eV

Source

Gate

Drain

K Shinohara

Tunneling through barrier

→ sets minimum thickness

Emission over barrier

→ limits 2D carrier density

Ec

EF

Ec

EF

Ewell-

Ewell-

At N s 1013 / cm2 , ( E f Ec ) ~ 0.6 eV

HEMT Scaling Challenge: High Access Resistance

Gate barrier also lies under source / drain contacts

Source

Gate

Drain

N+ layer

widegap barrier layer

K Shinohara

low leakage:

need high barrier under gate

low resistance:

need low barrier under contacts

Ec

EF

Ec

EF

Ewell-

N+ cap

layer

Ewell-

THz III-V FET Scaling: What Must Be Done

FET Scaling Laws

LG

As gate length is reduced...

channel thickness

should be reduced...

barrier thickness

should be reduced...

gate width WG

Changes required to double transistor bandwidth:

parameter

gate length

gate dielectric capacitance density

gate dielectric equivalent thickness

channel electron density

source & drain contact resistance

current density (mA/mm)

change

decrease 2:1

increase 2:1

decrease 2:1

increase 2:1

decrease 4:1

increase 2:1

target gm/Wg and Id/Wg

should be increased...

source and drain access resistivity should be reduced...

We face serious difficulties in doing these.

A MOSFET Might Scale Better than a HEMT

sidewall

gate dielectric

metal gate

source contact

N+ source

drain contact

quantum well / channel

N+ drain

barrier

substrate

no gate barrier

under S/D contacts

high-K gate

barrier

Overlap between gate

and N+ source/drain

Interconnects

Coplanar Waveguide

No ground vias

No need (???) to thin

substrate

Hard to ground IC

to package

+V

+V

+V

0V

Parasitic microstrip mode

ground plane breaks → loss of ground integrity

-V

0V

substrate mode coupling

or substrate losses

kz

III-V:

semi-insulating substrate→

substrate mode coupling

Silicon

conducting substrate

→ substrate conductivity

losses

+V

0V

Parasitic slot mode

Repairing ground plane with ground straps is effective only in simple ICs

In more complex CPW ICs, ground plane rapidly vanishes

→ common-lead inductance → strong circuit-circuit coupling

poor ground integrity

loss of impedance control

ground bounce

coupling, EMI, oscillation

40 Gb/s differential TWA modulator driver

note CPW lines, fragmented ground plane

35 GHz master-slave latch in CPW

note fragmented ground plane

175 GHz tuned amplifier in CPW

note fragmented ground plane

Classic Substrate Microstrip

W

Zero ground

inductance

in package

Thick Substrate

→ low skin loss

skin

H

1

1/ 2

r

Brass carrier and

assembly ground

IC with backside

ground plane & vias

interconnect

substrate

No ground plane

breaks in IC

H

High via

inductance

12 pH for 100 mm substrate -- 7.5 @ 100 GHz

lines must be

widely spaced

Line spacings must be ~3*(substrate thickness)

near-zero

ground-ground

inductance

TM substrate

mode coupling

kz

Strong coupling when substrate approaches ~ld / 4 thickness

ground vias must be

widely spaced

all factors require very thin substrates for >100 GHz ICs

→ lapping to ~50 mm substrate thickness typical for 100+ GHz

IC vias

eliminate

on-wafer

ground

loops

III-V MIMIC Interconnects -- Thin-Film Microstrip

narrow line spacing → IC density

no substrate radiation, no substrate losses

fewer breaks in ground plane than CPW

... but ground breaks at device placements

InP mm-wave PA (Rockwell)

still have problem with package grounding

...need to flip-chip bond

thin dielectrics → narrow lines

→ high line losses

→ low current capability

→ no high-Zo lines

W

Zo ~

o H

r1/ 2 W H

H

III-V MIMIC Interconnects -- Inverted Thin-Film Microstrip

narrow line spacing → IC density

Some substrate radiation / substrate losses

No breaks in ground plane

... no ground breaks at device placements

still have problem with package grounding

InP 150 GHz master-slave latch

...need to flip-chip bond

thin dielectrics → narrow lines

→ high line losses

→ low current capability

→ no high-Zo lines

InP 8 GHz clock rate delta-sigma ADC

No clean ground return ? → interconnects can't be modeled !

35 GHz static divider

interconnects have no clear local ground return

interconnect inductance is non-local

interconnect inductance has no compact model

8 GHz clock-rate delta-sigma ADC

thin-film microstrip wiring

every interconnect can be modeled as microstrip

some interconnects are terminated in their Zo

some interconnects are not terminated

...but ALL are precisely modeled

InP 8 GHz clock rate delta-sigma ADC

VLSI Interconnects with Ground Integrity & Controlled Zo

narrow line spacing → IC density

no substrate radiation, no substrate losses

negligible breaks in ground plane

negligible ground breaks @ device placements

still have problem with package grounding

...need to flip-chip bond

thin dielectrics → narrow lines

→ high line losses

→ low current capability

→ no high-Zo lines

Conclusions

Few-THz Transistors

Few-THz InP Bipolar Transistors: can it be done ?

Scaling limits: contact resistivities, device and IC thermal resistances.

62 nm (1 THz ft, 1.5 THz fmax ) scaling generation is feasible.

700 GHz amplifiers, 450 GHz digital logic

Is the 32 nm (1 THz amplifiers) generation feasible ?

Few-THz InP Field-Effect Transistors: can it be done?

challenges are gate barrier, vertical scaling,

source/drain access resistance, increased gm and drive current.

2DEG carrier concentrations must increase.

S/D regrowth offers a path to lower access resistance.

Solutions needed for gate barrier: maybe even MOSFET ?

What Would We Do With Them500?GHz digital logic

→ fiber optics

THz amplifiers→ THz radios

→ imaging, sensing,

communications

precision analog design

at microwave frequencies

→ high-performance receivers

Higher-Resolution

Microwave ADCs, DACs,

DDSs