CSE 477. VLSI Systems Design

advertisement

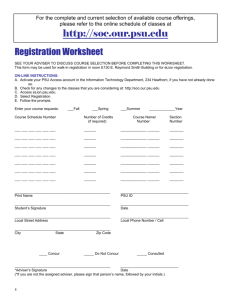

ECE484 VLSI Digital Circuits Fall 2014 Lecture 01: Introduction Adapted from slides provided by Mary Jane Irwin. [Adapted from Rabaey’s Digital Integrated Circuits, ©2002, J. Rabaey et al.] CSE477 L01 Introduction.1 Irwin&Vijay, PSU, 2002 Course Contents Introduction to digital integrated circuits Course goals CMOS devices and manufacturing technology. CMOS logic gates and their layout. Propagation delay, noise margins, and power dissipation. Combinational (e.g., arithmetic) and sequential circuit design. Ability to design and implement CMOS digital circuits and optimize them with respect to different constraints: size (cost), speed, power dissipation, and reliability Course prerequisites ECE 326. Electronic Circuit Design ECE 282. Logic Design of Digital Systems CSE477 L01 Introduction.2 Irwin&Vijay, PSU, 2002 Course Administration Instructor: George L. Engel gengel@siue.edu www.siue.edu/~gengel TA: Geetha Ravi gravi@siue.edu Labs: Need account on ECE machine (see Steve Muren, smuren@siue.edu) Text: Digital Integrated Circuits, 2nd Edition Rabaey et. al., ©2002 CSE477 L01 Introduction.3 Irwin&Vijay, PSU, 2002 Background from ECE282 and ECE326 Basic circuit theory Hardware description language resistance, capacitance, inductance MOS gate characteristics VHDL or verilog Logic design logical minimization, FSMs, component design CSE477 L01 Introduction.4 Irwin&Vijay, PSU, 2002 Transistor Revolution Transistor –Bardeen (Bell Labs) in 1947 Bipolar transistor – Schockley in 1949 First bipolar digital logic gate – Harris in 1956 First monolithic IC – Jack Kilby in 1959 First commercial IC logic gates – Fairchild 1960 TTL – 1962 into the 1990’s ECL – 1974 into the 1980’s CSE477 L01 Introduction.5 Irwin&Vijay, PSU, 2002 MOSFET Technology MOSFET transistor - Lilienfeld (Canada) in 1925 and Heil (England) in 1935 CMOS – 1960’s, but plagued with manufacturing problems PMOS in 1960’s (calculators) NMOS in 1970’s (4004, 8080) – for speed CMOS in 1980’s – preferred MOSFET technology because of power benefits BiCMOS, Gallium-Arsenide, Silicon-Germanium SOI, Copper , … CSE477 L01 Introduction.6 Irwin&Vijay, PSU, 2002 Moore’s Law In 1965, Gordon Moore predicted that the number of transistors that can be integrated on a die would double every 18 to 14 months (i.e., grow exponentially with time). Amazingly visionary – million transistor/chip barrier was crossed in the 1980’s. 2300 transistors, 1 MHz clock (Intel 4004) - 1971 16 Million transistors (Ultra Sparc III) 42 Million, 2 GHz clock (Intel P4) - 2001 140 Million transistor (HP PA-8500) CSE477 L01 Introduction.7 Irwin&Vijay, PSU, 2002 Intel 4004 Microprocessor CSE477 L01 Introduction.8 Irwin&Vijay, PSU, 2002 Intel Pentium (IV) Microprocessor CSE477 L01 Introduction.9 Irwin&Vijay, PSU, 2002 State-of-the Art: Lead Microprocessors CSE477 L01 Introduction.10 Irwin&Vijay, PSU, 2002 Moore’s Law in Microprocessors Transistors on lead microprocessors double every 2 years 1000 2X growth in 1.96 years! Transistors (MT) 100 10 486 1 386 286 0.1 0.01 8086 8080 8008 4004 8085 0.001 1970 CSE477 L01 Introduction.11 P6 Pentium® proc 1980 1990 Year Courtesy, Intel 2000 2010 Irwin&Vijay, PSU, 2002 Evolution in DRAM Chip Capacity human memory human DNA 100000000 10000000 64,000,000 4X growth every 3 years! 16,000,000 Kbit capacity/chip 4,000,000 1000000 1,000,000 book 100000 256,000 64,000 16,000 10000 4,000 1000 1,000 256 100 64 10 1980 0.07 m 0.1 m 0.13 m 0.18-0.25 m 0.35-0.4 m 0.5-0.6 m 0.7-0.8 m 1.0-1.2 m encyclopedia 2 hrs CD audio 30 sec HDTV 1.6-2.4 m page 1983 1986 1989 1992 1995 1998 2001 2004 2007 2010 Year CSE477 L01 Introduction.12 Irwin&Vijay, PSU, 2002 Die Size Growth Die size grows by 14% to satisfy Moore’s Law Die size (mm) 100 P6 486 Pentium ® proc 10 386 8080 8008 4004 8086 8085 286 ~7% growth per year ~2X growth in 10 years 1 1970 CSE477 L01 Introduction.13 1980 1990 Year Courtesy, Intel 2000 2010 Irwin&Vijay, PSU, 2002 Clock Frequency Lead microprocessors frequency doubles every 2 years 10000 2X every 2 years Frequency (Mhz) 1000 P6 Pentium ® proc 100 486 10 8085 1 0.1 1970 CSE477 L01 Introduction.14 8086 286 386 8080 8008 4004 1980 1990 Year Courtesy, Intel 2000 2010 Irwin&Vijay, PSU, 2002 Power Dissipation Lead Microprocessors power continues to increase Power (Watts) 100 P6 Pentium ® proc 10 8086 286 1 8008 4004 486 386 8085 8080 0.1 1971 1974 1978 1985 1992 2000 Year Power delivery and dissipation will be prohibitive CSE477 L01 Introduction.15 Courtesy, Intel Irwin&Vijay, PSU, 2002 Power Density Power Density (W/cm2) 10000 Rocket Nozzle 1000 Nuclear Reactor 100 8086 Hot Plate 10 4004 P6 8008 8085 Pentium® proc 386 286 486 8080 1 1970 1980 1990 Year 2000 2010 Power density too high to keep junctions at low temp CSE477 L01 Introduction.16 Courtesy, Intel Irwin&Vijay, PSU, 2002 Design Productivity Trends 100,000 Logic Tr./Chip 1,000 10,000 Tr./Staff Month. 1,000 100 58%/Yr. compounded Complexity growth rate 10 100 1 10 x 0.1 xx x x 0.01 x 1 21%/Yr. compound Productivity growth rate x x Productivity (K) Trans./Staff - Mo. Logic Transistor per Chip (M) Complexity 10,000 0.1 0.01 2009 2007 2005 2003 2001 1999 1997 1995 1993 1991 1989 1987 1985 1983 1981 0.001 Complexity outpaces design productivity CSE477 L01 Introduction.17 Courtesy, ITRS Roadmap Irwin&Vijay, PSU, 2002 Technology Directions: SIA Roadmap Year Feature size (nm) Mtrans/cm2 Chip size (mm2) Signal pins/chip Clock rate (MHz) Wiring levels Power supply (V) High-perf power (W) Battery power (W) 1999 2002 2005 2008 2011 2014 180 7 170 768 600 6-7 1.8 90 1.4 130 14-26 170-214 1024 800 7-8 1.5 130 2.0 100 47 235 1024 1100 8-9 1.2 160 2.4 70 115 269 1280 1400 9 0.9 170 2.0 50 284 308 1408 1800 9-10 0.6 174 2.2 35 701 354 1472 2200 10 0.6 183 2.4 For Cost-Performance MPU (L1 on-chip SRAM cache; 32KB/1999 doubling every two years) http://www.itrs.net/ntrs/publntrs.nsf CSE477 L01 Introduction.18 Irwin&Vijay, PSU, 2002 Why Scaling? Technology shrinks by ~0.7 per generation With every generation can integrate 2x more functions on a chip; chip cost does not increase significantly Cost of a function decreases by 2x But … How to design chips with more and more functions? Design engineering population does not double every two years… Hence, a need for more efficient design methods Exploit different levels of abstraction CSE477 L01 Introduction.19 Irwin&Vijay, PSU, 2002 Design Abstraction Levels SYSTEM MODULE + GATE CIRCUIT Vin Vout DEVICE G S n+ CSE477 L01 Introduction.20 D n+ Irwin&Vijay, PSU, 2002 Major Design Challenges Microscopic issues Macroscopic issues ultra-high speeds time-to-market power dissipation and supply rail drop growing importance of interconnect noise, crosstalk design complexity (millions of gates) high levels of abstractions reuse and IP, portability reliability, manufacturability clock distribution Year Tech. Complexity 1997 1998 1999 2002 0.35 0.25 0.18 0.13 13 M Tr. 20 M Tr. 32 M Tr. 130 M Tr. CSE477 L01 Introduction.21 systems on a chip (SoC) tool interoperability Frequency 3 Yr. Design Staff Size 400 MHz 210 500 MHz 270 600 MHz 360 800 MHz 800 Staff Costs $90 M $120 M $160 M $360 M Irwin&Vijay, PSU, 2002